Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

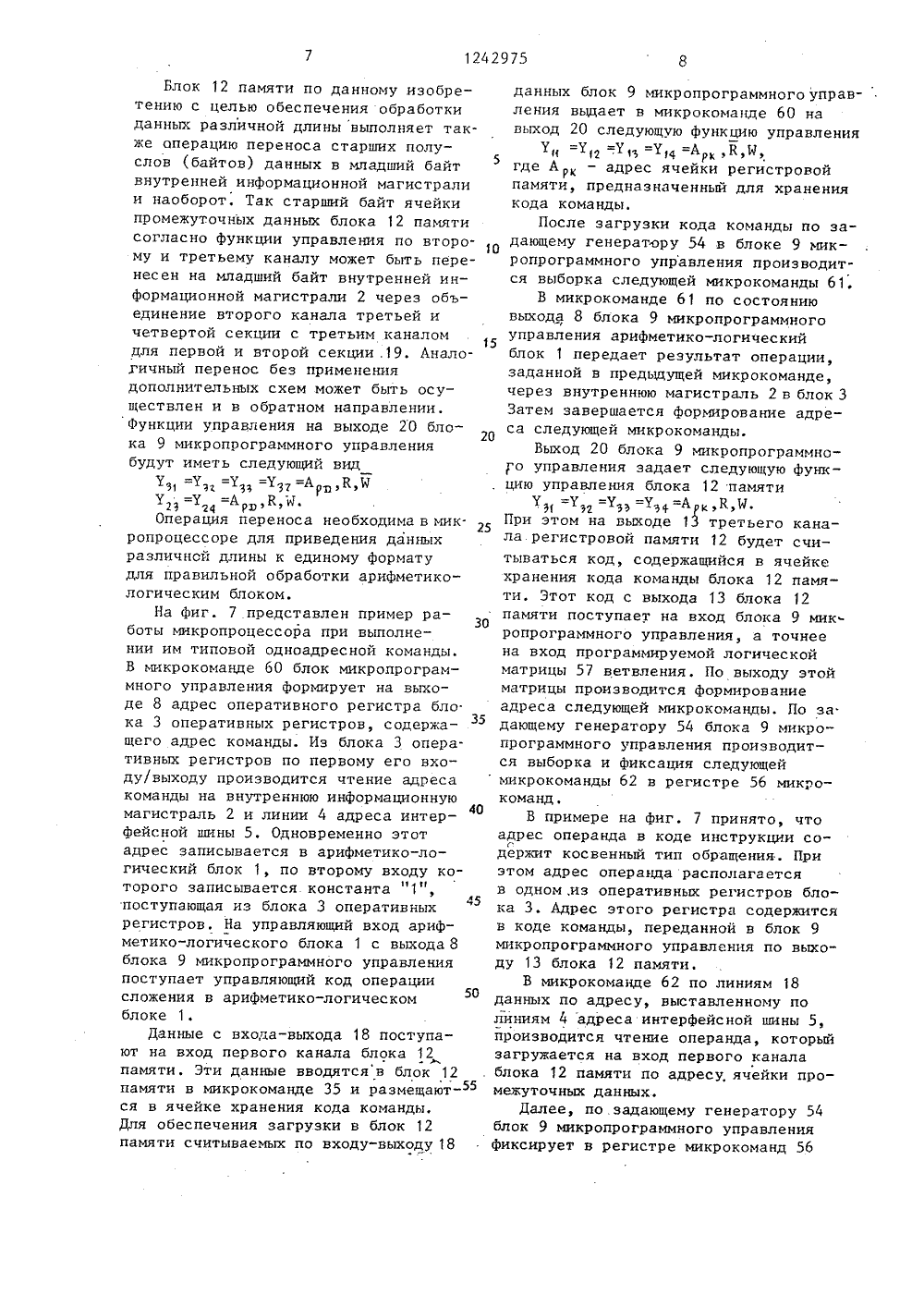

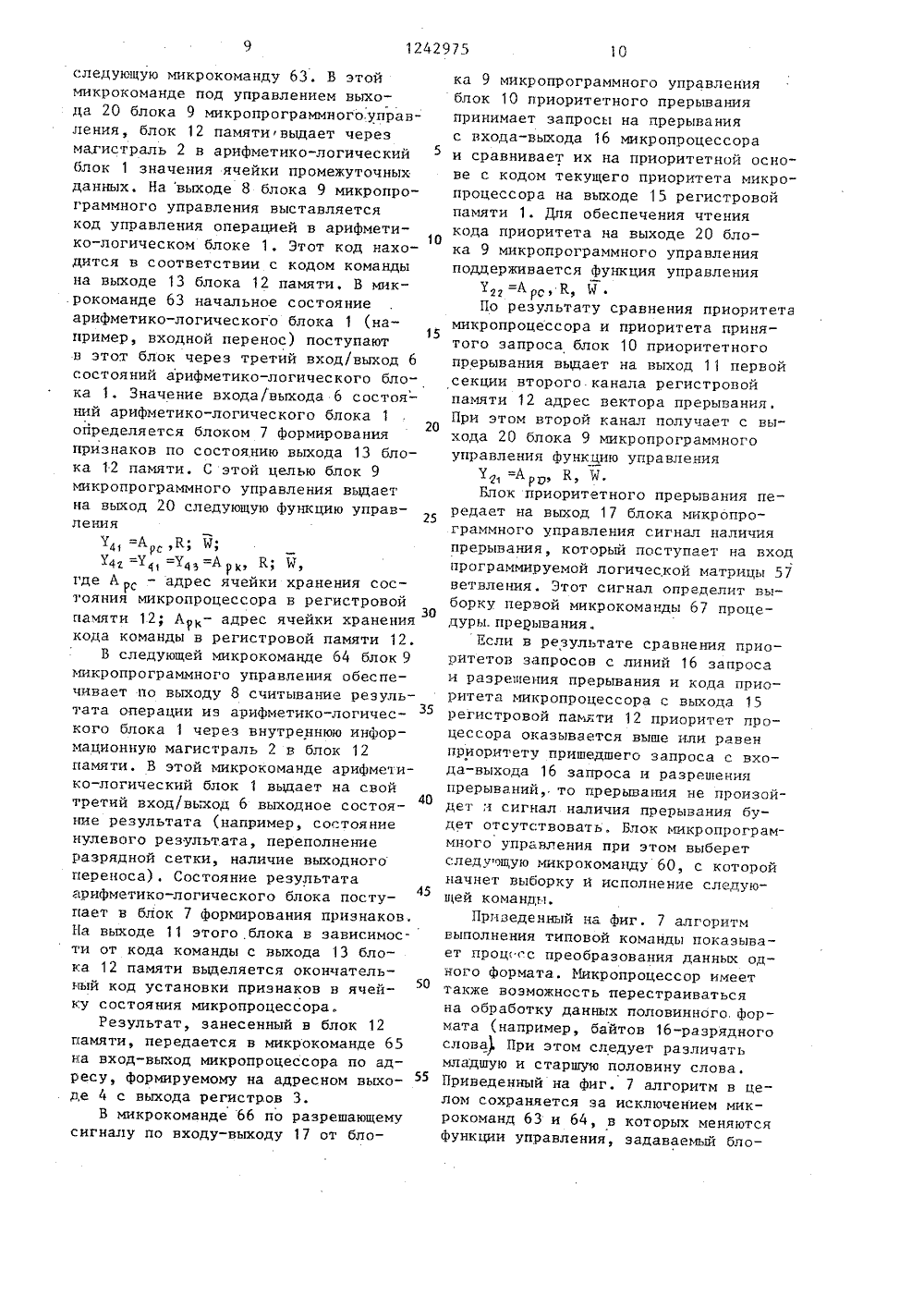

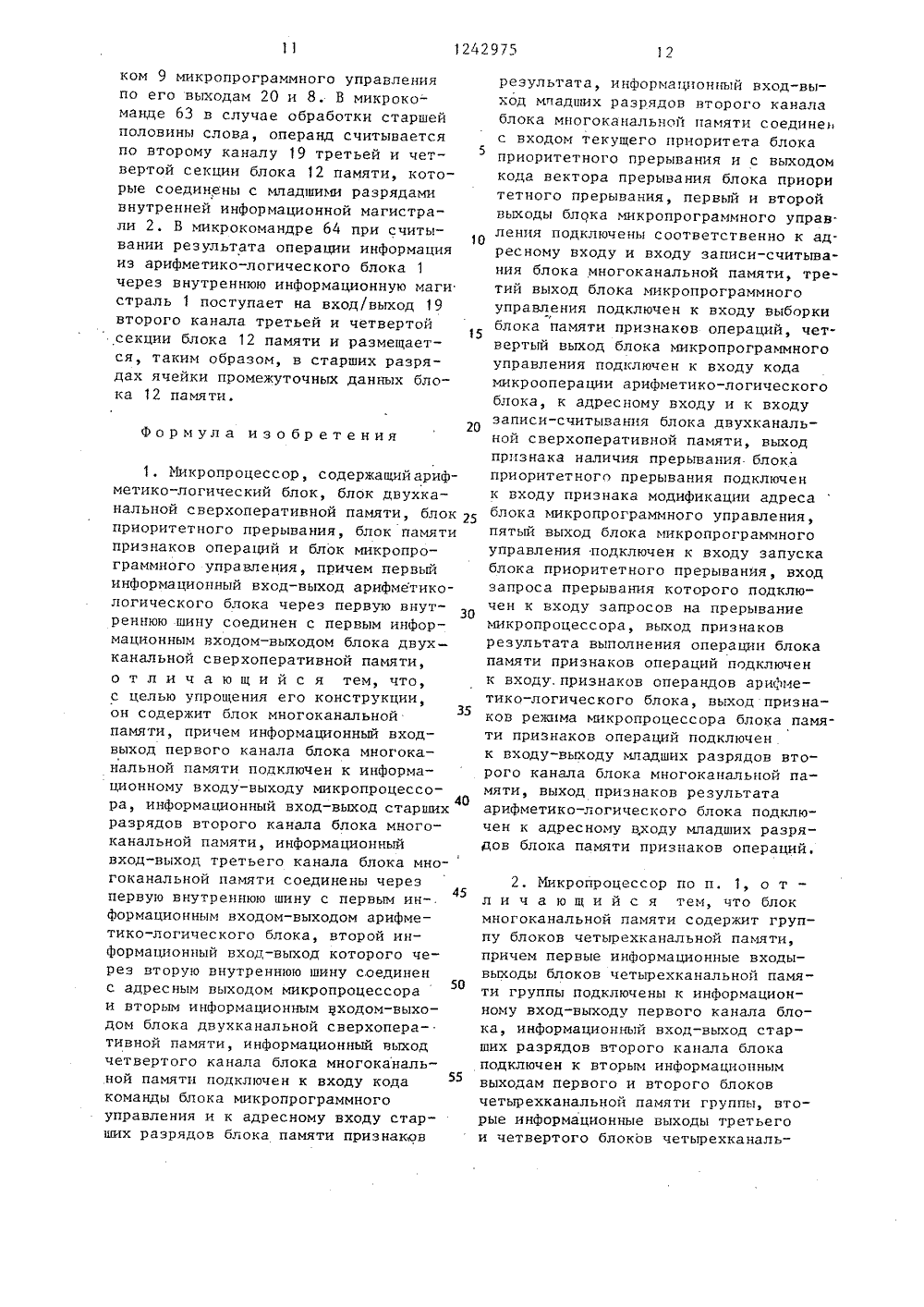

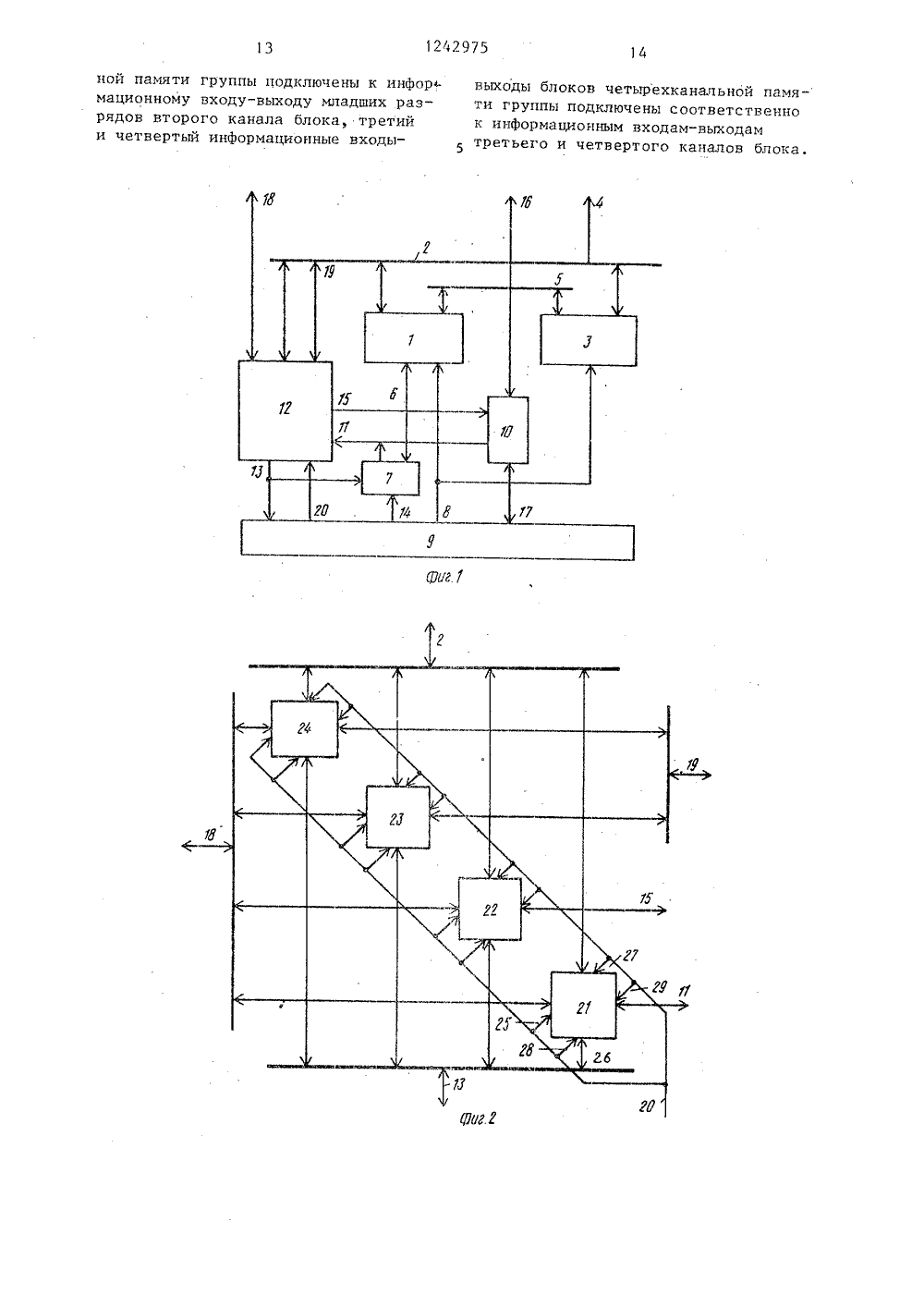

) 01) 4297 51) 4 С 06 Р 15/00 ИСАНИЕ ИЗОБРЕТЕНИЯ равтво СССР О, 1978; 01.73 СУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВ(71) Институт электронныхляющих машин(57) Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки информации. Цель изобретенияупрощение микропроцессора. Он содержит арифметико-логический блок, блок двухканальной сверхоперативной памяти, блок формирования признаков операций, блок микропрограммного управ- ления, блок многоканальной памяти и блок приоритетного прерывания. Цель изобретения достигается за счетповышения регулярности связей мехщу элементами и однородности структуры.с 1 з.п. ф-лы, 7 ил.Ю1242975 Ео Редактор В,Иван Заказ 3707ВБ 3035,ул.Проектная,зводственно-полиграфическое предприятие, г.ужг ПИ Государ о делам изМосква, Ж Пег /тавитель М.Силинред М.Ходанич Коррек раж б 71 Подписновенного комитета СССРретений и открьггий5, Раущская наб д. 4/51 1242975Изобретение относится к вычисли- вход 52 и выход 53 блока. Блок микротельной технике и может быть исполь- программного управления содержит гезовано при построении систем обработ- нератор 54 тактовых импульсов,ки информации. блок 55 памяти микрокоманд, реЦелью изобретения является упро- гистр 56, микрокоманд, программируещение микропроцессора. мую логическую матрицу 57, связи 58На фиг. 1 представлена Функциональ- и 59 между элементами блока. Арифме-ная схема микропроцессора; иа фиг, 2 . тико-логический блок может быть реаФункциональная схема блока многока- лизован на микросхеме К 1802 ВС 1,нальной памяти; на фиг. 3 - функцио О блок 7 - на К 556 РТ 1, секции 21 - 24нальная схема арифметико-логического ,на базе КР 1802 ВВ 1,блока; на фиг. 4 - блок-схема блока Каждая секция 12 многоканальнойпамяти признаков результата; на памяти содержит по крайней мере триФиг. 5 - Функциональная схема блока ячейки для запоминания данных памяти.приоритетного прерывания; на фиг. 6 - 15 Кроме того, каждая секция имеет четыфункциональная схема блока микропро- ре канала ввода/вывода данных. Каждыйграммного управления; на фиг. 7 - ап- канал разрядной секции имеет собственгоритм выполнения типовой команды ный управляющий вход 25-28, соответ-микропроцессора. ственно для первого, второго, третьеМикропроцессор содержит арифмети-. о го и четвертого каналов. Управляющийко-логический блок 1, первую внут- вход каждого канала имеет цепи адререннюю магистраль 2, блок 3 двух- са ячейки и цепь задания операцииканальной сверхоперативной памяти, (чтение, запись) по выбранному канаадресный выход 4 устройства, вторую лу. Совокупность управляющих входоввнутреннюю магистраль 5 вход-выход 6 25 для всех секций составляет управляю-.признаков состояния арифметико-логи- щий вход памяти. Совокупность входов/ческого блока, блок 7 памяти призна" выходов первых разрядных каналов кажков операций, выход 8 кода микроопе- дой секции составляет вход/выход перрации, блок 9 микропрограммного вого канала памяти.,Входы/выходыуправления, блок 10 приоритетного ЗО вторых разрядных каналов подключеныпрерывания, выход 11 вектора прерыва- к остальным узлам микропроцессорания, блок 12 многоканальной памяти,индивидуально как входы/выходы второ.входы, выходы и связи между элемен- го канала первой 11, второй 15,тами схемы микропроцессора 13 - 20. третьей и четвертой 19 секций. СовоБлок многоканальной памяти содер. купность входов/выходов третьих кажит группу блоков 21-24 четырехка- налов всех секпий составляет вход/вы 35 .нальной памяти, где 21 - секция хра- ход третьего канала, а совокупностькения младших разрядов памяти, 22- входов/выходов четвертых каналов23 - секции хранения промежуточных всех с.екций образует вход/выход четразрядов памяти, .а 24 - секция хране- вертого канала блока 12 памятиния старших разрядов памяти, управ- Микропроцессор работает следующимляющие входы 25 - 29 блока, Арифме- образом.тико-логический блок содержит ре- Работа входящих в микропроцессоргистр 30 первого операнда, регистр 31 устройств, а также их взаимодействиевторого операнда, выходы 32 и 33 между собой определяется блоком 9регистров первого и второго операн- микропрограммного управления. Заданиедов, комбинационное арифметико-логи- микропрограммы интерпретации текущейческое устройство 34, связи 35 - 38 команды осуществляется по выходу 13между элементами блока, блок 39 фор- четвертого канала блока 12 памяти,мирования признака нулевого результа- по которому в программируемую логита, входы и выходы 40 - 44 блока. ческую матрицу 57 ветвления передаетБлок памяти признаков результата реа- ся код исполняемой команды, Програмлизован на программируемойлогической мируемая логическая матрица ветвлематрице 45, в состав которой входят ния 57 по коду текущей команды формиэлементы И 46, элементы ИЛИ 47, эле- рует код адреса первой исполняемойменты НЕ 48 и трехстабильные эле- микрокоманды, Из памяти микрокоменты 49. Блок приоритетного преры- манд 55 производится выборка кодавания содержит регистр 50 запросов микрокомандь 4 который по тактовомупрерывания, схему 51 приоритета, импульсу от тактового генератора 54з 12429 инструкции, . т. е. однократно за всю микропрограмму исполнения конкретнои инструкции.Работа блока приоритетного прерывания происходит следующим образом.По входу-выходу 16 запроса на прерывания на входной регистр 50. блока 10 приоритетного прерывания поступают сигналы запросов на прерывания и фиксируются в этом регистре. Приоритетная схема 51 блока приоритетного прерывания производит комбинационный анализ поступивших запросов и текущего состояния приоритета процесссора по выходу 15 второй секции второго канала блока 12 памяти и производит выдачу сигналов разрешения прерыва - ния по входу-выходу 16, а также формирование кода разрешенного прерывания и кода по входу-выходу 17 для Фиксируется в регистре 56 микрокоманд, Выборка последующих микрокоманд осуществляется по коду адреса следую щей микрокоманды, задаваемому на выходе 59. В случае необходимости разветвления микрокоманды по выходу 58 регистра микрокоманд выдается код номера проверяемого условия ветвления, который настраивает программируемую логическую матрицу 57 ветвления на Формирование кода наложения на код адреса следующей микрокоманды по состоянию выхода 13 четвертого канала блока 12 памяти, Код наложения, вырабатываемый программируемой логической матрицей 57 ветвления, объединяется по функции ИЛИ с выходом 59 адреса следующей микрокоманды и поступает на адресный вход памяти микрокоманд 55.20Арифметико-логический блок 1 ра - ботает следующим образом.Входная информация (данные) поступает по первому выходу арифметикологического блока с информационной магистрали 2 и по второму входу/выходу из блока 3 оперативных регистров соответственно на первый 30 и второй 31 регистры входных данных арифметико-логического блока 1. Управле 30 ние загрузкой регистров 30 и 31 осуществляется по сигналам управления в цепях 41 и 42 от блока 9 микропрограммного управления по выходу 8. С выходов этих регистров данные поступают соответственно на первый 32 иЗ 5 второй 33 входы комбинационнойарифметико-логической схемы 34, Дополнительное состояние арифметико-логической схемы 34 задается по цепям входного 37 и выходного переноса 38 от40 входа/выхода 6 блока 7 формирования признаков. Настройка комбинационной арифметико-логической схемы 34 на реализацию конкретной функции осуществляется по входу 43 арифметико 45 логического блока от входа 8 блока 9 микропрограммного управления. С выхода 35 арифметико-логической схемы 9 результат ойерации поступает на первый и второй вход/выход арифметикологического блока 1 для передачи в другие узлы микропроцессора., Кроме того, этот же результат поступает на схему 39 формирования признака нуля результата. Второй выход 40 арифметико-логического блока содержит код признака переполнения результата. Значения сигналов выходного переноса 75 4по цепи 38, признака нуля результата по выходу 4 1 и признака переполнения результата по выходу 40 передаются по обобщенной цепи 6 в блок 7 Формир вания признаков.Блок 7 работает следующим образом. На вход программируемой логической матрицы 45 поступает с выхода 13 чет. вертого канала блока 12 памяти код исполняемой инструкции и код признаков состояния микропроцессора. Логическая матрица 45 вырабатывает на выходах код начального состояния ариф метико;логического блока 1 и устанавливает таким образом зависимость между прежним состоянием микропроцессора и последующим результатом исполняемой инструкции. В тоже время признаки результата исполняемой инструкции такие как выходной перенос по цепи 38, признак нуля результата по це. пи 4 1 или признак переполнения по цепи 40 также поступают с выхода арифметико-логичесКого блока 1 на вход программируемой логической матрицы 45 и, образуя произведения на схемах 46 И с кодом исполняемой инструкции по выходу 13, Формируют по второму выходу блока 7 формирования признаков новый код состояния микропроцессора, который поступает на вход 11 первой секции второго канала блока 12 памяти. Включение и работа блока 7 осуществляется по сигналу от блока 9 микропрограммного управления по его выходу 14. Включение и работа блока 7 производится на этапе вычисления результата и формирования нового состояния исполняемоймодификации адреса следующей микро- команды. Укаэанная связь. 17 блока микропрограммного управления присое,диняется к выходу программируемой логической матрицы 57 ветвления и5 участвует по функции проводного ИЛИ в формировании адреса микропрограммы обработки прерывания. Включение блока 10 приоритетного прерывания производится по его входу 52 от блока микропрограммного управления по входу-выходу 17 после каждого исполнения очередной инструкции.рассмотрим далее работу блока 12 памяти. Перед микропрограммированием процессора ячейки блока 12 памяти специфицируются однозначным образом. Например, первая ячейка назначается для хранения кода команды, вторая для хранения кода состояния микропроцессора, третья - для хранения промежуточных данных.Блок 9 микропрограммного управления по выходу 20 в каждой микрокоман де настраивает каждую разрядную секцию каждого из каналов блока 12 памяти, Для строгогоизложения описания запишем в общем виде функцию управления любого иэ каналов блока 12 памяти в виде1где У; - функция управления, подаваемая на входы 25-28 соответственно для каналов 1 - 4 (16 Ы 4) и для каждой секции 21-24 (114) блока 12 па 35 мяти, причемА - адрес ячейки памяти для 1-го11канала, 1-й секции;.К . - функция чтения по 1-му кана11 40лу и 1-й секции;М, - функция записи по -му каналу и 3-й секции.Таким образом, информация на вхо, де/выходе каждого канала может бьггь выбрана микропрограммным способом из45 отдельных разрядных частей любых ячеек блока 12 памяти, образуя на выходе канала составное данное. Так, например, на выходе 13 блока 12 памяти может бьггь образована для одновременного использования информацИи о значении старших разрядов кода исполняемой микропроцессором команды и младших разрядов ячейки блока 12 памяти, хранящей текущее состояние микропроцессора. Такое составное данное используется блоком микропрограммного управления для принятия решения о.направлении ветвления микропрограммы в зависимости от типа команды условного перехода и значения текущих признаков в текущем состоянии микропроцессора, Аналогичное составное данноеиспользуется блоком 7 Формированияпризнаков для задания на третьемвходе/выходе арифметико-логическогоблока входного состояния, которое зависит от кода команды и текущихпризнаков состояния микропроцессора. Для обеспечения работы блока 10 приоритетного прерывания блок 9 микропрограммного управления выводит из блока 12 памяти код приоритета микропроцессора в текущей инструкции исполняемой программы. При этом блоком 9 генерируется следующая функция управления вторым каналом второй секции блока 12 памятиУд =А, К,Ч,что обеспечивает чтение кода приоритета микропроцессора из ячейки Ахранения текущего состояния микропроцессора. Эта информация считывается с выхода 15 блока 12 памяти и поступает на первый вход блока 10 приоритетного прерывания, а на второй вход этого блока поступают сигналы с входов-выходов 1 б запроса и разрешения прерывания, Приоритетная схема блока 51 приоритетного прерывания производит приоритетное сравнение сигналов запроса на прерывание с текущим приоритетом микропроцессора, С этой целью каждой линии входа-выхода 16 присвоен жестко конкретный уровень приоритега, Это сравнение обычно осу - ществляется в определенной точке микропрограммы, которая выделяется выдачей блоком 9 микропрограммного управления управляющего сигнала по цепи 17.По выходу 20 блок 9 микропрограммного управления для обеспечения занесения в блок 12 памяти адреса вектора прерывания из блока приоритетного прерывания 10 по цепи 11 выдает следующую функцию управленияУ =А К,У,которая обеспечивает запись информации по входу 11 блока 12 памяти в ячейку промежуточных данных АДанная Функция управления также как и сигнал разрешения прерывания на выходе 17 блока 9 микропрограммно.го управления генерируются этим блоком в конечной микрокоманде микропрограммы интерпретации инструкции.Блок 12 памяти по данному изобретению с целью обеспечения обработки данных различной длины выполняет также операцию переноса старших полуслов (байтов) данных в младший байт внутренней информационной магистрали и наоборот. Так старший байт ячейки промежуточных данных блока 12 памяти согласно функции управления по второму и третьему каналу может быть перенесен на младший байт внутренней информационной магистрали 2 через объединение второго канала третьей и четвертой секции с третьим каналом для первой и второй секции .19. Аналогичный перенос без применения дополнительных схем может быть осуществлен и в обратном направлении. Функции управления на выходе 20 блока 9 микропрограммного управления будут иметь следующий вид1 = = =зг =А Н 1У =У =А ,К,1.Операцйя переноса необходима в микропроцессоре для приведения данных различной длины к единому формату для правильной обработки арифметикологическим блоком.На фиг. 7 представлен пример ра - боты микропроцессора при выполнении им типовой одноадресной команды. В микрокоманде 60 блок микропрограммного управления формирует на выходе 8 адрес оперативного регистра бло ка 3 оперативных регистров, содержа 35 щего адрес команды. Из блока 3 оперативных регистров по первому его входу/выходу производится чтение адреса команды на внутреннюю информационную магистраль 2 и линии 4 адреса интер 40 фейсной шины 5. Одновременно этот адрес записывается в арифметико-логический блок 1, по второму входу которого записывается константа "1",45 поступающая из блока 3 оперативных регистров, На управляющий вход арифметико-логического блока 1 с выхода 8 блока 9 микропрограммного управления поступает управляющий код операции сложения в арифметико-логическом блоке 1.Данные с входа-выхода 18 поступают на вход первого канала блока 12 памяти. Эти данные вводятся в блок 12 памяти в микрокоманде 35 и размещаются в ячейке хранения кода команды. Для обеспечения загрузки в блок 12 памяти считываемых по входу-выходу 18 данных блок 9 микропрограммного управления выдает в микрокоманде 60 навыход 20 следующую функцию управлениян ги Арк Н 1.где А ц - адрес ячейки регистровойпамяти, предназначенный для хранениякода команды.После загрузки кода команды по задающему генератору 54 в блоке 9 микропрограммного управления производится выборка следующей микрокоманды 61,В микрокоманде 61 по состояниювыхода 8 блока 9 микропрограммногоуправления арифметико-логическийблок 1 передает результат операции,зацанной в предыдущей микрокоманде,через внутреннюю магистраль 2 в блок 3Затем завершается Формирование адреса следующей микрокоманды.Выход 20 блока 9 микропрограммного управления задает следующую Функцию управления блока 12 памятии = = =з =АГк Н 1При этом на выходе 13 третьего канала регистровой памяти 12 будет считываться код, содержащийся в ячеикехранения кода команды блока 12 памяти. Этот код с выхода 13 блока 12памяти поступает на вход блока 9 микропрограммного управления, а точнеена вход программируемой логическойматрицы 57 ветвления. По выходу этойматрицы производится формированиеадреса следующей микрокоманды. По за.дающему генератору 54 блока 9 микропрограммного управления производится выборка и фиксация следующеймикрокоманды 62 в регистре 56 микрокоманд,В примере на фиг. 7 принято, чтоадрес операнда в коде инструкции содерлжт косвенный тип обращения. Приэтом адрес операнда располагаетсяв одном,из оперативных регистров блока 3. Адрес этого регистра содержитсяв коде команды, переданной в блок 9микропрограммного управления по выходу 13 блока 12 памятиВ микрокоманде 62 по линиям 18данных по адресу, выставленному полиниям 4 адреса интерфейсной шины 5,производится чтение операнда, которыйзагружается на вход первого каналаблока 12 памяти по адресу ячейки промежуточнык данных.Далее, по.задающему генератору 54блок 9 микропрограммного управленияфиксирует в регистре микрокоманд 56следующую микрокоманду 63. В этой микрокоманде под управлением выхода 20 блока 9 микропрограммного управления, блок 12 памятивьдает через магистраль 2 в арифметико-логический блок 1 значения ячейки промежуточных данных. На выходе 8 блока 9 микропрограммного управления выставляется код управления операцией в арифметиО ко-логическом блоке 1. Этот код находится в соответствии с кодом команды на выходе 13 блока 12 памяти. В мик.рокоманде 63 начальное состояние арифметико-логического блока 1 (на 15 пример, входной перенос) поступают в этот блок через третий вход/выход 6 состояний арифметико-логического блока 1. Значение входа/выхода 6 состоя- ний арифметико-логического блока 120 ойределяется блоком 7 формирования признаков по состоянию выхода 13 блока 12 памяти. С этой целью блок 9 микропрограммного управления вьдает на выход 20 следующую Функцию управ ления41=А,К; Я;41 1 ="4 з =А р кэ Р 1 1 ьгде А - адрес ячейки хранения сосрстояния микропроцессора в регистровой30 памяти 12; Ак- адрес ячейки хранения кода команды в регистровой памяти 12,В следующей микрокоманде 64 блок 9 микропрограммного управления обеспечивает по выходу 8 считывание результата операции из арифметико-логического блока 1 через внутреннюю информационную магистраль 2 в блок 12 памяти, В этой микрокоманде арифметико-логический блок 1 вьдает на свой третий вход/выход 6 вьходное состоя 40 ние результата (например, состояние нулевого результата, переполнение разрядной сетки, наличие выходного переноса)Состояние результата арифметико-логического блока посту 45 пает в блок 7 Формирования признаков. На выходе 11 этого блока в зависимости от кода команды с выхода 13 бло - ка 12 памяти вьделяется окончательный код установки признаков в ячей 50ку состояния микропроцессора.Результат, занесенный в блок 12 памяти, передается в микрокоманде 65на вход-выход микропроцессора по адресу, формируемому на адресном выходе 4 с выхода регистров 3.В микрокоманде 66 по разрешающему сигналу по входу-выходу 17 от блока 9 микропрограммного управления блок 10 приоритетного прерывания принимает запросы на прерывания с входа-выхода 16 микропроцессора и сравнивает их на приоритетной основе с кодом текущего приоритета микропроцессора на выходе 15 регистровой памяти 1. Для обеспечения чтения кода приоритета на выходе 20 блока 9 микропрограммного управления поддерживается Функция управленияУ =Асс, В., ЙПо результату сравнения приоритета микропроцессора и приоритета принятого запроса блок 10 приоритетного прерывания выдает на выход 11 первой секции второго. канала регистровой памяти 12 адрес вектора прерывания. При этом второй канал получает с выхода 20 блока 9 микропрограммного управления Функцию управления1 =АР 7 фБлок приоритетного прерывания передает на выход 17 блока микропрограммного управления сигнал наличия прерывания, который поступает на вход программируемой логической матрицы 57 ветвления. Этот сигнал определит выборку первой микрокоманды 67 процедуры, прерыванияЕсли в результате сравнения приоритетов запросов с линий 16 запроса и разрешения прерывания и кода приоритета микропроцессора с выхода 15 регистровой памяти 12 приоритет процессора оказывается выше или равенприоритету пришедшего запроса с входа-выхода 16 запроса и разрешенияпрерываний, то прерывания не произойдет и сигнал наличия прерывания будет отсутствовать. Блок микропрограммного управления при этом выберетследующую микрокоманду 60, с которойначнет выборку И исполнение следующей команды.Приведенный на Фиг. 7 алгоритмвыполнения типовой команды показывает процос преобразования данных одного формата. Иикропроцессор имееттакже возможность перестраиватьсяна обработку данных половинного, формата (например, байтов 16-разрядногослова/. При этом следует различатьмладшую и старшую половину слова.Приведенный на фиг, 7 алгоритм в целом сохраняется эа исключением микрокоманд 63 и 64, в которых меняются функции управления, задаваемый бло 1242975 1210 15 20 ком 9 микропрограммного управленияпо его выходам 20 и 8. В микрокоманде 63 в случае обработки старшейполовины слова, операнд считываетсяпо второму каналу 19 третьей и четвертой секции блока 12 памяти, которые соединены с младшими разрядамивнутренней информационной магистрали 2. В микрокомандре 64 при считывании результата операции информацияиз арифметико-логического блока 1через внутреннюю информационную магистраль 1 поступает на вход/выход 19второго канала третьей и четвертойсекции блока 12 памяти и размещается, таким образом, в старших разрядах ячейки промежуточных данных блока 12 памяти. Формула изобретения 1. Микропроцессор, содержащийарифметико-логический блок, блок двухканальной сверхоперативной памяти, блок 25 приоритетного прерывания, блок памяти признаков операций и блок микропрограммного управления, причем первый информационный вход-выход арифметикологического блока через первую внутреннюю шину соединен с первым информационным входом-выходом блока двухканальной сверхоперативной памяти, о т л и ч а ю щ и й с я тем, что, с целью упрощения его конструкции, он содержит блок многоканальнойпамяти, причем информационный вход- выход первого канала блока многоканальной памяти подключен к информационному входу-выходу микропроцессора, информационный вход-выход старших40 разрядов второго канала блока многоканальной памяти, информационный вход-выход третьего канала блока мно-гоканальной памяти соединены через первую внутреннюю шину с первым ин-.45 Формационным входом-выходом арифметико-логического блока, второй инФормационный вход-выход которого через вторую внутреннюю шину соединен с адресным выходом микропроцессора50 и вторым информационным входом-выходом блока двухканальной сверхоперативной памяти, информационный выход четвертого канала блока многоканальной памяти подключен к входу кода команды блока микропрограммногоуправления и к адресному входу старших разрядов блока памяти признаков результата, информационный вход-выход мпадцях разрядов второго каналаблока многоканальной памяти соединенс входом текущего приоритета блокаприоритетного прерывания и с выходомкода вектора прерывания блока приоритетного прерывания, первый и второйвыходы блока микропрограммного управ.ления подключены соответственно к адресному входу и входу записи-считывания блока многоканальной памяти, третий выход блока микропрограммногоуправления подключен к входу выборкиблока памяти признаков операций, четвертый выход блока микропрограммногоуправления подключен к входу кодамикрооперации арифметико-логическогоблока, к адресному входу и к входузаписи-считывания блока двухканальной сверхоперативной памяти, выходпризнака наличия прерывания блокаприоритетного прерывания подключенк входу признака модификации адресаблока микропрограммного управления,пятый выход блока микропрограммногоуправления подключен к входу запускаблока приоритетного прерывания, входзапроса прерывания которого подключен к входу запросов на прерываниемикропроцессора, выход признаковрезультата выполнения операции блокапамяти признаков операций подключенк входу, признаков операндов арифметико-логического блока, выход признаков режима микропроцессора блока памяти признаков операций подключенк входу-выходу младших разрядов второго канала блока многоканальной памяти, выход признаков результатаарифметико-логического блока подключен к адресному входу младших разрядов блока памяти признаков операций. 2. Микропроцессор по п. 1, о т л и ч а ю щ и й с я тем, что блок многоканальной памяти содержит группу блоков четырехканальной памяти, причем первые информационные входы- выходы блоков четырехканальной памяти группы подключены к информационному вход-выходу первого канала бло - ка, информационный вход-выход старших разрядов второго канала блока подключен к вторым информационным выходам первого и второго блоков четырехканальной памяти группы, вторые информационные выходы третьего и четвертого блоков четырехканаль 13 1242975ной памяти группы подключены к инфор.мационному входу-выходу младших разрядов второго канала блока, третийи четвертый информационные входывыходы блоков четырехканальной памяти группы подключены соответственнок информационным входам-выходамтретьего и четвертого каналов блока,

СмотретьЗаявка

3774991, 25.07.1984

ИНСТИТУТ ЭЛЕКТРОННЫХ УПРАВЛЯЮЩИХ МАШИН

ГРОМОВ ВЛАДИМИР СЕРГЕЕВИЧ, ЗАХАРОВ ВИКТОР ГЕОРГИЕВИЧ, ПАНФЕРОВ БОРИС ИВАНОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессор

Опубликовано: 07.07.1986

Код ссылки

<a href="https://patents.su/10-1242975-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Устройство для сопряжения электронно-вычислительной машины с общей магистралью вычислительной системы

Следующий патент: Микропроцессорная система с контролем

Случайный патент: Прибор для письма обычным шрифтом, предназначаемый для слепых