Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1030801

Авторы: Благодарный, Плахтеев, Тимонькин, Ткаченко, Харченко

Текст

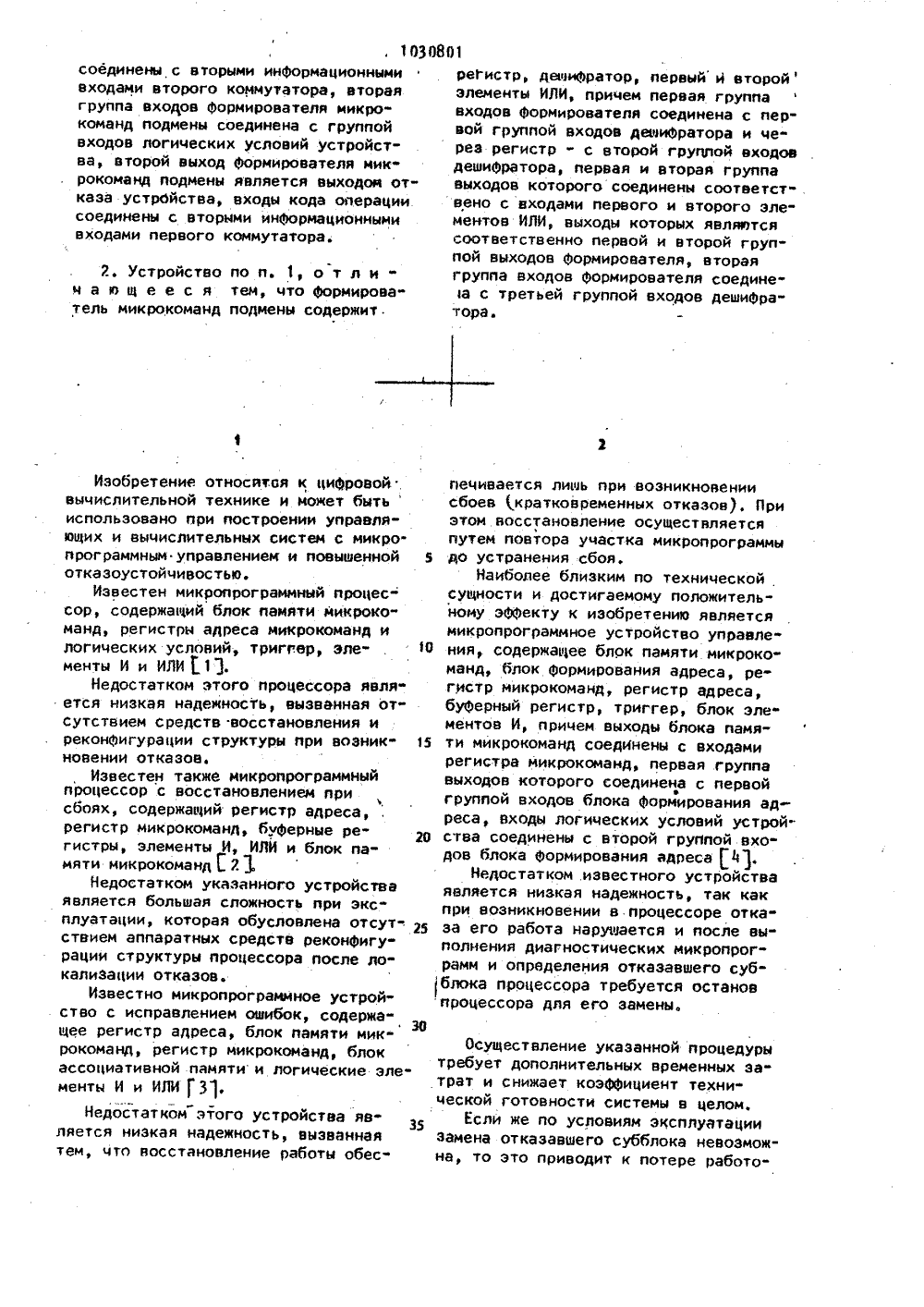

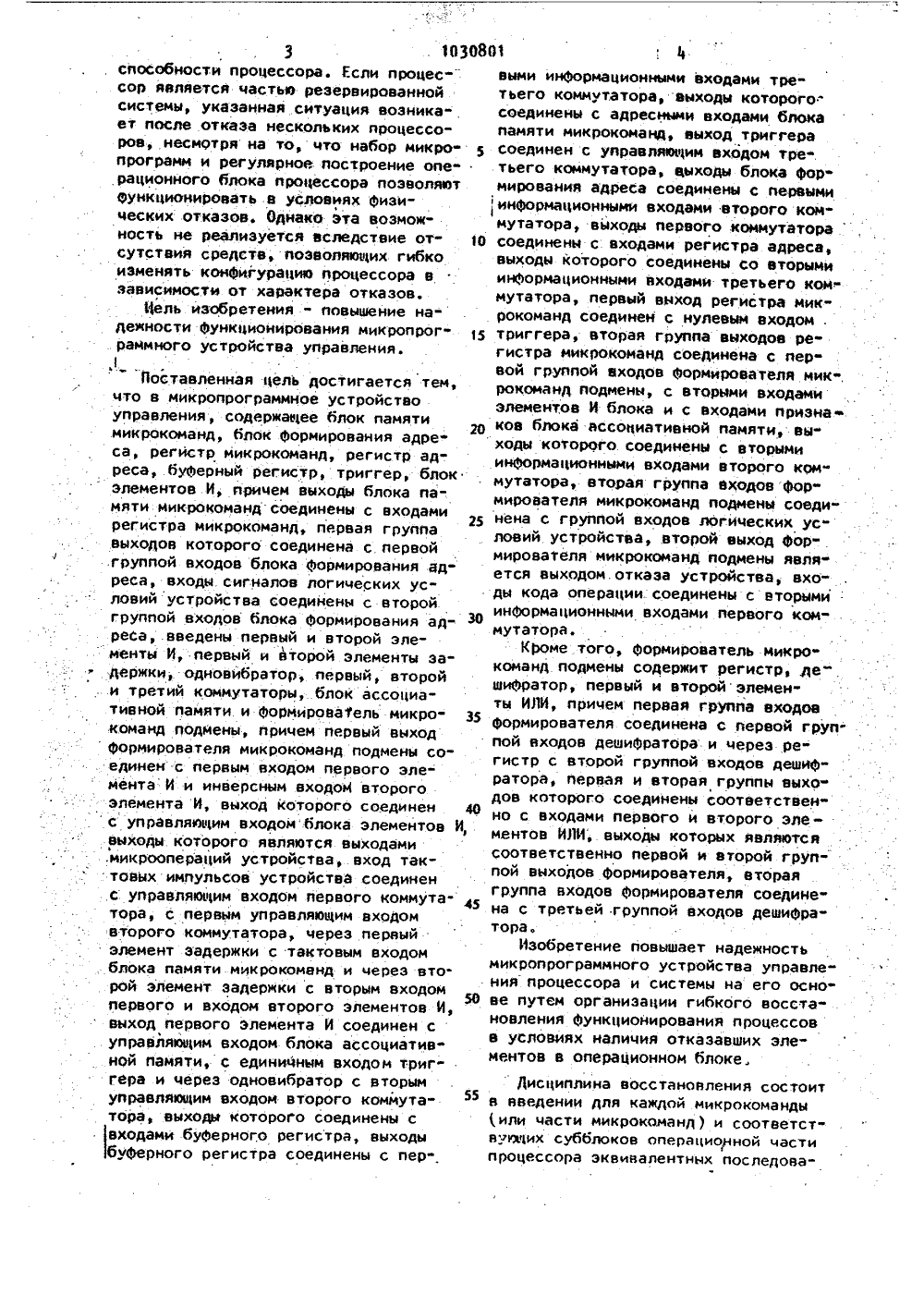

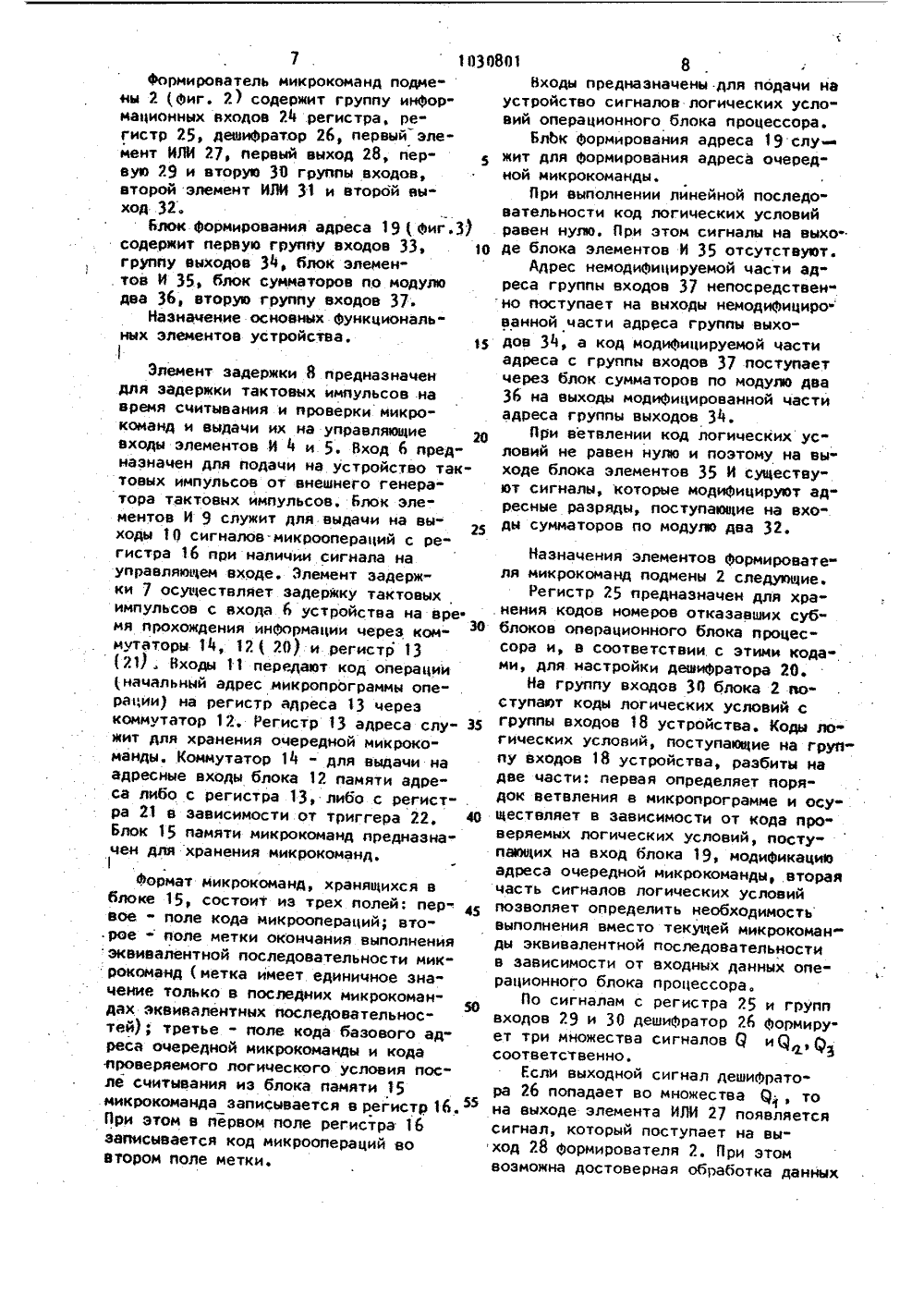

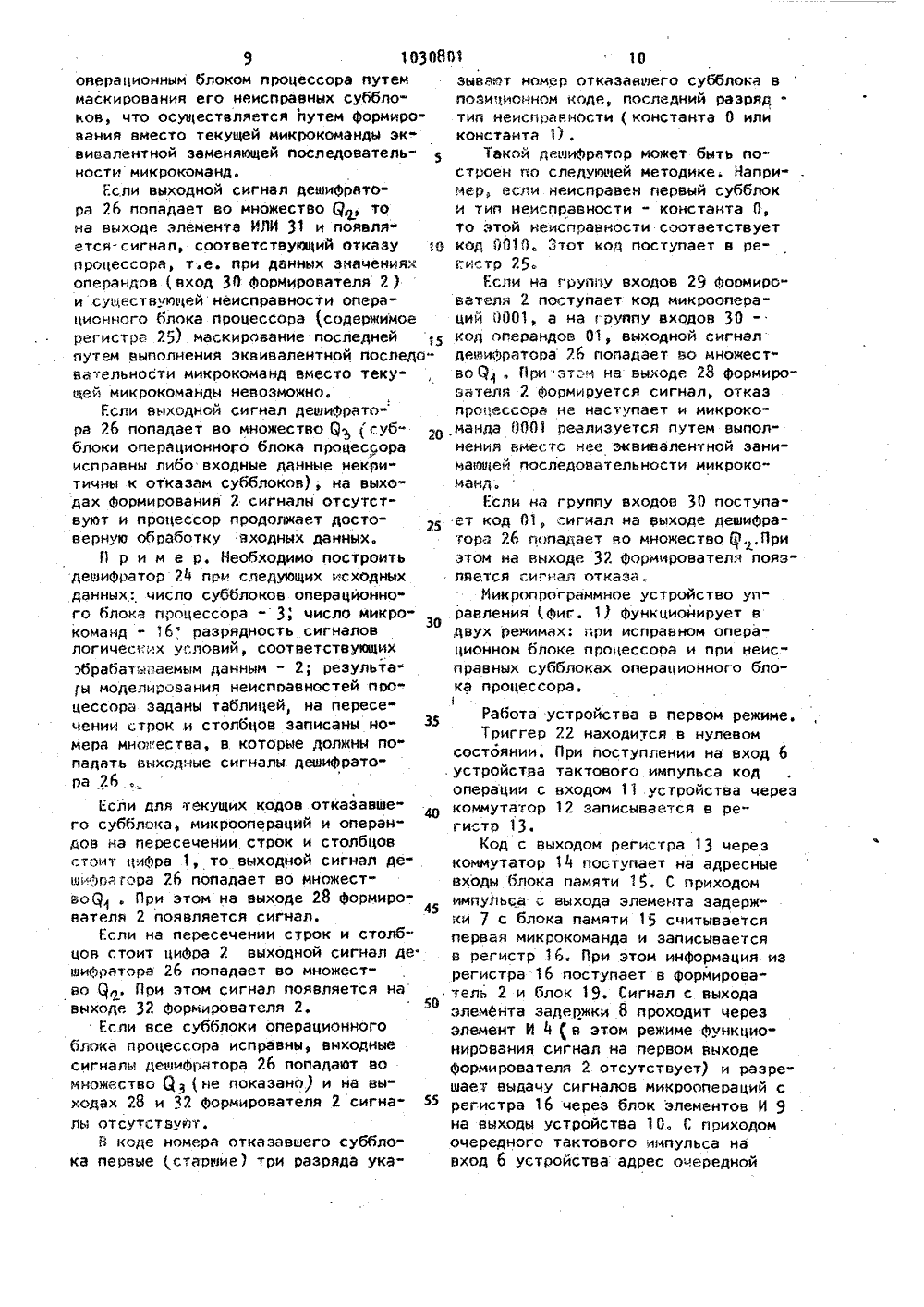

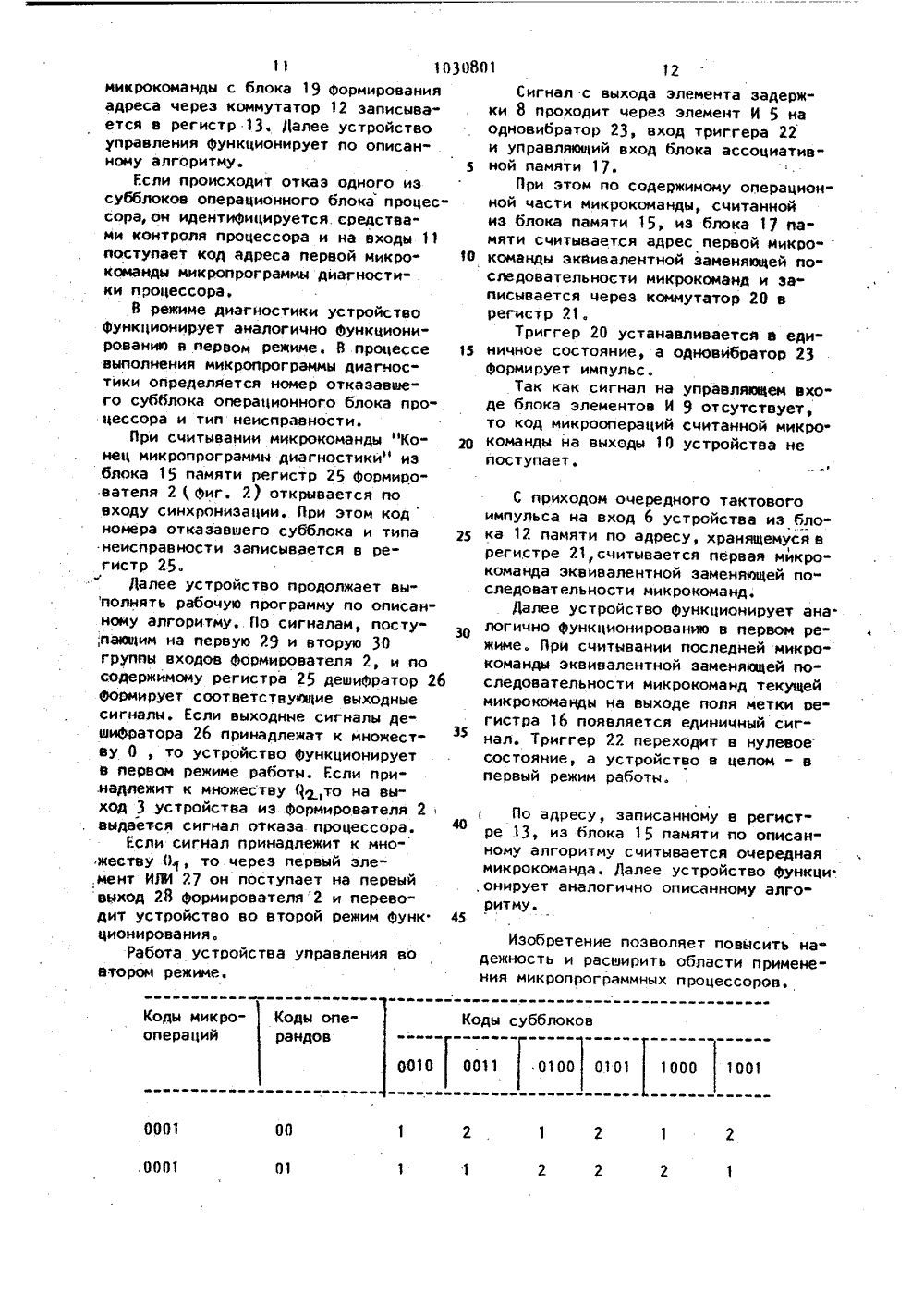

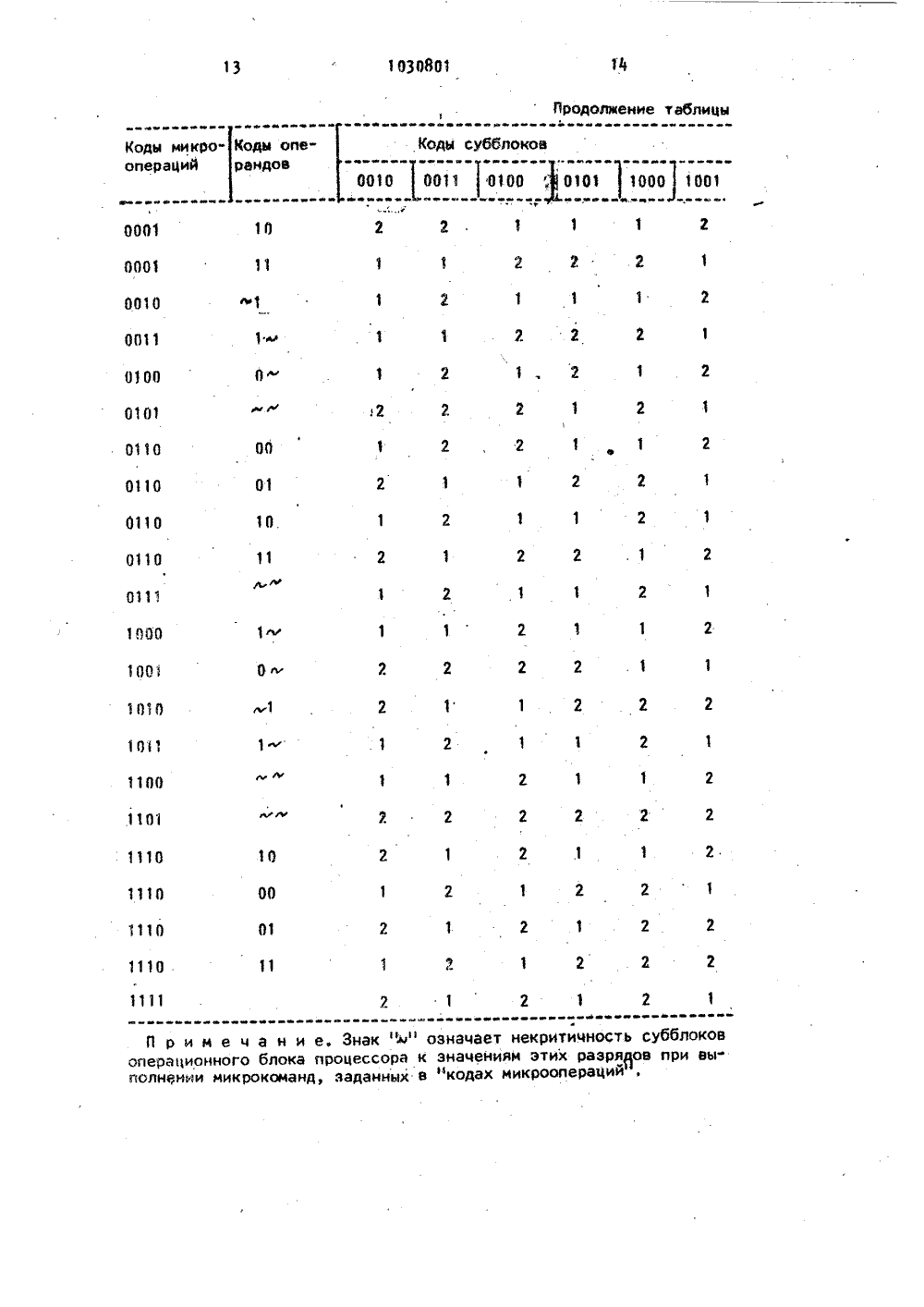

:. л.й 1 ГОСУД АРСТВЕКНИИ ДЕЛАМ ИЗОБРЕ ОПИ ИЕ ИЗОБРЕТЕНИЯ СВИДЕТЕЛЬСТВ ВТОРСИ хтеевькин по(56) 3. Авторское свидетельство СССЮ 709152, кл. С 06 Г 15/00, 1978.2, Авторское свидетельство СССРпо заявке Ю 2769466/18-24,кл. Г 06 Р, 3978.3. Авторское свидетельство СССРИ 741257, кл. 0 06 Г 11/00, 3978.4, Авторское свидетельство СССРзаявке Р" 2640038/18-24;й 06 Г 11/00. 1978 (прототип).(54)(57) 3. ИИКРОПРОГРАИИНОГ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блокпамяти микрокоманд, блок Формирования адреса, регистр микрокоманд, ре"гистр адреса, буФерный регистр, триггер, блок элементов И, причем выходыблока памяти микрокоманд соединеныс входами регистра микрокоманд, первая группа выходов которого соединенас первой группой входов блока Формирования адреса, входы сигналов логических условий устройства соединеныс второй группой входов блока Формирования адреса, о т л и ч а ю щ ее с я тем, что, с целью повышения достоверности, в него введены первыйи второй элементы И, первый и второй.элемейты задержки, одновибратор, первый, второй и третий коммутаторы,блок ассоциативной памяти и Формирователь микрокоманд подмены, причемпервый выход Формирователя микрокомандподмены соединен с первым входом первого элемента И и инверсным входом второго элемента И, выход которого со- единен с управляющим входом блока эле" ментов И, выходы которого являются выходами микроопераций устройства вход тактовых импульсов устройства со" единен с управляющим входом первого коммутатора, с первым управляющим входом второго коммутатора, через. первый элемент задержки с тактовым вхо" дом блока памяти микрокоманд и через второй элемент задержки " с вторым входом первого и входом второго элементов И, выход первого элемента И соединен с управляющим входом блока ассоциативной памяти, с. единичным вхо" дом триггера и через одновибратор - Е с вторым управляющим входом второго коммутатора, выходы которого соединены .с входами буФерного регистра, вы" ходы буФерного регистра соединены с первыми инФормационными входами тре- Я тьего коммутатора, выходы которого соединены.с адресными входами блока памяти микрокоманд, выход триггера соединен с управляющим входом третьего коммутатора, выходы блока Формирования адреса - с первыми ин" Формационными входами второго комму"татора, выходы первого коммутатора -с входами регистра адреса, выходы ; которого соединены с вторыми инФормационными входами третьего коммутато"ра, первый выход регистра микрокомандсоединен с чулевым входом триггера, вторая группа выходов регистра микро" команд соединена с первой группойвходов Формирователя микрокоманд подмены, с вторыми входами элементов И блока и с входами признаков блока ассоциативной памяти, выходы которого1030801 ФигЗ И. Сигагель ов Рел,.Зак ул, Проектн Составительктоо Н. Джуган Техоец И. Герд 5;1 / 9 тираж 70ВНИИПИ Государственнпо делам йзобретеФилиал ППП "Патент", г. го комиий и отушскаяжгород,(орректорй 3, Макаренко Подписноеета СССРрытийаб. д. 4/5ая, рр1030801 реГистр, дечиФратор, первый Ч второйэлементы ИЛИ, причем первая группавходов Формирователя соединена с первой группой входов девиФратора и через регистр - с второй группой входовдешиФратора, первая и вторая группа соединены с вторыми инФормационными входами второго коммутатора, вторая группа входов Формирователя микро- команд подмены соединена с группой входов логических условий устройства, второй выход Формирователя микрокоманд подмены является выходом от" выходов которого соединены соответст" каза устройства, входы кода операции вено с входами первого и второго элементов ИЛИ, выходы которых являются соединены с вторыми инФормационными соответственно первой и второй группой выходов Формирователя, втораягруппа входов Формирователя соединена с третьей группой входов дешиФратора. входами первого коммутатора. 2. устройство по и. 1, о т л им а ю щ е е с я тем, что Формирова" тель микрокоманд подмены содержит. Осуществление укаэанной процедуры требует дополнительных временных эа" трат и снижает коэФФициент технической готовности системы в целом.Если же по условиям эксплуатации замена отказавшего субблока невозможна, то это приводит к потере работоИзобретение относится к циФровой вычислительной технике и может бытьиспользовано при построении управля" ющих и вычислительных систем с микро. программным управлением и повышеннойотказоустойчивостью.Известен микропрограммный процес- сор, содержащий блок памяти микроко" манд, регистры адреса микрокоманд и логических условий, триггер, элементы И и ИЛИ1 1.Недостатком этого процессора явля" ется низкая надежность, вызванная от" сутствием средств восстановления и реконФигурации структуры при возник новении отказов.Известен также микропрограммный процессор с восстановлением при сбоях, содержащий регистр адреса, , регистр микрокоманд, буФерные ре" гистры, элементы И, ИЛИ и блок памяти микрокоманд2 .Недостатком указанного устройства является большая сложность при эксплуатации, которая обусловлена отсут"ствием аппаратных средств реконФигурации структуры процессора после локализации отказов.Известно микропрограммное устрой" ство с исправлением ошибок, содержа" щее регистр адреса, блок памяти мик" рокоманд, регистр микрокоманд, блок ассоциативной памяти и логические эле" енты " и ИЛИ 31Недостатком этого устройства является низкая надежность, вызванная тем, что восстановление работы обеспечивается лищь при возникновениисбоев кратковременных отказов). Приэтом. восстановление осуществляетсяпутем повтора участка микропрограммыдо устранения сбоя.Наиболее близким по техническойсущности и достигаемому положительному эФФекту к изобретению являетсямикропрограммное устройство управления, содержащее блок памяти.микрокоманд, блок Формирования адреса, регистр микрокоманд, регистр адреса,буФерный регистр, триггер, блок эле"ментов И, причем выходы блока памяти микрокоманд соедйнены с входамирегистра микрокоманд, первая группавыходов которого соединена с первойгруппой входов блока Формирования адреса, входы логических условий устройства соединены с второй группой входов блока Формирования адреса 4.Недостатком .известного устройстваявляется низкая надежность, так какпри возникновении в процессоре отказа его работа нарувается и после вы"полнения диагностических микропрограмм и определения отказавшего субблока процессора требуется остановпроцессора для его замены,0803 10 15 25 30 35 40 ) 45 55 3 103 способности процессора. Если процес- сор является частью резервированной системы, указанная ситуация возникает после отказа нескольких процессоров, несмотря на то, что набор микропрограмм и регулярное построение операционного блока процессора позволяютФунйционировать в условиях Физических отказов. Однако эта возможность не реализуется вследствие от"сутствия средств, позволяющих гибкоизменять конФигурацию процессора взависимости от характера отказов.Цель изобретения - повышение надежности Функционирования микропрограммного устройства управления. ЬПоставленная цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти .микрокоманд, блок Формирования адреса, регистр микрокоманд, регистр адреса, буФерный регистр, триггер, блок элементов И, причем выходы блока памяти микрокоманд соединены с входамирегистра микрокоманд, первая группавыходов которого соединена с. первой группой входов блока Формирования ад"реса, входы. сигналов логических условий устройства соединены с второйгруппой входов блока Формирования адреса,.введены первый и второй элементы И, первый и второй элементы задержки,. одновйбратор, первый, второй .и третий коммутаторы,.блок ассоциативной памяти и Фориирователь микрокоманд подмены, причем первый выходФормирователя микрокоманд подмены соединен -с первым входом первого элемента И и инверсным входом второго элемента И, выход которого соединенс управляющим входом блока элементов Ивыходы которого являются выходами ,микроопераций устройства, вход тактовых импульсов устройства соединен .с управляющим входом первого коммутатора, с первым управляющим входом второго коммутатора, через первый элемент задержки с тактовым входом блока памяти микрокомвнд и через второй элемент задержки с вторым входом первого и входом второго элементов И, выход первого элемента И соединен с . управляющим входом блока ассоциатив" ной памяти, с единичным входом триггера и через одновибратор с вторым управляющим входом второго коммутатора, выходы которого соединены свходами буФерного регистра, выходыбуФерного регистра соединены с первыми инФормационными входами третьего коммутатора, выходы которогосоединены с адресными входами блокапамяти микрокоманд, выход триггерасоединен с управляющим входом тре-.тьего коммутатора, аыходы блока Формирования адреса соединены с первыми ,инФормационными входами второго коммутатора, выходы первого .коммутатора .соединены с входами регистра адреса,выходы которого соединены со вторымиинФормационными входами третьего ком"мутатора, первый выход регистра мик" рокоманд соединен с нулевым входом . триггера, вторая группа выходов регистра микрокоманд соединена с пер" вой группой входов Формирователя микрокоманд подмены, с вторыми входами элементов И блока и с входами призна20 ков блока ассоциативной памяти, выходы которого соединены с вторымиинФормациониыми входами второго ком" мутатора, вторая группа входов Фор" мирователя микрокоманд подмены соеди"иена с группой входов логйческих ус"ловий устройства, второй выход Формирователя микрокоманд подмены является выходом отказа устройства, входы кода операции соединены с вторыми: инФормационными входами первого коммутатора.Кроме того, Формирователь микро- команд подмены содержит регистр, де-. шиФратор, первый и второй элементы ИПИ, причем первая группа входов Формирователя соединена с первой груп. пой входов дешиФратора и через ре" гистр с второй группой входов дешиф" ратора, первая и вторая группы выходов которого соединены соответственно с входами первого и второго элементов ИПИ, выходы которых явлются соответственно первой и второй группой выходов Формирователя, вторая группа входов Формирователя соединена с третьей .группой входов дешиФра" тора.Изобретение повышает надежность микропрограммного устройства управле" ния процессора и системы на его осно 50 ве путем органиэации гибкого восстановления Функционирования процессовв условиях наличия отказавших эле" ментов в операционном блоке, Дисциплина восстановления состоит в введении для каждой микрокоманды или части микрокоманд ) и соответствующих субблоков операционной части процессора эквивалентных последова1 0308 тельностей .микрокоманд, которые позволяют выполнить "отказавшую" микрокоманду обойти - отказавший субблок,в хранении в блоке ассоциативной памяти начальных адресов эквивалентных 5последовательностей микрокоманд, чтопозволяет уменьшить объем средстввосстановления и гибко его инициировать, а также в инициировании проце"дуры восстановления в зависимости от Оисходных данных, поступающих в операционный блок процессора, дает воэ".можность продолжать раЬоту в,условияхналичия отказавших субблоков, не про-,изводя реконфигурации структуры про"цессора и не снижая его производи"тельности.Введение блока ассоциативной памяти и обусловленных ими связей позволя.ет хранить информацию о начальных ад- щ 0ресах эквивалентных заменяющих последовательностей и считывать их при поступлении соответствующих ассоциатив"ных признаков " кодов микрокоманд иуправляющего сигнала. 25Введение формирователя микрокомандподмены и о 1 условленных им связей позволяет осуществлять выработку управ"ляющего сигнала, инициирующего в за"Висимости от кода отказавшего сусло 30ка, и значений логических условий,в том числе и логических. условий, учи.тывающих характер входных данных, выполнение вместо текущей микрокоманды эквивалентной последовательностимикрокоманд, а также не вырабатыватьуправляющий сигнал, если входные данные не критичны к отказавшему суб"блоку, и вырабатывать сигнал отказапроцессора при невозможности маски"рования отказавшего субблока,ЬВведение второго элемента И иобусловленных им связей позволяет формировать. управляющий сигнал для выдачи сигналов микроопераций с второйгруппы выходов регистра микрокомандчерез первый блок элементов И на выходы микроопераций устрОйства,Введение первого элемента И иобусловленных им связей позволяетформировать управляющий сигнал дляблока ассоциативной памяти, единично"го входа триггера и одновибратора.Введение пеового элемента задержкии обусловленных им связей позволяет 5задерживать тактовый импульс на управ"ляющем входе блока памяти микрокоманд,на время записи адреса очередной 01 Фмикрокоманды в регистр адреса либо ебуферный регистр.Введение первого коммутатора иобусловленных им связей позволяетпередавать в регистр адреса адрес очередной микрокоманды либо с входомкода операции устройства, либо с вы"ходом блока формирования адреса.Введение второго коммутатора иобусловленных им связей позволяетпередавать в буферный регистр код ад реса либо с блока Формирования адре"са, либо с блока ассоциативной памяти,Введение третьего коммутатора иобусловленных им связей позволяетпередавать адрес очередной микрокоманды на вход блока памяти адресныхмикрокоманд либо с регистра адреса,либо с Ьуферного регистра.Введение второго элемента задержки и обусловленных им связей позволя"ет задерживать тактовый импульс навремя считывания микрокоманды из блока памяти микрокоманд и проверки сигналов микроопераций в формирователемикрокоманд подмены. Введение одновибратора и обуслов"ленных им связей позволяет формировать сигнал запрета на управляющиевходы второго коммутатора на времявыполнения первой микрокоманды иэ эк"вивалентной заменяющей последователь"ности микрокоманд.На фиг, 1 представлена функциональ.ная схема устройства, на фиг. 2 функциональная схема Формирователямикрокоманд подмены, на Фиг. 3 - Функциональная схема блока формированияадреса.Микропрограммное устройство управления содержитфиг. 1 ) вторую груп"пу входов формирователя 1, формирова.тель 2, выход сигнала отказа устрой"ства 3, второй 4 и первый 5 элементы И, выход тактовых импульсов 6,первый 7 и второй 8 элементы задержки, блок элементов И 9, выходы микроопераций 10, группу входов кода опе"рации 11, первый коммутатор 12, регистр адреса 13, третий коммутатор 14блок памяти микрокоманд 15, регистр 16микрокоманд, блок 17 ассоциативнойпамяти, группу входов 18 сигналов логических условий, блок 19 формирования адреса 19, второй коммутатор 20,буферный регистр 21, триггер 22 иодновибратор 23,1 озо 8 о 7Формирователь микрокоманд подмены 2 Фиг. 2) содержит группу инФор" мационных входов 24 регистра, регистр 25, девиФратор 26, первый элемент ИЛИ 27, первый выход 28, пер" вую 29 и вторую 30 группы входов, второй элемент ИЛИ 31 и второй выход 32.Блок Формирования адреса 19Фиг.3) содержит первую группу входов 33, о группу выходов 34, блок элемен. тов И 35, блок сумматоров по модулю два 36, вторую группу входов 37.Назначение основных Функциональных элементов устройства.5Элемент задержки 8 предназначен для задержки тактовых импульсов на время считывания и проверки микрокоианд и выдачи их на управляющие входы элементов И 4 и 5. Вход 6 предназначен для подачи на устройство тактовых импульсов от внешнего генератора тактовых импульсов. Блок элементов И 9 служит для выдачи на выходы 10 сигналов-микроопераций с ре"25 гистра 16 при наличии сигнала на управляющем входе. Элемент задерж" ки 7 осуществляет задержку тактовых импульсов с входа 6 устройства на вре мя прохождения инФормации через коммутаторы 14, 12 ( 20) и .регистр 13 (21) . Входы 11 передают код операцииначальный адрес микропрограммы опе" рации) на регистр адреса 13 через коммутатор 12. Регистр 13 адреса слу жит для хранения очередной микрокоманды. Коммутатор 14 - для выдачи на адресные входы блока 12 памяти адре" са либо с регистра 13, либо с регист- . ра 21 в зависимости от триггера 22. 4 О Блок 15 памяти микрокоманд предназначен для хранения микрокоманд.Формат микрокоманд, хранящихся в блоке 15, состоит из трех полей: пер"45 вое " поле кода микроопераций; второе - поле метки окончания выполнения эквивалентной последовательности микрокоманд (метка имеет единичное значение только в последних микрокомандах эквивалентных последовательнос"Ю тей); третье " поле кода базового ад" реса очередной микрокоманды и кода проверяемого логического условия после считывания из блока памяти 15 микрокоманда записывается в регистр 16. 55 При этом в первом поле регистра 16 записывается код микроопераций ео втором поле метки. 8Входы предназначены для подачи на устройство сигналов логических условий операционного блока процессора.БлЬк Формирования адреса 19 служит для Формирования адреса очередной микрокомдндыеПри выполнении линейной последо" вательности код логических условий равен нулю. При этом сигналы на выхо-. де блока элементов И 35 отсутствуют.Адрес немодиФицируемой части ад" реса группы входов 37 непосредствен" но поступает на выходы немодиФициро. ванной части адреса группы выходов 34, а код модиФицируемой части адреса с группы входов 37 поступает через блок сумматоров по модулю два 36 на выходы модиФицированной части адреса группы выходов 34.При ветвлении код логических условий не равен нулю и поэтому на вы" ходе блока элементов 35 И существу" ют сигналы, которые модиФицируют адресные разряды, поступающие на входы сумматоров по модулю два 32,Назначения элементов Формировате"ля микрокоманд подмены 2 следующие,Регистр 25 предназначен для хранения кодов номеров отказавших суб"блоков операционного блока процессора и, в соответствии. с этими ходами, для настройки деаиФратора 20.На группу входов 30 блока 2 поступают коды логических условий сгруппы входов 18 устройства. Коды логических условий, поступающие на группу входов 18 устройства, разбиты надве части: первая определяет порядок ветвления в микропрограмме и осу"ществляет в зависимости от кода проверяемых логических условий, поступающих на вход блока 19, модиФикациюадреса очередной микрокоманды, втораячасть сигналов логических условийпозволяет определить необходимостьвыполнения вместо текущей микрокоманды эквивалентной последовательностив зависимости от входных данных операционного блока процессора,По сигналам с регистра 25 и группвходов 29 и 30 дешиФратор 26 Формирует три множества сигналов 9 и Я , фсоответственно./2Если выходной сигнал дешиФратора 26 попадает во множества Я, тона выходе элемента ИЛИ 27 появляетсясигнал, который поступает на выход 28 Формирователя 2. При этомвозможна достоверная обработка данных9 10308 операционным блоком процессора путем маскирования его неисправных субблоков, что осуществляется путем Формирования вместо текущей микрокоманды эквивалентной заменяющей последовательности микрокоманд.Если выходной сигнал деаиФрато" ра 26 попадает во множество Я , то на выходе элемента ИЛИ 31 и появля ется-сигнал, соответствующий отказу 10 процессора, т.е. при данных значениях операндов ( вход 30 Формирователя 2 ) и существ ующей неисправности операционного блока процессора содержимое регистра 25) маскирование последней путем выполнения эквивалентной последовательности микрокоманд вместо текущей микрокоманды невозможно.Если выходной сигнал дещиФрато- ра 26 попадает во множество Я гсуб" блоки операционного блока процессора исправны либо входные данные некритичны к отказам субблоков), на выхо" дах Формирования 2 сигналы отсутствуют и процессор продолжает досто" верную обработку входных данных.П р и м е р. Необходимо построить дещиФратор 2 ч при следующих исходных данных: число субблоков операционно" го блока процессора - 3; число микро" команд - 16 разрядность сигналов логических условий, соответствующих вырабатываемым данным - 2; результа гы моделирования неиспоавностей процессора заданы таблицей, на пересе- ценки строк и столбцов записаны но" З 5 мера множества, в которые должны по" падать выходные сигналы дешиФрато" ра 26Если для гекущих кодов отказавае" го субблока, микроопераций и операндов на пересечении строк и столбцов стоит циФра 1, то выходной сигнал деш 11:,регера 26 попадает во множеством . При этом на выходе 28 Формирователя 2 появляется сигнал.45Если на пересечении строк и столб" цов стоит циФра 2 выходной сигнал де. аиФратора 26 попадает во множест" во Я. Пои этом сигнал появляется на выходе 32 Формирователя 2,5 ОЕсли все субблоки операционного блока процессора исправны, выходные сигналы дещиФратора 26 попадают во множество Я (не показано) и на вы" ходах 28 и 32 Формирователя 2 сигна лы отсутствуют.В коде номера отказавшего суббло" ка первые стариие) три разряда ука" 10зывают номер отказавюего субблока впозиционном коде, последний разрядтип неисправности ( константа 0 иликонстанта 1) .Такой дещиФра,ор может быть построен по следующей методике; Например,. если неисправен первый субблоки тип неисправности " константа О,то этой неисправности соответствуеткод 0010. Зтот код поступает в рена тр 21 рЕсли на группу входов 29 Формиро"вателя 2 поступает код микроопераций 0001, а на группу входов 30 -.код операндов 01, выходной сигналдеюиФратора 26 попадает во множеством . При этом на выходе 28 Формиро"вателя 2 Формируется сигнал отказпроцессора не наступает и микрокоманда 0001 реализуется путем выпол"нения вместо нее эквивалентной занимающей последовательности микрокоманд.Если на группу входов 30 поступает код 01, сигнал на выходе девиФратора 26 попадает во множество Щ.,Приэтом на выходе 32 Формирователя появляется сигнал отказа,Микропрограммное устройство управления (,Фиг. 1) Функционирует вдвух режимах: при исправном операционном блоке процессора и при неисправных субблоках операционного блока процессора,Работа устройства в первом режиме.Триггер 22 находится в нулевомсостоянии. При поступлении на вход 6устройства тактового импульса кодоперации с входом 11 устройства черезкоммутагор 12 записывается в регистр 13.Код с выходом регистра 13 черезкоммутатор 1 ч поступает на адресныевходы блока памяти 15, С приходомимпульса с выхода элемента задерж"ки 7 с блока памяти 15 считываетсяпервая микрокоманда и записываетсяв регистр 16, При этом инФормация изрегистра 16 поступает в Формирова"гель 2 и блок 19. Сигнал с выходаэлемента задержки 8 проходит черезэлемент И чв этом режиме Функцио"нирования сигнал на первом выходеФормирователя 2 отсутствует) и разре"щает выдачу сигналов микроопераций срегистра 16 через блок элементов И 9на выходы устройства 10. С приходомочередного тактового импульса навход 6 устройства адрес очередной30801 12 Ее ЕеЕевшевКоды микроопераций Коды операндов Коды субблоков Фе 001 О ОО 11 О 1 ОО О 101 1 ООО 1 ОО 1 0001 00 1 2 2 2.0001 01 11 10 микрокоманды с блока 19 Формирования адреса через коммутатор 12 записывается в регистр 13, Далее устройство управления Функционирует по описанному алгоритму.Если происходит отказ одного иэ субблоков операционного блока процес" сора,он идентифицируется. средства" ми контроля процессора и на входы 11 поступает код адреса первой микро" команды микропрограммы диагностики процессора.8 режиме диагностики устройство функционирует аналогично Функционированию в первом режиме. В процессе выполнения микропрограммы диагностики определяется номер отказавшего субблока операционного блока процессора и тип неисправности,При считывании микрокоманды "Ко нец микропрограммы диагностики" из блока 15 памяти регистр 25 Формирователя 2 1, Фиг. 2) открывается по входу синхронизации, При этом кодномера отказавшего субблока и типа неисправности записывается в регистр 25.Далее устройство продолжает выполнять рабочую программу по описанному алгоритму. По сигналам, посту,пающим на первую 29 и вторую 30 группы входов Формирователя 2, и по содержимому регистра 25 дешиФратор 26 Формирует соответствующие выходные сигналы. Если выходные сигналы дешиФратора 26 принадлежат к множеству 0 , то устройство Функционирует в первом режиме работы. Если при.надлежит к множеству (2,то на выход 3 устройства из Формирователя 2 выдается сигнал отказа процессора.Если сигнал принадлежит к мно- жеству И, то через первый элемент ИЛИ 27 он поступает на первый выход 28 Формирователя 2 и переводит устройство во второй режим Функ. ционирования.Работа устройства управления во Втором режиме. Сигнал с выхода элемента задерж"ки 8 проходит через элемент И 5 наодновибратор 23, вход триггера 22и управляющий вход блока ассоциатив 5 ной памяти 1,При этом по содержимому операционной части микрокоманды, считаннойиз блока памяти 15, из блока 17 па"мяти считывается адрес первой микро"10 команды эквивалентной заменяющей по"слвдовательности микрокоманд и записывается через коммутатор 20 врегистр 21.Триггер 20 устанавливается в еди 15 ничное состояние, а одновибратор 23Формирует импульс,Так как сигнал на управляющем вхо"де блока элементов И 9 отсутствует,то код микроопераций считанной микро 20 команды на выходы 10 устройства непоступает. С приходом очередного тактовогоимпульса на вход 6 устройства из блока 12 памяти по адресу, хранящемуся в регистре 21,считывается первая микро" команда эквивалентной заменяющей по" следовательности микрокоманд.Далее устройство Функционирует ана.логично Функционированию в первом режиме. При считывании последней микро" команды эквивалентной заменяющей последовательности микрокоманд текущей микрокоманды на выходе поля метки оегистра 16 появляется единичный сигнал. Триггер 22 переходит в нулевое состояние, а устройство в целом - в первый режим работы. По адресу, записанному в регистре .13, из блока 15 памяти по описан"ному алгоритму считывается очереднаямикрокоманда. Далее устройство Функци,онирует аналогично описанному алго"ритму.45Изобретение позволяет повысить надежность и расширить области применения микропрограммных процессоров.1030801 Продолеение таблицы Коды операндов КодыЮВ1 Коды микроопераций 0010 0611 Еее Ю в ащв 2 2 0001 0010 0300 0101 ОО 0110 0110 0110 0110 1001 1 1 2 2 1 1 1 2 1 1011 1100 2 2 2 .1 1 2 21 1110 00 2 1 2 2 2 2 2 01 1111 2 1 2 1 2М в ее э е в е е евП р и и е ч а н и е. Знак "м" означает некритичность субблоков операционного блока процессора к значениям этих разрядов при вы" полнении микрокоманд, заданных в 4 кодах микрооперачий 2 1 1 1 2

СмотретьЗаявка

3431016, 27.04.1982

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ПЛАХТЕЕВ АНАТОЛИЙ ПАВЛОВИЧ, БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/00, G06F 9/22

Метки: микропрограммное

Опубликовано: 23.07.1983

Код ссылки

<a href="https://patents.su/10-1030801-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для логарифмирования

Следующий патент: Устройство диспетчеризации электронной вычислительной машины

Случайный патент: Питатель сыпучих материалов