G06F 1/04 — устройства для генерирования и(или) распределения синхронизирующих импульсов или сигналов, непосредственно образованных этими импульсами

Устройство для выделения маркера кадровой синхронизации

Номер патента: 1416962

Опубликовано: 15.08.1988

Авторы: Кузьмичев, Раптовский

МПК: G06F 1/04

Метки: выделения, кадровой, маркера, синхронизации

...на выходе элемента 23 иэ"за возможной неоднозначности в переключе-. нии разрядов регистра 1 сдвига. Им пульсы с выхода элемента И 24 поступают на счетный вход счетчика 19, ко-. торый формирует параллельный код числа нееовпадающих разрядов.Принцип сравнения приходящей и 25 идеальной КСП, находящейся в регистре 1 сдвига пояснен на фиг.3. В качестве примера рассмотрена 12-разрядная КСП, а приходящая КСП имеет ошибку в 6-м разряде. Ошибка выделяется в тот (ЗО момент, когда 6-й разряд приходящей КСП записывается в первый разряд ре гистра 1 сдвига. Двоичный параллельный код ошибки формируется счетчиком 19, В момент времени, когда приходящая КСП полностью запишется в ре" гистр, блок 3 сравнения формирует импульс уровня "1", если код ошибки...

Устройство для формирования цифровых последовательностей

Номер патента: 1416963

Опубликовано: 15.08.1988

Авторы: Пахарин, Чернориз, Ядрошникова

МПК: G06F 1/04

Метки: последовательностей, формирования, цифровых

...(счетчик 1 досчитает до максимума), с его выхода переноса на синхровход 10 блока 5 Формирования временных интервалов выдается сигнал, используемый для отсчета временного интервала.Длительность временных интервалов между изменениями вида цифровой последовательности Т; задается кодами К;-1, хранящимися в блоке 14 памяти формирователя 5 временных интервалов. Код К соответствующий количеству повторений выбранной реализации, считывается по адресу, определяемому состоянием счетчика 4, и подается с первой группы ныходон блока 14 па" памяти на информационные входы счет" чика 15. Сигнал сброса, поступающий по входу 9 сброса блока 5 формирования временных интервалов, через элемент ИЛИ 16 и элемент 17 задержки подается на вход разрешения записи...

Устройство для задержки цифровой информации с уплотнением

Номер патента: 1425632

Опубликовано: 23.09.1988

Авторы: Волощук, Дрозд, Лацин, Полин, Шипита

МПК: G06F 1/04

Метки: задержки, информации, уплотнением, цифровой

...будет записана последовательность единиц инулей, причем единица будет соотнет"ствовать совпадению записываемого(считываемого) в данном такте инфор 1425632мационного слова со словом, записанным (считанным) в предыдущем такте,По окончании одного цикла записи через К. тактов синхроимпульсов на5 входе 18 произойдет переключение счетного триггера 17 в ноль сигналом заема с выхода счетчика 7. Одновременно произойдет запись кода задержки в счетчик 7, обнуление счетчика 1 О, и начнется новый цикл задержки. При этом первая половина блоков памяти (блоки 8 и 13) будет приведена в режим чтения, В первом такте режима чтения происходит чтение информации из бло ка 13 по адресу К. Считанная информация (ноль или единица) через первый коммутатор 6...

Устройство для распределения импульсов

Номер патента: 1427354

Опубликовано: 30.09.1988

Автор: Богумирский

МПК: G06F 1/04

Метки: импульсов, распределения

...2, который откры 50вает группу 8 элементов И. Код изрегистра 7, поступает на первые входыэлементов ИЛИ 10, -10и проходит навходы дешифратора 9, Если в регистре7 находится код числа 1 ( = 1,и), то появляется сигнал на -омвыходе дешифратора 9, который подается на -ый информационный вход группы 6 элементов И. После этого появляется импульс на выходе элемента 5 задержки, по которому появляется импульс на выходе 15, устройства.По второму импульсу на счетном входе счетчика 1 в нем формируется код числа 2. При этом появляется сигнал на втором выходе дешифратора 2, который открывает группу 8; элементов И. В дальнейшем распределитель работает аналогично.В результате этого код из регистра 7; поступает на х-ые входы элементов ИЛИ 10;-10, и...

Устройство для синхронизации вычислительной системы

Номер патента: 1427355

Опубликовано: 30.09.1988

Авторы: Игнатьев, Латышев, Ушаков

МПК: G06F 1/04

Метки: вычислительной, синхронизации, системы

...генератора соединен с входом элементазадержки и является тактовым выходомблока, выход элемента задержки явля ется запускающим выходом блока. Изобретение относится к вычислительй технике и может быть использовано при проектировании микропроцессорнцх систем модульного типа.Цель изобретения - повышение точности за счет сохранения при выходе из строя одного из блоков выработки синхросигналов синхронной работы отдельных групп блоков.Йа фиг.1 лриведена схема устройства на фиг.2 - схема синхронизируемого генератора тактовых импульсов, на фиг.З - временная диаграмма работы устройства.Устройство содержит и блоков (1 -1) выработки синхросигналов. Кажды блок 1 содержит задающий генератор 2, элемент 3 задержки, синхровход 4, запускающий выход...

Устройство для генерации меток времени

Номер патента: 1432492

Опубликовано: 23.10.1988

Автор: Мамедов

МПК: G06F 1/04

Метки: времени, генерации, меток

...до тех пор, пока по входу 19 не поступит сигнал. При этом триггер 12 устанавливается в "О", элементы И 2 и 4 закрываются, и устройство прекращает работу.Возможны две аварийные ситуации. На первом этапе работы устройства возможно переполнение счетчика 9, При этом с его выхода переполнения сигнал через элемент ИЛИ 15 устанавливает триггер 11 в "1", и на выходе 23 устройства возникает сигнал Ошибка" Помимо этого на втором этапе работы устройства в случае несвоевременной реакции вычислительного комплекса на сигнал "Готовность" на выходе 22 устройства повторный сигнал с выхода переполнения счетчика 7 проходит через элемент И 3, элемент ИЛИ 15 и также устанавливает триггер 1 ошибки в "1". При нормальной работе устройства на втором этапе...

Устройство перезапуска автоматизированной системы обработки информации

Номер патента: 1432493

Опубликовано: 23.10.1988

Авторы: Белый, Давыдов, Котс, Линов, Савинова

МПК: G06F 1/04

Метки: автоматизированной, информации, перезапуска, системы

...вьгхсде АВ схемы 6 при -сутствует логическая единица), итактовые импульсы с выхода ГТИ 11 через элементы ИЛИ 3 и 2 увеличиваютзначение содержимого счетчика ч, Приэтом осуществляется последовательныйпросмотр регистров блока 1 памяти,Как только значение г. на первой группе выходов становится равно или превышает установленное время переза. -пуска (содержимое регистра 5) на выходе А ( В схемы 6 сравнения устанавливается сигнал логического нуля, который закрывает элемент И 14 и запрещает подачу тактовых импульсов ГТИ 11на счетный вход счетчика 4, .Пс сигналу логической единицы на выходе М Всхемы 6 сравнения оцнсв.,братор 8 через открытый элемент И 3 устанавливает триггер 9 в нулевое состояние,Сигнал логической единицы с инверсного входа...

Устройство для синхронизации блоков памяти

Номер патента: 1439566

Опубликовано: 23.11.1988

Авторы: Бруевич, Воробьев, Куликов, Смирнов

МПК: G06F 1/04

Метки: блоков, памяти, синхронизации

...расширения диаграммы оказывается недостаточно, тоописанный процесс повторяется, иначе после окончания тестирования отрицательный импульс поступает на вход15 и через элемент И 12 подается настробирующий вход дешифратора 11, азатем на выход 16. В результате число, записанное в счетчике 36, увеличивается еще на одну единицу, чтообеспечивает запас надежности по величине С. Одновременно отрицательныйимпульс с входа 15 через элемент ИЛИ 457 поступает на первый вход элементаИЛИ 8. Поскольку на его второмвходе присутствует низкий уровеньнапряжения с инверсного выходатриггера 6, то отрицательный импульсформируется также на выходе элемента ИЛИ 8 и своим задним фронтом пе реводит счетчик 10 в состояние (001) .Кроме того, отрицательный импульс...

Программируемый таймер

Номер патента: 1441407

Опубликовано: 30.11.1988

МПК: G06F 1/04, G06F 11/30

Метки: программируемый, таймер

...счетчика-делителя 2частоты ка первый адресный вход ПЗУ3, Таким образтом, адрес команды, вь- бираемой иэ 1.ЗУ 3, состоит иэ трехЧаСТЕй, ПЛИ ЭТОМ СтдтЦЯЯ:аСТЬ аДРЕс 0 с т (5. кя.";р д Б л Ря с р е д к я 5часть - из ре- стра ч услов;я и младДЯ ДСТЬ - СО СНЕ ТЧИКД - ДЕЛИТЕ 1 сДСТОТЬ, т.оцот ЯЯ ОСЛС ОВДТСЛ;КОСТЬКЕ ПЗУ ;, Г ЕГО ВЬХОдОВ - 3) ПОСту Зс т т. - ,т, т ЛтгтХ Д К ЬКОН я-, Ьчт;Х"тс, .:то., повд тВ, 1. Гых ГСЭЛаТОдт Тд:;Тор 1 ия; - .; ТЬ Кдд". т Хг - тт -Ч ,тт - Рт- "я ТЗ 1 НЕПзРР;О ОСТУ:Д т,;Ч.": СЬ т которые "я Рго Входе прообразугся Б ИККРЕ "Ен, Нутл КОДОВ"ПР СЛСДС атРЛ СЫ 3 -, ,тт 1т О С " Е т О Р Я т С г Втперебол Я;.Рек р ПЗУ 3, Пас-Р завел- ПЕИЯ КдЬГГО ПГОХОд .1 або МИКООПГОтт; яют синхг они элутттис" сигк я тт кривгттт...

Устройство для синхронизации модулей вычислительной системы

Номер патента: 1442985

Опубликовано: 07.12.1988

Авторы: Розенблюм, Федорова, Яковлев, Яценко

МПК: G06F 1/04, G06F 13/00

Метки: вычислительной, модулей, синхронизации, системы

...И-ИЛИ-НЕ 13-1 (для д1 2, 3; 13, 2, 1 соответственно) переходит из в О"., вызывая переключение элемента НЕ 14-1 нз "О" в "1".314Однако, так как выход элемента НЕ14-1 подключен к шинепо и;оводному ИЛИ, шинапереходит в состояниевысокого потенциала "1" лишь в результате срабатывания из "0" в "1 цэлементов НЕ 14-1 во всех остальныхблоках устройства; В о т на переход шиныв "0" происходит переключение выхода 10- 1 :.оммутатор 9 лз"О" в "1", после чего элсмен И-ЧЕ12-1 переключается в ,"Г , теь. самымвыдавая сигнал запроса модуля ча вы"полнение 1-й операции, После ее выполнения модуль 6 ьфддает сигнал ответа путем переключения своего выхода 8- из "1" в 0", что вызываетпереход элеме.".а Р -ЛИ-НЕ 13-х из , "0" в "1", а затем элемента НЕ...

Таймер

Номер патента: 1444738

Опубликовано: 15.12.1988

Авторы: Веревкин, Галабурда, Ильин, Лачугин, Могилко

МПК: G06F 1/04

Метки: таймер

...переполнение счетчика 12, сигнал с выхода переполнения устанавливает в нулевое состояние триггер 14, что приводит к закрытию элемента И 10 и открытию элемента запрета 11, а также к разрешению выдачи адреса через селектор 15 со счетчика 13.Поскольку в счетчике 13 установлен адрес (К+1)-й ячейки, то по переднему фронту следующего импульса от генератора 16 произойдет чтение содержимого (К+1) -й ячейки блока 1, далее - запись считанного слова в счетчик 3, Из блока 2 памяти в мультиплексор 4 поступит признак соответствующей частоты. При наличии на входе 7 таймера сигнала данной частоты произойдет прибавление единицы к содержимому счетчика 3, после чего новое содержимое счетчика 3 будет записано по старому адресу, т, е. в (К+1)-ю ячейку блока...

Устройство для синхронизации вычислительной системы

Номер патента: 1456942

Опубликовано: 07.02.1989

Автор: Макаров

МПК: G06F 1/04

Метки: вычислительной, синхронизации, системы

...элемента И 14 формируетсяпоследовательность, содержащая каждый второй импульс делителя, на выходе элемента И 15 - каждый четвертый и т.д. Элементы И 14 - 19 стробируются сигналами управляющего кода. При единичном сигнале в соответствующем разряде управляющего кода соответствующая последовательность импульсов пропускается на элемент ИЛИ 20, а при нулевом запрещается, Таким образом, в зависимостиот управляющего кода за один циклпересчета счетчика 11 на выходе микросхем К 155 ИЕ 8 может быть получено1456942 Устройство для синхронизации вычислительной системы, содержащее задающий генератор, элемент И, счетчик и дешифратор, причем разрядные выходы счетчика соединены с входами дешифратора, выходы которого являются выходами устройства, о т л и...

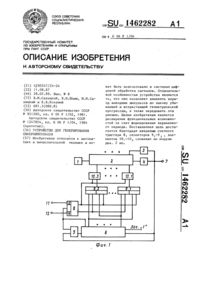

Устройство для генерирования синхроимпульсов

Номер патента: 1462282

Опубликовано: 28.02.1989

Авторы: Коханый, Плиш, Савицкий

МПК: G06F 1/04

Метки: генерирования, синхроимпульсов

...следования которых уменьшается по закону геометрической прогрессии (фиг. 2 б) на входе 11 устройстваустанавливается "1", на входе 12"0". В исходном состоянии счетчик 2и регистр 6 сдвига обнулены. На пря 1 А 62282мом выходе триггера 8 - "0", на выходах элементов 10 сложения по модулю два - нулевой потенциал,Тактовые импульсы изменяют состояние выходов счетчика. Восьмой тактовый импульс приводит счетчик 2 в исходное состояние. При этом по отрицательному перепаду в старшем разряде счетчика 2 формирователь 3 импульса формирует короткий импульс,по которому производится запись "1в первый разряд регистра 6 сдвига,и с задержкои , превышающей длительность импульса, производится записьединичного сигнала через селекторы91 и элементы 10.1...

Устройство для синхронизации блоков вычислительной системы

Номер патента: 1467551

Опубликовано: 23.03.1989

МПК: G06F 1/04

Метки: блоков, вычислительной, синхронизации, системы

...с тактового генератора 9 (фиг.2),Последовательности импульсов с выходов делителя 5 частоты и триггеров 6-8 представляют собой последовательности прямоугольных импульсов с частотой в четыре раза меньше частоты тактового генератора 9, причем каждая последовательность сдвинута по фазе относительно предыдущей на одну восьмую периода, эти последовательности поступают на выходы блока 1, с которых по линиям связи поступают на входы блоков 2,В блоках 2 эти последовательности поступают на входы элементов 10 и 11 сложения.по модулю два, с выходов которых они поступают на входы элемента ИЛИ 12, на выходе которого образуется последовательность, частота которой в четыре раза древьппает частоту, передаваемую по линиям связи,Фформула изобретения...

Устройство для синхронизации приема асинхронных сигналов

Номер патента: 1471186

Опубликовано: 07.04.1989

Автор: Самотугин

МПК: G06F 1/04

Метки: асинхронных, приема, сигналов, синхронизации

...информациеймежду устройствами, имеющими автойомные тактовые генераторы,Целью изобретения является повышение быстродействия.На фиг.1 приведена схема устроиства; на фиг.2 - временные диаграммыустройства.Устройство содержит элемент НЕ 1,триггеры 2-4, синхровход 5, вход 6асинхронного сигнала и выход 7.Устройство работает следующим образом.При поступлении на вход 6 устройства информационных асинхронных сигналов . единичного уровня триггер 3переключается в нулевое состояние.Триггер 2 переключается в единичноесостояние по переднему фронту синхроимпульсов, поступающих на вход 5устройства, так как на его нулевойвход поступает сигнал нулевого уров-.ня с выхода элемента НЕ 1. Триггер 4переключится в единичное состояниепод действием сигнала с...

Устройство для управления синхронизацией памяти

Номер патента: 1472893

Опубликовано: 15.04.1989

Авторы: Бруевич, Воробьев, Куликов, Садовникова

МПК: G06F 1/04

Метки: памяти, синхронизацией

...11, он выдается навыход 21, обеспечивая дополнительныйсдвиг первого синхросигнала на одиншаг в глубину области устойчивойработы (успешное прохождение теста вэтом случае также может быть случайным). Одновременно отрицательный импульс через элементы ИЛИ 4 и 5 поступает на счетный вход счетчика 10,увеличивая его содержимое на единицу, и выдается на выход 17 устройст-.ва. В результате установка первогосинхросигнала заканчивается, а второйсинхросигнал смещается к началу формирования временной диаграммы.Установка синхросигналов с второго по седьмой происходит аналогично.При настройке седьмого синхросигнала в счетчике 10 записан код (111)и на выходе элемента И 13 присутствует "1" (высокий уровень напряжения). Поэтому отрицательный...

Устройство для формирования синхросигналов

Номер патента: 1474628

Опубликовано: 23.04.1989

МПК: G06F 1/04

Метки: синхросигналов, формирования

...аэлемент И"НЕ 16 становится подго 3товленным для приема очередного управляющего импульса и преобразованияего в выходной импульс на выходе 15(третий триггер находится в состоянии "1"). Этим импульсом завершается серия выдачи импульсов устройством так как после установки имФ3пульсом с выхода 15 триггера Т3группы 3 в "0" все триггеры группы3 устанавливаются в "0" (для приводимого примера), и появившийся следующий импульс с выхода. элемента И 8 через элемент НЕ 19 преобразуется в упа+1равляющий импульс на выходе 15 распределителя 13 импулвсов, которыйприбавляет "1" в счетчик 2 циклов йчерез элемент И 7 переносит код требуемой последовательности импульсовиэ блока 12 в группу 3 триггеров.Элемент НЕ 19 используется с целью обеспечения...

Устройство для задержки информации с контролем

Номер патента: 1474833

Опубликовано: 23.04.1989

Авторы: Волощук, Дрозд, Лацин, Лебедь, Полин

МПК: G06F 1/04, H03K 5/153

Метки: задержки, информации, контролем

...пяти). Еслиже за Р циклон повторного сбоя по зафиксированному н регистре 16 адресу .не происходит, то счетчик 1 О, досчитав до нуля, вырабатывает сигналзаема и блокирует поступление насвой вычитающий вход сигналов переполнения (конца цикла) нэ счетчика 6адреса. Одновременно с этим однонибратор 11 вырабатывает короткий импульс и сбрасывает триггер 14 н "0",тем самым разрешая фиксацию и анализ 25следукзцих сбойных адресов. Таким образом, устройство позволяет распознавать сбои и отказы ячеек накопителя изаменять отказавшую ячейку на резервную, что повышает надежность Функционирования цифровой задержки информации .Счетчик 6 адреса представляет собой суммирующий счетчик по модулюК = 2"-1, где п - разрядность счетчикаВыход переполнения его...

Устройство для синхронизации приема асинхронных сигналов

Номер патента: 1476453

Опубликовано: 30.04.1989

Автор: Бантюков

МПК: G06F 1/04

Метки: асинхронных, приема, сигналов, синхронизации

...работа триггера 7 по синхровходу и запускается элемент 6 за- держки этого блока 2.1.Через времяпо переднему фронту импульса с выхода элемента 6 задержки устанавливается в единичное поло жение триггер 7 блока 2.1. На выходе 4.1 появляется сигнал с прямого выхода триггера 7, одновременно вследствие появления на инверсном выходе триггера 7 нулевого сигнала, триггер 5 блока 2.1 устанавливается в нулевое положение. В момент окончания импульса на первом выходе рас 2пределителя 1 импульсов триггер 7устанавливается в нулевое положение,На входе 4.1 оканчивается импульс.Устройство установилось в исходноесостояние.Таким образом, на выходе 4.1(соответствующем входу 3.1), выданимпульс, синхронный импульсу, выданному распределителем 1 импул":сови...

Распределитель импульсов

Номер патента: 1481733

Опубликовано: 23.05.1989

МПК: G06F 1/04

Метки: импульсов, распределитель

...единичные логическиеуровни, а на выходе элемента 2 И-И 1 Я НЕ 3 - нулевой логический уровеньиз-за срабатывания элемента И 21.С приходом третьего положительного импульса по шине 39 управленияраспределитель импульсов перейдетв состояние "110",Далее при поступлении ка шину 39управления четвертого, пятого и шестого положительных импульсов на первом, втором и третьем выходах 36 - 38устройства последовательно будутсформированы следующие состояния"100", "101" и "001". Прй этом очевидно, что шестой импульс переводитраспределитель импульсов в исходноесостояние, с которого начиналась егоработа перед подачей первого импульса по шине 39 управления устройством.В режиме устройства с одним каналом опроса распределитель импульсовработает следующим...

Датчик времени

Номер патента: 1481734

Опубликовано: 23.05.1989

МПК: G06F 1/04

...последовательности импульсов (фиг.2 б, в,г), сдвинутые друг относительно друга на интервал времени. Импульсы с первого выхода дешифратора 3 подаются на счетный вход делителя 4 30 частоты, который вырабатывает импульсы (Аиг. 2,д), засинхронизированные с импульсами б с первого выхода дешиФратора 3, В момент времени, когда с делителя 4 частоты приходит уровень логической "1" на первые входы элементов И 8, 9, 6, импульс последовательности б, пройдя через элемент И 8, устанавливает триггер 7 в нулевое ф состояние, тем самым запрещая прохож дение сигнала на считывание текущего значения времени, который приходит на второй вход элемента И 10 в ниделогической "1". Импульс в с второго выхода дешиАратора 3, пройдя через 45 элемент И 6, попадает на...

Устройство для синхронизации вычислительной системы

Номер патента: 1495773

Опубликовано: 23.07.1989

Автор: Куклин

МПК: G06F 1/04

Метки: вычислительной, синхронизации, системы

...цикла, всегда производится при совпадении на входахэлемента И 45 обнуляющего сигналас выхода элемента ИЛИ 40 с синхроим.пульсом С (по концу сигнала С ).Обнуляющий сигнал формируется припомощи элементов ИЛИ 40, И 36 " 38:в синхронном режиме работы по поступлению сигнала М с входа 6 черезэлемент И 37; при отсутствии синхронного сигнала М 2 сигналом 1 з вначале следующего цикла, при сохраняющемся состоянии К на счетчике 33и на дешифраторе 34 через элементИ Зб; в режиме подсинхронизации с сигналами М (при включении триггера 44) любым сигналом М, при условии завершения режима подсинхронизации по сигналу М 1, т,е. при выключении триггера 32 и снятии при этомзапрета на прохождение сигнала Мчерез элемент И 38,Задание режима:подсинхронизациис...

Устройство для формирования временных интервалов

Номер патента: 1495774

Опубликовано: 23.07.1989

Авторы: Абакумова, Вербовский, Зеленский, Кухарчук, Струтинский

МПК: G06F 1/04

Метки: временных, интервалов, формирования

...+ Т (сопят 3 - сопят 2) . Выбор констант. Для определенияконстант должны быть заданы интервалследования импульсов основного каскада Т, который может быть полученсо средней точностью 0,5 периода задающего генератора, а также должнабыть задана длительность макроциклаТ ц работы устройства на которомпогрешность должна быть скорректирована,В общем случае Т,с Т с Т, перваяконстанта определяется с учетом (1),как целая часть отношения 5 14 нии содержимого счетчика 5 с второй константой. При этом триггер 11 переключается в единичное состояние. На следующем тактовом импульсе переключается в единичное состояние и триггер 10, в результате чего при очередном появлении высокого потенциала на выходе блока 3 сравнения импульс с генератора не проходит...

Распределитель импульсов

Номер патента: 1504650

Опубликовано: 30.08.1989

Автор: Чибисов

МПК: G06F 1/04, H03K 5/15

Метки: импульсов, распределитель

...1 ина выходе 15, в момент временивызовет переключение триггера 1 всостояние иОи и триггера 2 в состояние и 1 и в момент времени С и 1 со 8ответственно,В момент времени Содновибратор10,отработав заданную длительность(время задержки между срезом и фронтом выходных импульсов), переключится из состояния иОи в состояние и 1",что, в свою очередь, вызовет запускодновибратора 9 в момент времени й 1,Запуск одновибратора 9 вызоветизменение сигнала на входе 16 с и 1 ив иОи в момент времени Г. отработавзаданную длительность, одновибратор9 в момент. времени :, изменит состояние выхода с ии в иОи, что вызовет запуск одновибратора 10 и изменение сигнала на входе 16 в моментвремени й, и 1 соответственно,В момент времени С 1 ипроизойдет переключение...

Устройство для выработки синхросигналов

Номер патента: 1506441

Опубликовано: 07.09.1989

Авторы: Гаврилюк, Кирищук, Феоктистов

МПК: G06F 1/04

Метки: выработки, синхросигналов

...последовательность синхросигналов. Если на вход 4 останова устройства поступает сигнал, триггер 10устанавливается в "1", запрещая прохождение сигналов с выходов блока 1 10постоянной памяти через элементы И 59 первой группы, и генерация тактовыхимпульсов на выхоцах 32-36 устройстваостанавливается, Если при этом на вход11 запуска устройства поступает сигнал, то триггер 10 сбрасывается в "0",и генерация синхроимпульсов на выходах 32-36 устройства продолжаетсяс того места, где произошел останов.Если необходимо запустить генерацию тактовых импульсов с определенного места цикла, то подав на входы 2731 устройства соответствующий код,в частности это может быть и код начала цикла, а на синхронход 23 разрещения записи устройства подав...

Устройство для синхронизации нескольких вычислительных машин

Номер патента: 1508200

Опубликовано: 15.09.1989

Авторы: Бекасова, Гаганов, Крылов, Мочалов, Рузин, Русаков, Чистяков

МПК: G06F 1/04

Метки: вычислительных, машин, нескольких, синхронизации

...и поступает на выход каксигнал прерывания.Для синхронизации работы нескольких ЭВМ, предусмотрен делитель 8 частоты, выдающий импульсы синхронизации.Делитель 8 частоты формирует трисигнала синхронизации с периодами5, 10 и 20 мс. Выбор периода выдачи сигнала осуществляется при подготовке к работе в реальном масштабе времени.,15082 формула изобретения 1. Устройство для синхронизации нескольких вычислительных машин, содержащее генератор тактовых импульсов, блок управления, блок формирования прерываний, регистр, о т л ич а ю щ е е с я тем, что, с целью расширения функциональных возможнос тей за счет обеспечения синхронной работы нескольких вычислительных машин в реальном масштабе времени, в устройство введены счетчик, делитель частоты, блок...

Устройство для синхронизации распределенной вычислительной системы

Номер патента: 1508201

Опубликовано: 15.09.1989

Авторы: Клименко, Пьявченко, Сироткин, Строцкий

МПК: G06F 1/04

Метки: вычислительной, распределенной, синхронизации, системы

...Последовательность формирования и появления сигналов на шинах блока 36 показана на фиг,9,Управление работой блока 36 осуществляется блоком 35 управления, Он является программируемым контролле 45 ром и позволяет по макрокоманде осуществлять разовый или циклический опрос аналоговых каналов при синхронизации процесса от микроЭВМ 2 локальной вычислительной сети 1. При синхронизации от блока 8 блок 35 может работать в многоцикловом режиме без дополнительного управления от хостмашины при каждом цикле опроса. Структура управляющего слова для блока 35. приведена на фиг.10, Старший бит уп 55 равляющего слова является признаком вида синхронизации - отмикроЭВМ 2 или от блока 8, следующий бит является признаком циклической работы устройства,...

Устройство для выделения кадрового синхронизирующего слова

Номер патента: 1509857

Опубликовано: 23.09.1989

МПК: G06F 1/04, H04L 7/00

Метки: выделения, кадрового, синхронизирующего, слова

...кадра, свидетельствующем об окончании информационного кадра, запускается одновибратор 2. Длительность формируемого одновибратором 2 импульса выбирается меньше половины периода частоты тактовых импульсов, Импульс с выхода одновибратора 2 сбрасывает триггер 3 в нулевое состояние, Высокий потенциал с инверсного выхода триггера 3 разрешает работу формирователя 5 и открывает элемент И 11, Устройство готово для анализа поступающей информации в ожидаемом временном интервале в предположении, что этот код является кодом кадрового синхрослова.При несовпадении битов принимаемого и формируемого кодов на выходе блока Ь сравнения появляется высокий йотенциал, открывающий элемент И 11, что вызовет по спаду тактового импульса на выходе элемента НЕ...

Распределитель импульсов

Номер патента: 1511747

Опубликовано: 30.09.1989

МПК: G06F 1/04, H03K 5/19

Метки: импульсов, распределитель

...сигналкоторый подготовит соответствующий элемент И 11.1 - 11.п для прохождения очередного тактового импульса на вычитающий вход счетчиков 12,1-12,п и 23.1-23,п.Очередной тактовый импульс с тактового входа 20 устанавливает счетчик 5 в соответствующее состояние (из содержимого счетчика 5 вычитается очередной импульс или к содержимому счет 151747чика 5 прибавляется очередной импульс), и на определенном выходе группы 9 элементов И появляется импульс, который перебрасывает очередной триг 5 гер 0.1-10.п в единичное состояние и на следующий выход 221-22.п начинается выдача выходного импульса, Одновременно тактовый импульс через элементы И 111-11.п, в каналы которых 1 О уже выдаются выходные импульсы, поступает на вычитающие входы счетчиков...

Устройство для формирования цифровых последовательностей

Номер патента: 1513434

Опубликовано: 07.10.1989

Авторы: Лейкина, Лесовой, Ульянов

МПК: G06F 1/04

Метки: последовательностей, формирования, цифровых

...записать логические "1" в ячейках с адресами, отмеченными в таблице..Таким образом, на выходах блока 3 памяти формируются дополнительные номиналы коэффициентов деления, отличные от коэффциентов деления с выходов. блоков 2 и 7 памяти, что дает возможность расширить количество одновременно формируемых коэффициентов деления при одних и тех же аппаратурных затратах, или дает возможность иметь лучшие показатели надежности на каждый формируемый коэффициент деления.5134346 45 55 5Устройство является схемой реализации формирования р .по формуле (4) для и = 1 и вычисления значения р, равного наименьшему общему кратному Г,чисел р РР:Р = (Р 1 РР) (5) где Р(Р, Р р ) - наименьшееобщее крат.ное циселР РРо При этом в блоке 2 памяти в...