Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

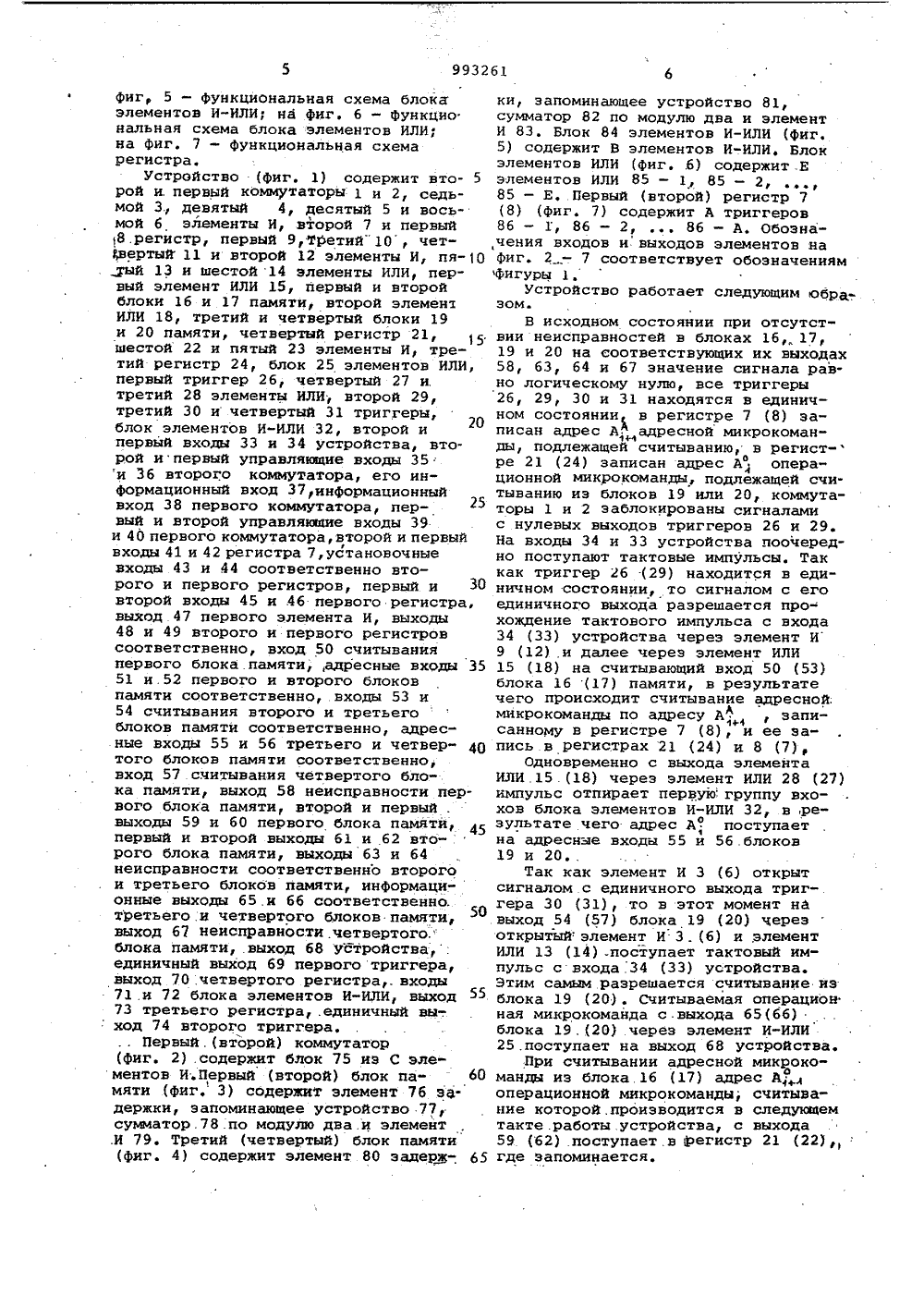

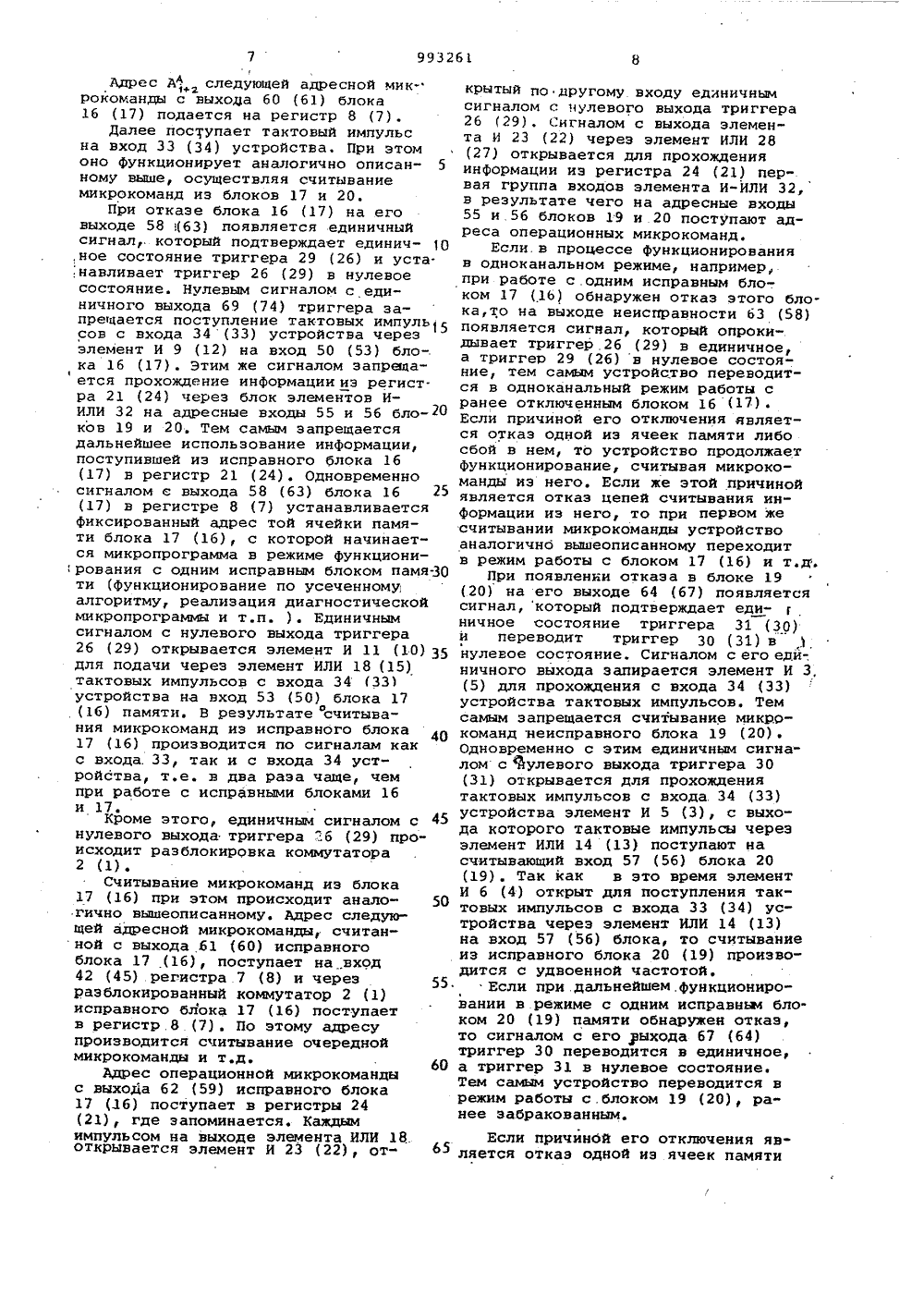

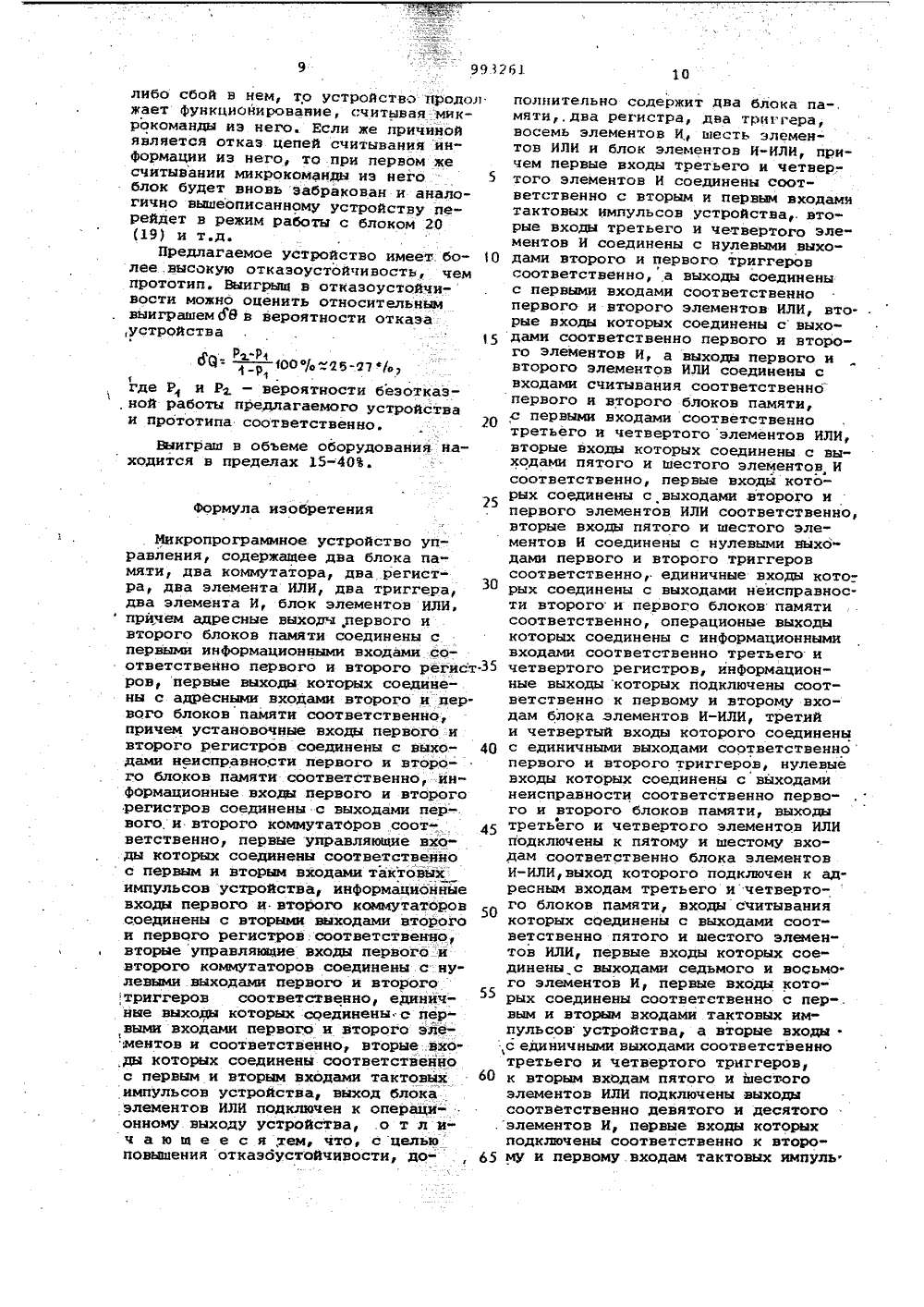

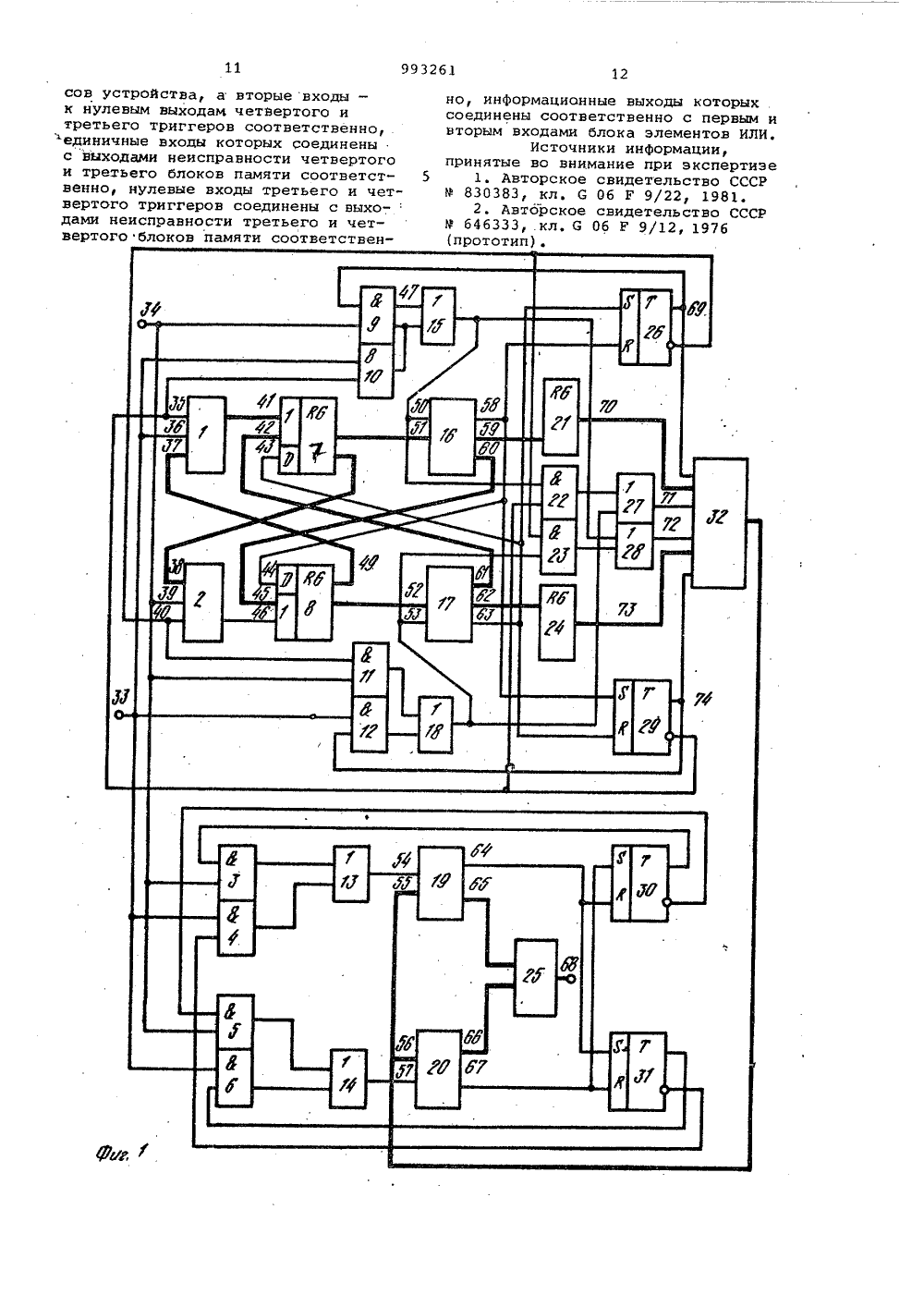

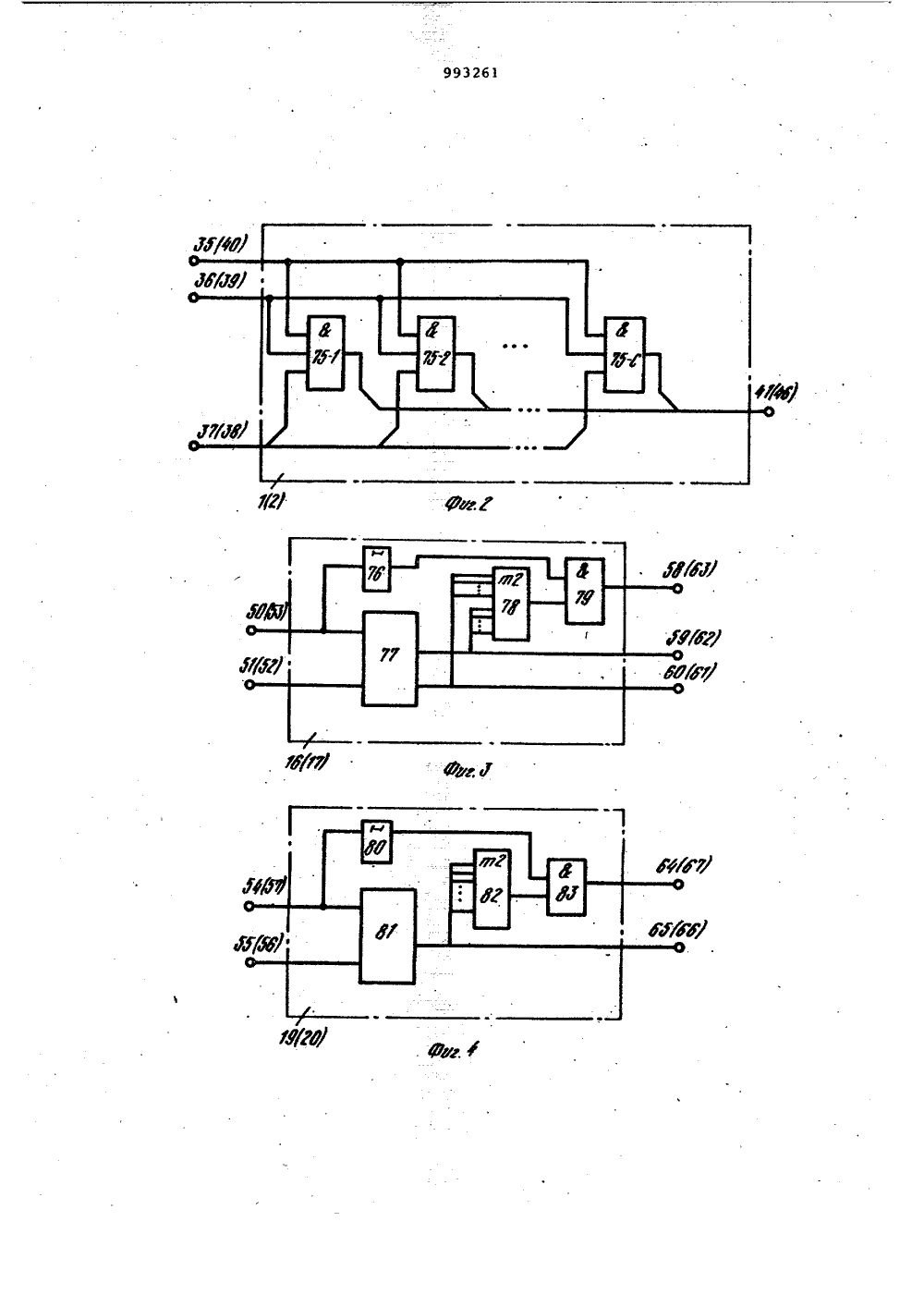

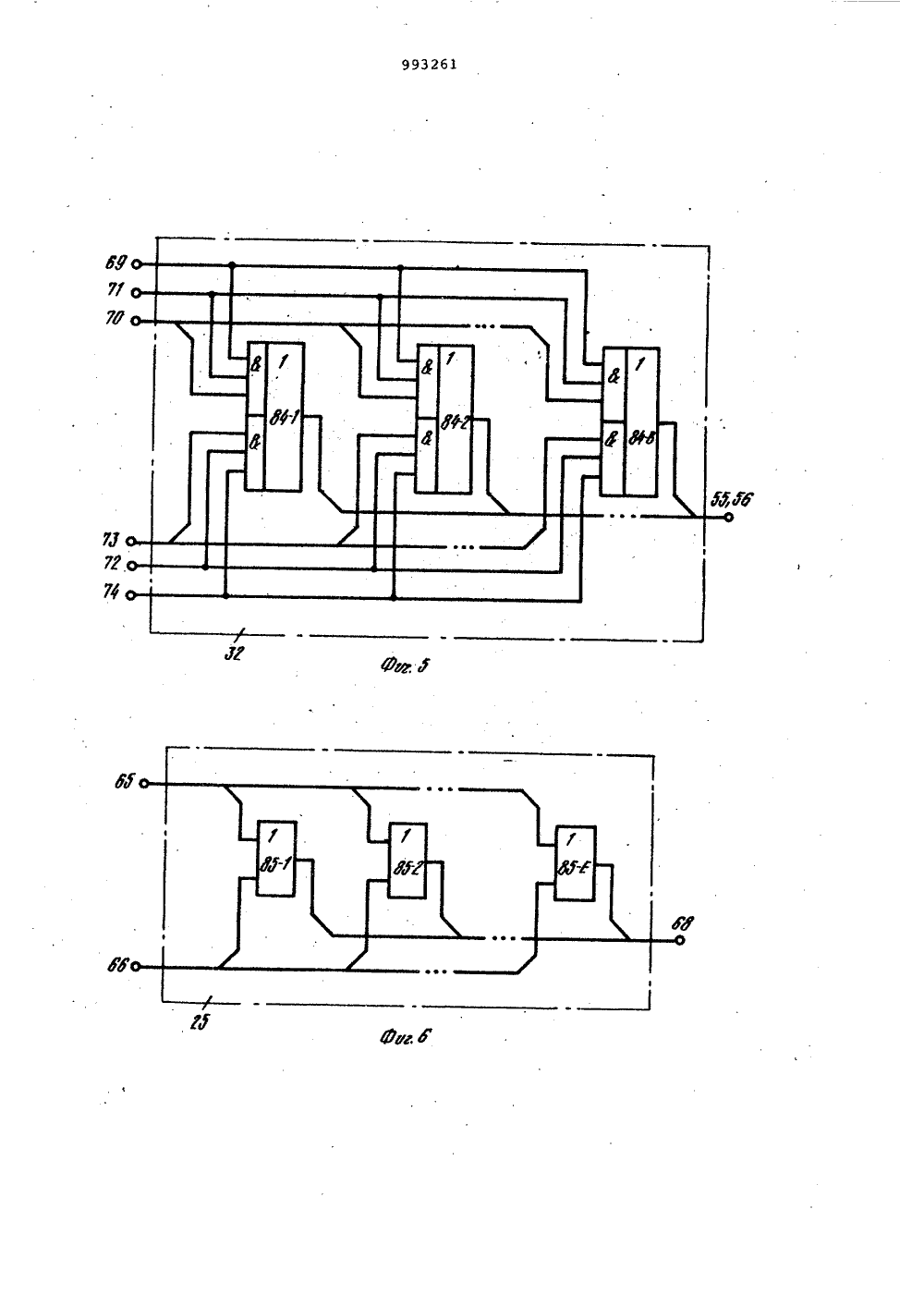

Союз СоветскихСоциалистическихРеспублик ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1,993261(63) Дополнительное к авт, свид-ву(22) Заявлено 0209.81 (21 Ь 334996/18-24 1) М Кп 3 С 06 Р 9/22 с присоединением заявки йоГосударственный комитет СССР ио делам изобретений и открытий(088. 8) Опубликовано 300183,Бюллетень М 4 Дата опубликования описания 300183(71) Заявител 4) МИКР ГРАММНОЕ УСТРОЙСТВОПРАВЛЕНИЯ Изобретение относится к вычислительной технике и может быть использовано в устройствах управления ЭВМ,Известно перестраиваемое микропрограммное устройство. управления, содержащее два блока памяти, два регистра, два коммутатора, два триг-, гера, элементы ИЛИ и элементы И 1.,Однако устройство обладает низкой отказоустойчивостью, обусловленной структурной корреляцией адрес- , ных и операционных частей микрокоманд при идентификации отказов в них., большим количеством.оборудова" ния, обусловленным дублированием информации в.ячейках блоков. памяти при наличии в микропрограмме повторяющихся микрокоманд, низким быстродействием, .обусловленным снижением частоты выдачи микрокоманд на выхо де устройства при отказе. одного иэ. блоков памяти.Наиболее близким к предлагаемомуГ по технической сущности и положитель. ному эффекту является перестраиваемое микропрограммное устройство уп-. равления,.которое содержит.два.блока памяти, два коммутатора, два регист- ра, два элемента И, два триггера, два элемента И, блок элементов ИЛИ,причем круппы адресных выходов первого и второго блоков памяти соедине-.ны с первыми группами информационныхвходов соответственно первого и второго.регистров, первые группы выходовкоторых соединены с группами адрес-.ных.входов второго и первого блоковпамяти. соответственно, причемустано.вочные входы первого и второго ре- -гистров соединены.с выходами неисправности .первого и второго блоковпамяти соответственно, .входы второйгруппы информационных входов первого и второго регистров соединены сгруппой .выходов первого и второгокоммутаторов соответственнЬ, первыеуправляющи. входы которых соединенысоответственно .с первым и вторымвходами устройства, входы группы информационных. входов первого и .второ-.го коммутаторов соединены с выходамивторой группы .выходов .второго и первого.регистров соответственно, вторые.управляющие входы первого.и вто"рого триггеров соответственно, единичные выходы которых соединены спервыми входами первого и второгоэлементов .И соответственно, вторыевходы .которых .соединены .соответст венно спервыми.и вторым входами уст 993261ройства, причем выходы блока элементов ИЛИ являютсягруппой выходовустройства (,2Недостатками данного устройстваявляютсянизкая отказоустойчивость,большой объем обрудования и низкоебыстродействие,Цель изобретения - повышение отказоустойчивости. Поставленная цель достигается тем, что устройство, содержащее два блока О памяти, два коммутатора, два регистра, два элемента ИЛИ, два триггера, два элемента И, блок элементов ИЛИ, причем адресные выходы первого и второго блоков памяти соединены с 15 первыми информационными входами соответственно первого и второго регистров, первые выходы которых соединены с адресными входами второго и первого блоков памяти соответственно, причем установочные входы первого и второго регистров соединены с выходами неисправности первого и второго блоков памяти соответственно, информационные входы первого и второго регистров соединены с выходами первого и второго коммутаторов соответственно, первые управляющие входы которых соединены соответственно с первым и вторым входами тактовых им. пульсов устройства, информационные входы первого и второго коммутаторов соединены с вторыми выходами второго и первого регистров соответственно, вторые управляющие входы первого и второго коммутаторов соединены с нулевыми выходами первого и второго триггеров соответственщэ, единичные выходы которых соединены с первыми входами первого и второго элементов И соответственно, вторые вхо" 40 ды которых соединены соответственно с первым и вторым входами тактовых импульсов устройства, выход блока элементов ИЛИ подключен коперационному выходу устройства, дполнительно 45 содержит два блока памяти, два регист. ра, два триггера, восемь элементов И, шесть элементов ЙЛИ и блок элементов И-ИЛИ, причем первые входы третьего и четвертого элементов И соедине ны соответственно с вторыми и первыми.входами тактовых импульсовустройства, вторые входы третьего и четвертого элементов И соединены с нулевыми выходами второго и первого триггеров соответственно, а выходы соединены с первыми входами со" ответственно первого и второго элементов ИЛИ, вторые входы которых соединены с выходами соответственно первоге и второго элементов И, а 60 выходы первого и второго элементов ИЛИ соединены с входами считывания соответственно первого и второго блоков памяти, с первыми входами соответственно третьего и четверто го элементов ИЛИ, вторые входы которых соединены с выходами пятого и шестого элементов И соответственно, первые. входы которых соединены с выходами второго и первого элементов ИЛИ соответственно, вторые входы пятого и шестого элементов И соединены с йулевыми выходами первого и второго триггеров соответственно, единичные входы которых соединены с выходами неисправности второго и первого блоков памяти соответственно, операционные выходы которых соединены с информационными входами соответственно третьего и четвертого регистров, информационные выходы которых подключены соответственно к первому и второму входам блока элементов И - ИЛИ, третий и четвертый входы которого соединены с единичными выходами соответственно п .рвого и второго триггеров, нулевые входы которых соединены с выходами неисправности соответственно первого и второго блоков памяти, выходы третьего и четвертого элементов ИЛИ подключены к пятому и шестому входам соответственно блока элементов И-ИЛИ, выход которого подключен к адресным входам. третьего и четвертого блоков памяти, входы считывания которых соединены .с выходами соответственно пятого и шестого элементов ИЛИ, первые входы которых соединены с выходами седьмого и восьмого элементов И, первые входы которых соединены соот:ветственно с первым и вторым входами тактовых импульсов устройства, а вторые входы - с единичными выходами соответственно третьего и четвертого.триггеров,.к вторым входам пятого и шестого элементов ИЛИ подключены выурды.соответственно девятого и десятого элементов И, первые входы которых подключены соответственно к второму и первому входам тактовых импульсов устройства, а вторые входы - к нулевым выходам четвертого и третьего триггеров соответственно, единичные входы которых соединены с выходами неисправности четвертого и третьего блоков памяти соответственно, нулевые входы третье го и четвертого триггеров соединены с выходами неисправности третьего и четвертого блоков памяти соответственно, информационные выходы которых соединены соответственно с пер" вым и вторым входами блока элементов ИЛИ.4На Фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема первого (второго) коммутатора; на фиг, 3 - Функциональная схема первого (второго) блока памяти; на фиг. 4 - Функциональная схема третьего (четвертого) блока памяти; на993261 ки, запоминающее устройство 81,сумматор 82 по модулю два и элементИ 83. Блок 84 элементов И-ИЛИ (фиг.5) содержит В элементов И-ИЛИ. Блокэлементов ИЛИ (Фиг.,б) содержит .Еэлементов ИЛИ 85 - 1, 85 - 2, ,.,85 - ЕПервый (второй) регистр 7(8) (фиг. 7) содержит А триггеров86 - 1, 86 - 2,86 - А. Обозна,чения входов и выходов элементов нафиг. 2 . - 7 соответствует обозначениямфигуры 1,Устройство работает следующим юбразом.В исходном состоянии при отсутствии неисправностей в блоках 16,. 17,19 и 20 на соответствующих их выходах58, 63, 64 и 67 значение сигнала рав"но логическому нулю, все триггеры26, 29, 30 и 31 находятся в единичном состоянии в регистре 7 (8) записан адрес А адресной микрокоманиды, подлежащей считыванию, в регист-ре 21 (24) записан адрес А операционной микрокоманды, подлежащей считыванию из блоков 19 или 20, коммута"торы 1 и 2 заблокированы сигналамис нулевых выходов триггеров 26 и 29.На входы 34 и 33 устройства поочередно поступают тактовые импульсы. Таккак триггер 26 (29) находится в еди"ничном состоянии, то сигналом с егоединичного выхода разрешается прохождение тактового импульса с входа34 (33) устройства через элемент И9 (12) и далее через элемент ИЛИ15 (18) на считывающий вход 50 (53)блока 16 (17) памяти, в результатечего происходит считывание адресной:микрокоманды по адресу А, записанному в регистре 7 (8), и ее запись в регистрах 21 (24) и 8 (7)Одновременно с выхода элементаИЛИ.15.(18) через элемент ИЛИ 28 (27)импульс отпирает первую: группу вхохов блока элементов И-ИЛИ 32, в,результате чего адрес А поступает1на адресные входы 55 и 5 б.блоков19 и 20Так как элемент И 3 (6) открытсигналом с единичного выхода триггера 30 (31), то в этот момент на.выход 54 (57) блока 19 (20) черезоткрытый: элемент И 3.(б) и,элементИЛИ 13 (14) поступает тактовый импульс с входа 34 (33) устройства.Этим самым разрешается считывание изблока 19 (20). Считываемая операционная микрокоманда с.выхода 65(бб)блока 19(20) через элемент И-ИЛИ25.поступает на выход 68 устройства.При считывании адресной микроко"манды из блока.16 (17) адРес А+операционной микрокоманды, считывание которой. производится в следующемтакте .работы .устройства, с выхода59 (62),поступает .в )егистр 21 (22):где запоминается. фнг, 5 - функциональная схема блокаэлементов И-ИЛИ 1 на фиг. 6 - Функцно.нальная схема блока элементов ИЛИ;на фиг, 7 - Функциональная схемарегистра,Устройство (Фиг. 1) содержит второй и. первый коммутаторы 1 и 2, седьмой 3, девятый 4, десятый 5 и восьмой б элементы И, второй 7 и первый,8.регистр, первый 9,Третий" 10, четвертый 11 и второй 12 элементы И, пя Отый 13 и шестой 14 элементы ИЛИ, первый элемент ИЛИ 15, первый и второйблоки 16 и 17 памяти, второй элементИЛИ 18, третий и четвертый блоки 19и 20 памяти, четвертый регистр 21,шестой 22 и пятый 23 элементы И, третий регистр 24, блок 25 элементов ИЛИ,первый триггер 26, четвертый 27 и.третий 28 элементы ИЛИ; второй 29,третий 30 и четвертый 31 триггеры,блок элементов И-ИЛИ 32, второй ипервый входы ЗЗ и 34 устройства, второй и первый управляющие входы 35:и Эб второго коммутатора, его информационный вход 37 информационныйвход 38 первого коммутатора, первый и второй управлякваие входы 39и 40 первого коммутатора, второй и первыйвходы 41 и 42 регистра 7,установочныевходы 43 и 44 соответственно второго и первого регистров, первый и ЗОвторой входы 45 и 46 первого регистра,выход 47 первого элемента И, выходы48 и 49 второго и первого регистровсоответственно, вход 50 считыванияпервого блока. памятиадресные входы 3551 и.52 первого и второго блоковпамяти соответственно,.входы 53 и54 считывания второго и третьегоблоков памяти соответственно, адресные входы 55 и 56 третьего и четвер Отого блоков памяти соответственно,вход 57.считывания четвертого блока памяти, выход 58 неисправности первого блока памяти, второй и первый .выходы 59 и 60 первого блока памяти, 45первый и второй выходы 61 и 62 второго блока памяти, выходы 63 и 64неисправности соответственно второгои третьего блоков памяти, информационные выходы 65.и бб соответственно.третьего.и четвертого блоков памяти,выход 67 неисправности .четвертого.блока памяти, выход 68 устройства,:единичный выход 69 первого триггера,выход 70 .четвертого регистра,.входы71.и 72 блока элементов И-ИЛЙ, выход73 третьего регистра.единичный вы-.ход 74 второго триггера.Первый. (второй) коммутаторАдрес Ад следующей адресной микрокоманды с выхода 60 (61) блока 16 (17) подается на регистр 8 (7).Далее поступает тактовый импульс на вход 33 (34) устройства. При этом оно функционирует аналогично описан ному выше, осуществляя считывание микрокоманд из блоков 17 и 20.При отказе блока 16 (17) на его выходе 58 (63) появляется единичный сигнал,. который подтверждает единич О ,ное состояние триггера 29 (26) и уста. навливает триггер 26 (29) в нулевое состояние. Нулевым сигналом с единичного выхода 69 (74 триггера запрещается поступление тактовых импуль 5 сов с входа 34(33) устройства через элемент И 9 (12) на вход 50 (53) бло-. ка 16 (17). Этим же сигналом запрещается прохождение информации из регистра 21 (24) через блок элементов ИИЛИ 32 на адресные входы 55 и 56 блоков 19 и 20. Тем самым запрещается дальнейшее использование информации, поступившей из исправного блока 16 (17) в регистр 21 (24). Одновременно сигналом е выхода 58 (63) блока 16 25 (17) в регистре 8 (7) устанавливается фиксированный адрес той ячейки памяти блока 17 (16), с которой начинается микропрограмма в режиме функционирования с одним исправным блоком памя.30 ти (Функционирование по усеченному, алгоритму, реализация диагностической микропрограммы и т,п. ). Единичным сигналом с нулевого выхода триггера 26 (29) открывается элемент И 11 (10) 35 для подачи через элемент ИЛИ 18 (15) тактовых импульсов с входа 34 (33) устройства на вход 53 (50) блока 17 (16) памяти. В результате считывания микрокоманд из исправного блока 17 (16) производится по сигналам как с входа. 33, так и с входа 34 устройства, т.е. в два раза чаще, чем при работе с исправными блоками 16 и 17.Кроме этого, единичным сигналом с 45 нулевого выхода триггера "б (29) происходит разблокировка коммутатора 2 (1)Считывание микрокоманд из блока 17 (16) при этом происходит анало гично вышеописанному. Адрес следующей адресной микрокоманды, считанной с выхода 61 (60) исправного блока 17 (16), поступает на .вход 42 (45) регистра 7 (8) и через 55 разблокированный коммутатор 2 (1) исправного блока 17 (16) поступает в регистр 8 (7)По этому адресу производится считывание очередноймикрокоманды и т.д. 60Адрес операционной микрокоманды с выхода 62 (59) исправного блока 17 (16) поступает в регистры 24 (21), где запоминается. Каждым импульсом на выходе элемента ИЛИ 18.открывается элемент И 23 (22), от крытый по другому входу единичнымсигналом с нулевого выхода триггера26 (29), Сигналом с выхода элемента И 23 (22) через элемент ИЛИ 28(27) открывается для прохожденияинформации из регистра 24 (21) первая группа входов элемента И-ИЛИ 32,в результате чего на адресные входы55 и 56 блоков 19 и 20 поступают адреса операционных микрокоманд.Если.в процессе функционированияв одноканальном режиме, например,при работе с.одним исправным бло-.ком 17 (16) обнаружен отказ этого блока,то на выходе неисправности 63 (58)появляется сигнал, который опрокидывает триггер .26 (29) в единичное,а триггер 29 (26) в нулевое состояние, тем самым устройство переводится в одноканальный режим работы сранее отключенным блоком 16 (17).Если причиной его отключения является отказ одной из ячеек памяти либосбой в нем, то устройство продолжаетфункционирование, считывая микрокоманды из него. Если же этой причинойявляется отказ цепей считывания информации из него, то при первом жесчитывании микрокоманды устройствоаналогичнб вышеописанному переходитв режим работы с блоком 17 (16) и т.д.При появлении отказа в блоке 19(20) на его выходе 64 (67) появляетсясигнал, который подтверждает единичное состояние триггера 31 (30)и переводит триггер 30 (31) в 1нулевое состояние. Сигналом с его еди-,ничного выхода запирается элемент И 3,(5) для прохождения с входа 34 (33)устройства тактовых импульсов. Темсамым запрещается считывание микрркоманд неисправного блока 19 (20).Одновременно с этим единичным сигналомс йулевого выхода триггера 30(31) открывается для прохождениятактовых импульсов с входа. 34 (33)устройства элемент И 5 (3), с выхода которого тактовые импульсы черезэлемент ИЛИ 14 (13) поступают насчитывающий вход 57 (56) блока 20(19). Так как в это время элементИ б (4) открыт для поступления тактовых импульсов с входа 33 (34) устройства через элемент ИЛИ 14 (13)на вход 57 (56) блока, то считываниеиз исправного блока 20 (19) производится с удвоенной частотой.Если при.дальнейшем функционировании в.режиме с одним исправньи блоком 20 (19) памяти обнаружен отказ,то сигналом с его выхода 67 (64)триггер 30 переводится в единичное,а триггер 31 в нулевое состояние.Тем самым устройство переводится врежим работы с.блоком 19 (20), ранее забракованным,Если причинбй его отключения является отказ одной из ячеек памятилибо сбой в нем, то устройство прадо жает функционирование, считывая микрокоманды иэ него. Если же причиной является отказ цепей считывания информации иэ него, то при первом же считывании микрокоманды из него блок будет вновь забракован и аналогично вышеописанному устройству перейдет в режим работы с блоком 20 (19) и т.д.Предлагаемое устройство имеет, более .высокую отказоустойчивость, чем прототип. Выигрыш в отказоустойчивости можно оценить относительным выиграшемдО в вероятности откаэа ,устройства л полнительно содержит два блока па-.мятидва регистра, два триггера,восемь элементов И, шесть элементов ИЛИ н блок элементов И-ИЛИ, причем первые входы третьего и четвер-.5 того элементов И соединены соответственно с вторым и первым входамнтактовых импульсов устройства вторые входы третьего и четвертого элементов И соединены с нулевыми выхо О дами второго и первого триггеровсоответственно, а выходы соединеныс первыми входами соответственнопервого и второго элементов ИЛИ, вторые входы которых соединены с выходами соответственно первого и второго элементов И, а выходы первого ивторого элементов ИЛИ соединены свходами считывания соответственнопервого и второго блоков памяти,с первыми входами соответственнотретьего и четвертого элементов ИЛИ,вторые входы которых соединены с выходами пятого и шестого элементов Исоответственно, первые входй кото рых соединены с выходами второго и .первого элементов ИЛИ соответственно,вторые входы пятого и шестого элементов И соединены с нулевыми выхбдами первого и второго триггеровсоответственно, единичные входы котоЗ 0 рых соединены с выходами неисправности второго и первого блоков памятисоответственно, операционые выходыкоторых соединены с информационнымивходами соответственно третьего и35 четвертого регистров, информационные выходы которых подключены соответственно к первому и второму вхоформула изобретения. Микропрограммное устройство управления, содержащее два блока памяти, два коммутатора, два регистра, два элемента ИЛИ, два триггера, два элемента И, блок элементов ИЛИ,причем адресные выход,первого и второго блоков памяти соединены с.первыми информационными входами .соответственно первого и второго регист ров, первые выходы которых соединены с адресными входами второго и первого блоков памяти соответственно, причем установочные входы первого и второго регистров соединены е выходами неисправности первого и второго блоков памяти соответственно, информационные входы первого и второго регистров соединены с выходами пер-. вого,и второго коммутатОров соответственно, первые управляющие входы которых соединены соответствеяно с первым и вторым входами тактовых импульсов устройства, ииформационййе входы первого и второго коммутаторов соединены с вторыми выходами второго и первого регистров соответственно, вторые управляющие входы первого и второго коммутаторов соединены .с нулевыми выходами первого и второго триггеров соответственно, единичные выходы которых соединены с первыми входами первого и второго эле,ментов и соответственно, вторые входы которых соединены соответственно с первым и вторым входами тактовых импульсов устройства, выход блока .элементов ИЛИ подключен к операционному выходу устройства, .о т л ич а ю щ е е с я тем, что, с целью повышения отказоустойчивости, до 40 45 50 55 60 Р.-Р. 4 Р О%"5-7(ф,4-Ргде Р и Р - вероятности безотказ, ной работы предлагаемого устройства и прототипа соответственно.Выиграш в объеме оборудования находится в пределах 15-40. дам блока элементов И-ИЛИ, третийи четвертый входы которого соединеныс единичными выходами соответственнопервого и второго триггеров, нулевыевходы которых соединены с выходаминеисправности соответственно первого и второго блоков памяти, выходытретьего и четвертого элементов ИЛИподключены к пятому и шестому входам соответственно блока элементовИ-ИЛИ,выход которого подключен к адресным входам третьего и четвертого блоков памяти, входы считываниякоторых соединенй с выходами соответственно пятого и шестого элемен"тов ИЛИ, первые входы которых соединены с выходами седьмого и восьмо. го элементов И, первые входы которых соединены соответственно с пер-,вым и вторым входами тактовых импульсов устройства, а вторые входы,с единичными выходами соответственно третьего и четвертого триггеров, к вторым входам пятого и шестого элементов ИЛИ подключены выходы соответственно девятого и десятогоэлементов И, первые входы которыхподключены соответственно к второму и первому. входам тактовых импульсов устройства, а вторые входы - к нулевым выходам четвертого и третьего триггеров соответственно, единичные входы которых соединены с выходами неисправности четвертого и третьего блоков памяти соответственно, нулевые входы третьего и четвертого триггеров соединены с выходами неисправности третьего и четвертого блоков памяти соответственно, информационные выходы которыхсоединены соответственно с первым ивторым входами блока элементов ИЛИ.Источники информации,принятые во внимание при экспертиэе5 1. Авторское свидетельство СССРР 830383, кл. С Об Р 9/22 1981.2. Авторское свидетельство СССРМ 646333, .кл. С 06 Р 9/12, 1976Тираа 704Государстве елам иэобре Москва, ЖПодписное ного комитета СС ений и.открытий .5, Раушская наб.

СмотретьЗаявка

3334996, 02.09.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕВ АЛЕКСАНДР ПАВЛОВИЧ, ТКАЧЕВ МИХАИЛ ПАВЛОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.01.1983

Код ссылки

<a href="https://patents.su/9-993261-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для логического управления

Следующий патент: Устройство для обработки информации

Случайный патент: Устройство для измерения коэффициента гармоник