Устройство для умножения десятичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1198514

Авторы: Кожемяко, Красиленко, Мартынюк, Натрошвили, Тимченко

Текст

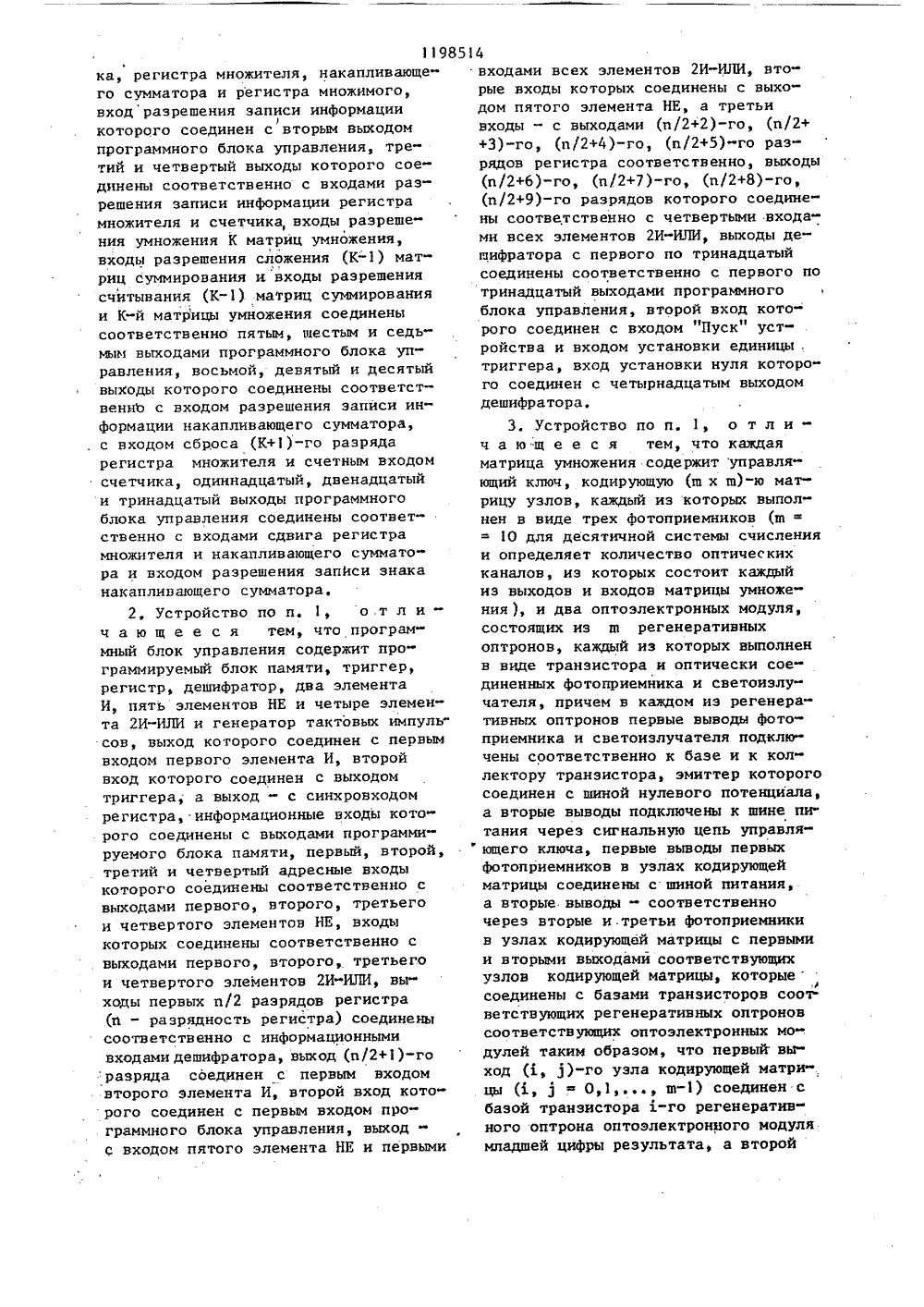

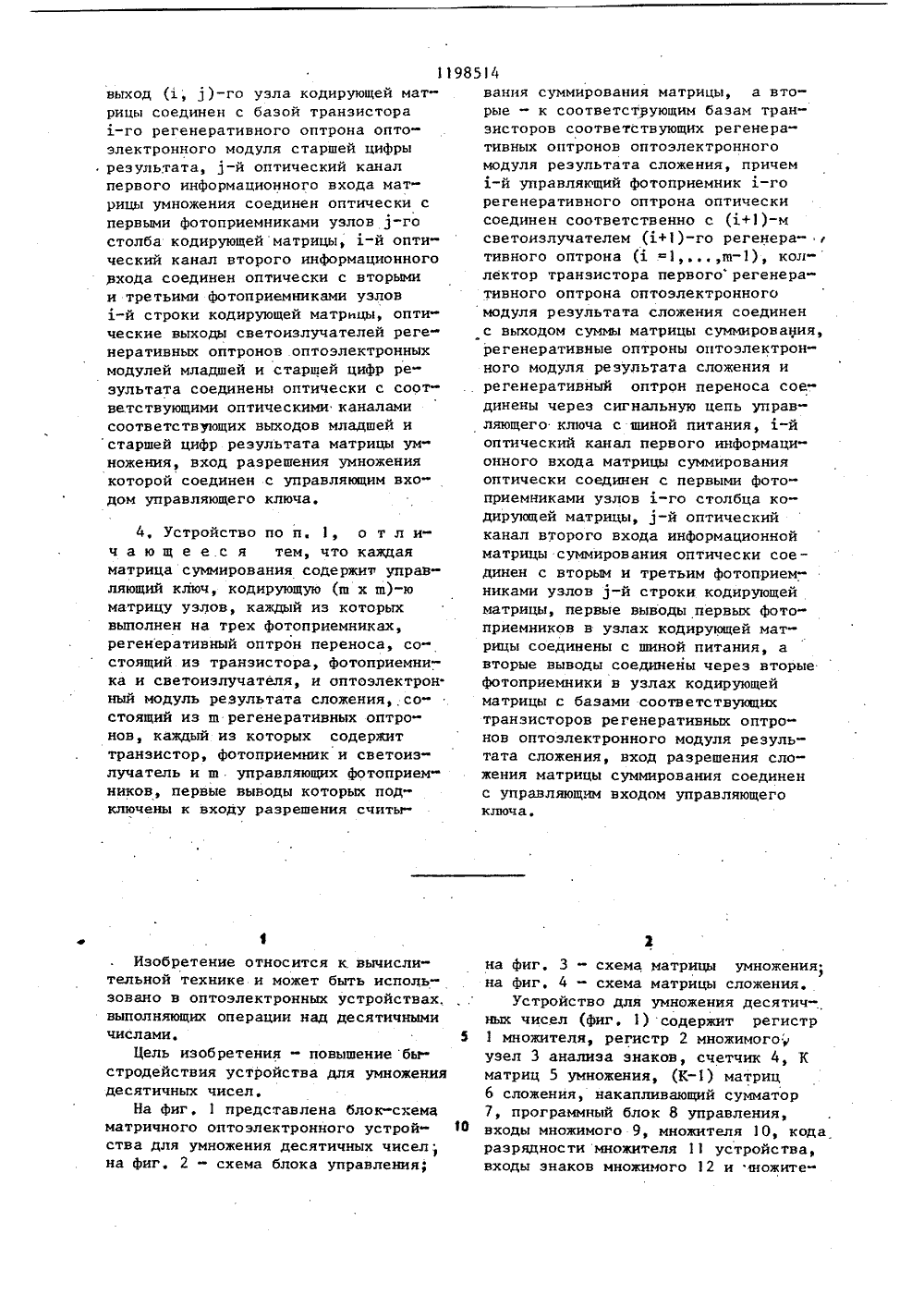

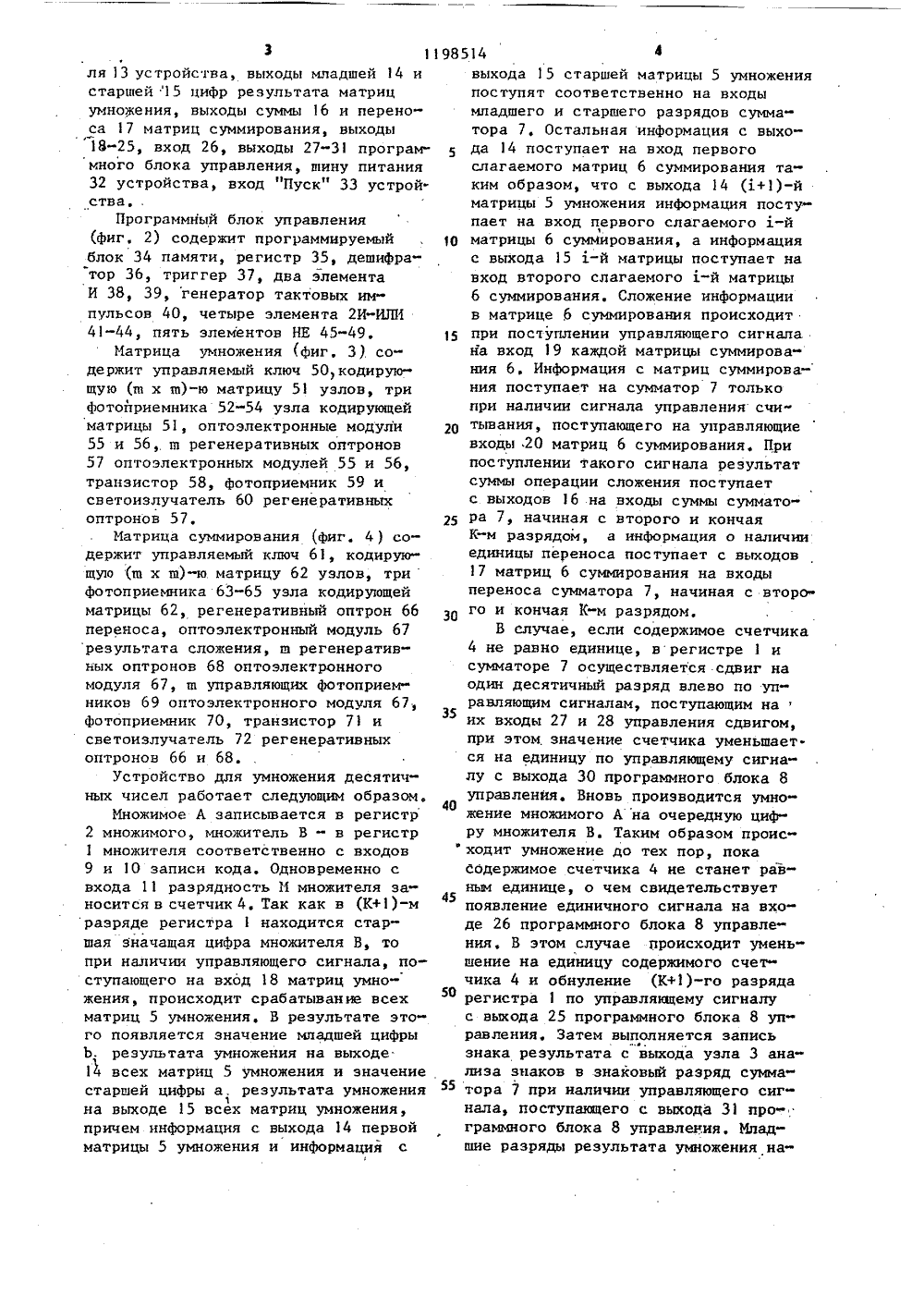

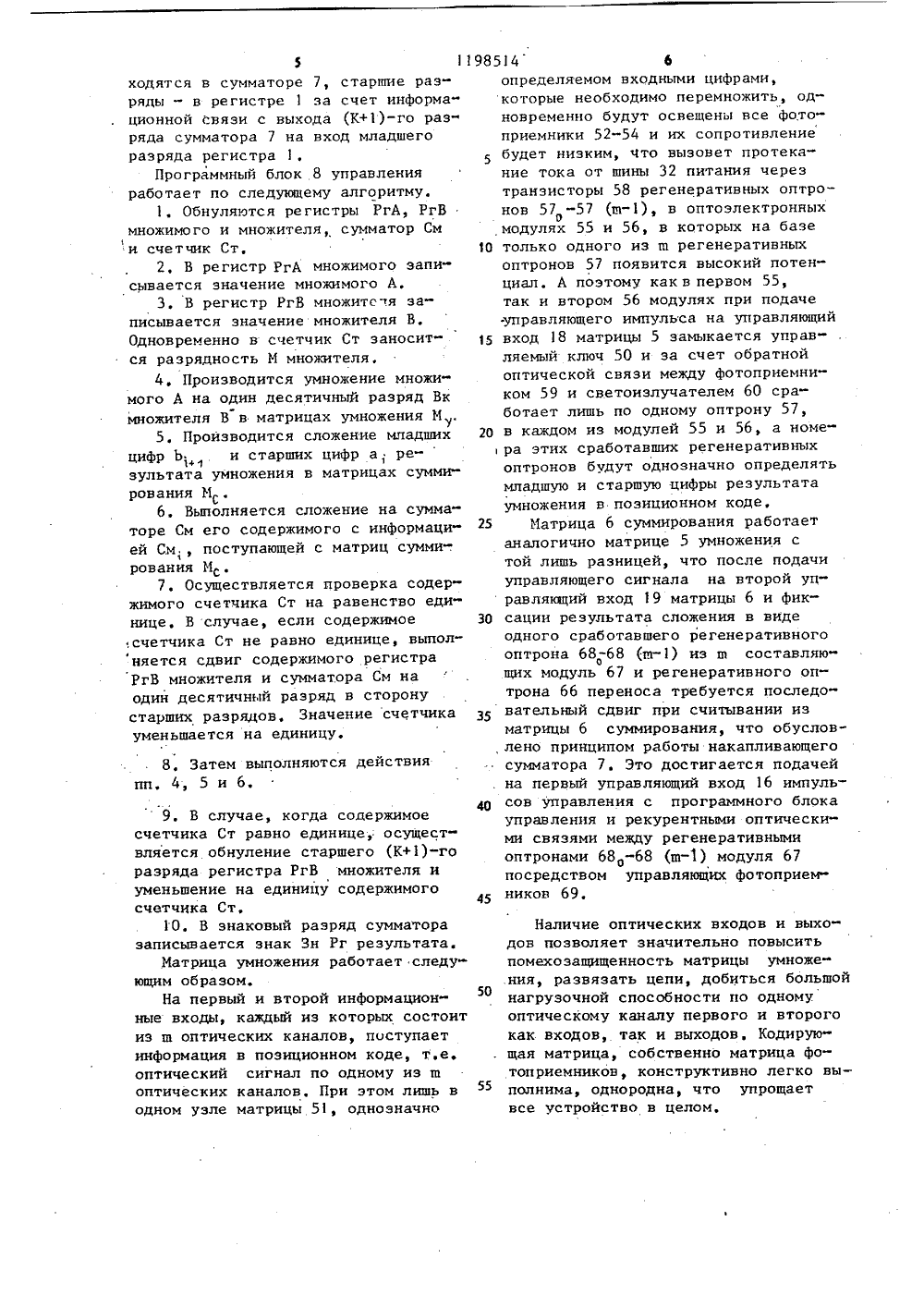

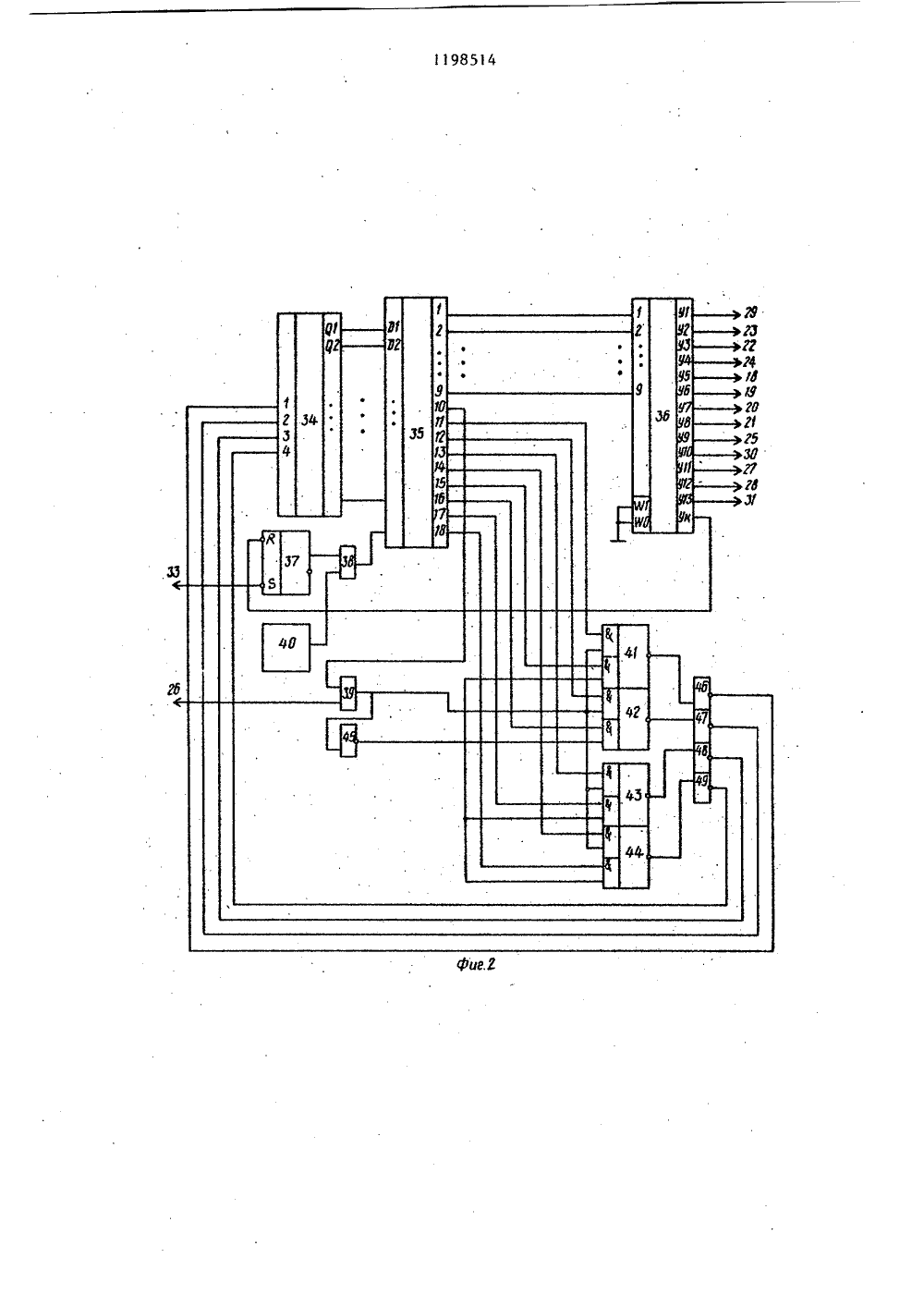

реализавычитания ктронных боростро(56) Кожем ции алгори и др.ения М ов умно исел на Изв, ву Р 3, с, свидет л, С Об десятичных ч сумматорах,ение, 1976,Авторское 9 1016780, коптоэл овПр 62-65, льство Г 7/49 81,егистрнный ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(54 )(57 ) 1, УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ, содержащее регистр множимого, регистр множителя, накапливающий сумматор, узел анализа знаков и счетчик, причем входы множителя и множимого устройства соединены соответственно с информационными входами регистров множителя и множимого, выходы знаковых раз- рядов которых соединены с первым и вторым входами узла анализа знаков, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены К матриц умножения (К - разрядность множителя и множимого), (К) матриц суммирования и программный блок управления, причем разрядные выходы регистра множимого соединены с первыми информационны ми входами К матрицы умножения, вторые информационные входы которых соединены с (К+1)-и выходом ра множителя, (К+1)-й информацио вход которого соединен с К-м выходомрегистра множителя, информационныйвход младшего разряда которого соеди"нен с выходом (К+1)-го разряда накапливающего сумматора, вход (К+1)-горазряда которого соединен с выходом старшей цифры результата умножения К-й матрицы умножения, выходстаршей цифры результата умножения-й матрицы умножения соединен спервым информационным входом 1-йматрицы суммирования ( = 1. К)второй информационный вход )-й матрицы суммирования соединен с выходом младшей цифры результата умножения Ц)-й.матрицы умножения= щ= 2, ЗК), выход младшей цифрырезультата умножения первой матрицы,.умножения соединен с информационным Сфвходом младшего разряда накапливающего сумматора, информационный вход Язнакового разряда которого соединенс выходом блока анализа знаков, вход)-го разряда первого слагаемого накапливающего сумматора соединен с выходом суммы 1.-й матрицы суммированиясоответственно, выход переноса которой соединен с выходом )-го разрядавторого слагаемого накапливающегосумматора, входы знака множимого,знака множителя и кода разрядностимножителя устройства соединены соответственно с входами знаковых разрядов регистров множимого и множителя фЭи информационным входом счетчика, шина питания устройства соединена сшиной питания всех матриц умноженияи суммирования, выход счетчика соединен с первым входом программного блока управления, первый выход которого соединен с входами сброса счетчи 11985ка, регистра множителя, накапливающего сумматора и регистра множимого,вход разрешения записи информациикоторого соединен с вторым выходомпрограммного блока управления, третий и четвертый выходы которого соединены соответственно с входами разрешения записи информации регистрамножителя и счетчика, входы разрешения умножения К матриц умножения,входы разрешения сложения (К) матриц суммирования и входы разрешениясчитывания (К"1) матриц суммированияи К-й матрицы умножения соединенысоответственно пятым, шестым и седьмым выходами программного блока управления, восьмой, девятый и десятыйвыходы которого соединены соответственнЬ с входом разрешения записи информации накапливающего сумматора,с входом сброса (К+1)-го разрядарегистра множителя и счетным входомсчетчика, одиннадцатый, двенадцатыйи тринадцатый выходы программногоблока управления соединены соответственно с входами сдвига регистрамножителя и накапливающего сумматора и входом разрешения записи знаканакапливающего сумматора,2. Устройство по и. 1, о т л и -ч а ю щ е е с я тем, что программный блок управления содержит программируемый блок памяти, триггер,регистр, дешифратор, два элементаИ, пять элементов НЕ и четыре элемента 2 И-ИЛИ и генератор тактовых импуль"сов, выход которого соединен с первымвходом первого элемента И, второйвход которого соединен с выходомтриггера, а выход - с синхровходомрегистра, информационные входы которого соединены с выходами программируемого блока памяти, первый, второй,третий и четвертый адресные входыкоторого соединены соответственно свыходами первого, второго, третьегои четвертого элементов НЕ, входыкоторых соединены соответственно свыходами первого, второго, третьегои четвертого элементов 2 И-ИЛИ, выходы первых и/2 разрядов регистра(и - разрядность регистра) соединенысоответственно с информационнымивходами дешифратора, выход (и/2+1)-горазряда соединен с первым входомвторого элемента И, второй вход которого соединен с первым входом программного блока управления, выходс входом пятого элемента НЕ и первыми 14входами всех элементов 2 И-ИЛИ, вторые входы которых соединены с выходом пятого элемента НЕ, а третьивходы - с выходами (и/2+2)-го, (и/2+(и/2+9)-го разрядов которого соединены соответственно с четвертыми входами всех элементов 2 И-ИЛИ, выходы дещифратора с первого по тринадцатыйсоединены соответственно с первого потринадцатый выходами программногоблока управления, второй вход которого соединен с входом "Пуск" устройства и входом установки единицы .триггера, вход установки нуля которо"го соединен с четырнадцатым выходомдешифратора,3, Устройство по и, 1, о т л и -ч а ю "щ е е с я тем, что каждаяматрица умножения содержит управляющий ключ, кодирующую (ш х в)-ю матрицу узлов, каждый из которых выполнен в виде трех фотоприемников (в1 О для десятичной системы счисления и определяет количество оптических каналов, иэ которых состоит каждый из выходов и входов матрицы умножения ), и два оптоэлектронных модуля, состоящих из в регенеративных оптронов, каждый из которых выполнен в виде транзистора и оптически соединенных фотоприемника и светоизлучателя, причем в каждом из регенеративных оптронов первые выводы фотоприемника и светоиэлучателя подключены соответственно к базе и к коллектору транзистора, эмиттер которогосоединен с шиной нулевого потенциала, а вторые выводы подключены к шине пи" тания через сигнальную цепь управля"ющего ключа, первые выводы первых фотоприемников в узлах кодирующейматрицы соединены с шиной питания,а вторые выводы - соответственночерез вторые и.третьи фотоприемникив узлах кодирующей матрицы с первымии вторыми выходами соответствующих узлов кодирующей матрицы, которые)1 соединены с базами транзисторов соот. ветствующих регенеративных оптронов соответствующих оптоэлектронных модулей таким образом, что первый выход (х 1)-го узла кодирующей матрицы (3.1 0,1 в) соединен с базой транзистора ь-го регенеративного оптрона оптоэлектронного модуля младшей цифры результата, а второй1 выход (д, 1)-го узла кодирующей матрицы соединен с базой транзистора д-го регенеративного оптрона оптоэлектронного модуля старшей цифры результата, 1-й оптический канал первого информационного входа матрицы умножения соединен оптически с первыми фотоприемниками узлов 1-го столба кодирующей матрицы, 1-й оптический канал второго информационного ,входа соединен оптически с вторыми и третьими фотоприемниками узлов д-й строки кодирующей матрицы, оптические выходы светоизлучателей реге неративных оптронов оптоэлектронных модулей младшей и старшей цифр результата соединены оптически с соответствующими оптическими каналами соответствующих выходов младшей и старшей цифр результата матрицы умножения, вход разрешения умножения которой соединен с управляющим входом управляющего ключа,4, Устройство по п. 1, о т л ич а ю щ е е.с я тем, что каждая матрица суммирования содержит управляющий ключ, кодирующую (ш х ш)-ю матрицу узлов, каждый из которых выполнен на трех фотоприемниках, регенеративный оптрон переноса, состоящий из транзистора, фотоприемника и светоиэлучателя, и оптоэлектрон. ный модуль результата сложениясостоящий из ш регенеративных оптронов, каждый из которых содержит транзистор, фотоприемник и светоизлучатель и ш управляющих фотоприемников, первые выводы которых подключены к входу разрешения считы 198514вания суммирования матрицы, а вторые - к соответствующим базам транзисторов соответствующих регенеративных оптронов оптоэлектронного модуля результата сложения, причем 1-й управлякщий фотоприемник д-горегенеративного оптрона оптическисоединен соответственно с (1+1)-м светоизлучателем (1+1)-го регенеративного оптрона (1 .1ш), коллектор транзистора первого регенеративного оптрона оптоэлектронного модуля результата сложения соединенс выходом суммы матрицы суммирования, регенеративные оптроны оптоэлектронного модуля результата сложения ирегенеративный оптрон переноса соединены через сигнальную цепь управляющего ключа с шиной питания, д-й оптический канал первого информационного входа матрицы суммирования оптически соединен с первыми фотоприемниками узлов 1.-го столбца кодирующей матрицы, 1-й оптический канал второго входа информационной матрицы суммирования оптически соединен с вторым и третьим фотоприемниками узлов 1-й строки кодирующейматрицы, первые выводы первых фотоприемников в узлах кодирующей матрицы соединены с шиной питания, а вторые выводы соединены через вторыефотоприемники в узлах кодирующей матрицы с базами соответствующих транзисторов регенеративных оптронов оптоэлектронного модуля результата сложения, вход разрешения сложения матрицы суммирования соединен с управляющим входом управляющего ключа,10 Изобретение относится к,вычислительной технике и может быть использовано в оптоэлектронных устройствах.выполняющих операции над десятичнымичислами,Цель изобретения - повышение быстродействия устройства для умножениядесятичных чисел,На фиг. 1 представлена блок-схемаматричного оптоэлектронного устройства для умножения десятичных чиселна фиг, 2 - схема блока управления; на фиг, 3 - схема матрицы умножения на фиг, 4 - схема матрицы сложения.Устройство для умножения десятичных чисел (фиг, 1) содержит регистр 1 множителя, регистр 2 множимогоу узел Э анализа знаков, счетчик 4, К матриц 5 умножения, (К) матриц 6 сложения, накапливающий сумматор 7, программный блок 8 управления, входы множимого 9, множителя 10, кода разрядности множителя 11 устройства, входы знаков множимого 12 и 1 ножите 3 1ля 13 устройства, выходы младшей 14 истаршей 15 цифр результата матрицумножения, выходы суммы 16 и переноса 17 матриц суммирования, выходы18-25, вход 26, выходы 27-3 програм"много блока управления, шину питания32 устройства, вход "Пуск" 33 устройства, .Программный блок управления(фиг. 2) содержит программируемыйблок 34 памяти, регистр 35, дешифратор 36, триггер 37, два элементаИ 38, 39, генератор тактовых импульсов 40, четыре элемента 2 И-ИЛИ41-44, пять элементов НЕ 45-49.Матрица умножения (Фиг, 3). содержит управляемый ключ 50,кодирующую (щ х тп)-ю матрицу 51 узлов, трифотоприемника 52-54 узла кодирующейматрицы 51, оптоэлектронные модули55 и 56 ш регенеративных оптронов57 оптоэлектронных модулей 55 и 56,транзистор 58, фотоприемник 59 исветоизлучатель 60 регенеративныхоптронов 57,Матрица суммирования (фиг, 4 ) содержит управляемый ключ 61, кодирующую (ш х ш)-ю матрицу 62 узлов, трифотоприемника 63-65 узла кодирующейматрицы 62, регенеративный оптрон 66переноса, оптоэлектронный модуль 67результата сложения, ш регенеративных оптронов 68 оптоэлектронногомодуля 67, ш управляющих фотоприемников 69 оптоэлектронного модуля 67,фотоприемник 70, транзистор 71 исветоизлучатель 72 регенеративныхоптронов 66 и 68.Устройство для умножения десятичных чисел работает следующим образом,Множимое А записывается в регистр2 множимого, множитель В - в регистр1 множителя соответственно с входов9 и 1 О записи кода. Одновременно свхода 11 разрядность М множителя заносится в счетчик 4. Так как в (К+1)-мразряде регистра 1 находится старшая значащая цифра множителя В, топри наличии управляющего сигнала, поступающего на вход 18 матриц умножения, происходит срабатывание всехматриц 5 умножения, В результате этого появляется значение младшей цифрыЬ, результата умножения на выходе 14 всех матриц 5 умножения и значениестаршей цифры а. результата умножения1на выходе 15 всех матриц умножения,причем информация с выхода 14 первойматрицы 5 умножения и информация с198514 содержимое счетчика 4 ие станет равным единице, о чем свидетельствуетпоявление единичного сигнала на входе 26 программного блока 8 управления, В этом случае происходит уменьшение на единицу содержимого счетчика 4 и обнуление (К+1)-го разрядарегистра 1 по управлякщему сигналус выхода 25 программного блока 8 управления, Затем выполняется записьзнака результата с выхода узла 3 анализа знаков в знаковый разряд сумма тора 7 при наличии управляющего сигнала, поступающего с выхода 31 программного блока 8 управления. Младшие разряды результата умножения на 5 0 5 20 25 30 35 40 выхода 15 старшей матрицы 5 умножения поступят соответственно на входы младшего и старшего разрядов сумматора 7, Остальная информация с выхода 14 поступает на вход первого слагаемого матриц 6 суммирования таким образом, что с выхода 14 (1+1)-й матрицы 5 умножения информация посту " пает на вход первого слагаемого д-й матрицы 6 суммирования, а информация с выхода 15 -й матрицы поступает на вход второго слагаемого 1-й матрицы 6 суммирования. Сложение информации в матрице 6 суммирования происходит при поступлении управляющего сигнала на вход 19 каждой матрицы суммирования 6, Информация с матриц суммирова- ния поступает на сумматор 7 только при наличии сигнала управления счи" тывания, поступающего на управляющие входы 20 матриц 6 суммирования. При поступлении такого сигнала результат суммы операции сложения поступает с выходов 16 на входы суммы сумматора 7, начиная с второго и кончая К-м разрядом, а информация о наличии единицы переноса поступает с выходов 17 матриц 6 суммирования на входы переноса сумматора 7, начиная с второ го и кончая К-м разрядом.В случае, если содержимое счетчика 4 не равно единице, в регистре 1 и сумматоре 7 осуществляется сдвиг на один десятичный разряд влево по управляющим сигналам, поступающим на их входы 27 и 28 управления сдвигом, при этом, значение счетчика уменьшается на единицу по управляющему сигналу с выхода 30 программного блока 8 управления. Вновь производится умножение множимого Ана очередную цифру множителя В, Таким образом происходит умножение до тех пор, пока5ходятся в сумматоре 7, старшие разряды - в регистре 1 за счет информационной связи с выхода (К+1)-го разряда сумматора 7 на вход младшегоразряда регистра 1,Программный блок 8 управленияработает по следующему алгоритму.1, Обнуляются регистры РгА, РгВмножимого и множителя, сумматор Сми счетчик Ст,2, В регистр РгА множимого записывается значение множимого А.3. В регистр РгВ множителя записывается значение множителя В.Одновременно в счетчик Ст заносится разрядность М множителя.4, Производится умножение множимого А на один десятичный разряд Вкмножителя В в матрицах умножения М,.5, Производится сложение младшихцифр Ь;, и старших цифр а, результата умножения в матрицах суммирования М6, Выполняется сложение на сумматоре См его содержимого с информацией См поступающей с матриц сумми-.рования Мс.7. Осуществляется проверка содержимого счетчика Ст на равенство единице, В случае, если содержимое,счетчика Ст не равно единице, выполняется сдвиг содержимого регистраРгВ множителя и сумматора См наодин десятичный разряд в сторонустарших разрядов, Значение счетчикауменьшается на единицу. 8, Затем выполняются действияпп, 4, 5 и б,9, В случае, когда содержимоесчетчика Ст равно единице, осуществляется обнуление старшего (К+1)-горазряда регистра РгВ множителя иуменьшение на единицу содержимогосчетчика Ст,10. В знаковый разряд сумматоразаписывается знак Зн Рг результата.Матрица умножения работает следующим образом.На первый и второй информационные входы, каждый из которых состоитиз ш оптических каналов, поступаетинформация в позиционном коде, т,е,оптический сигнал по одному из шоптических каналов, При этом лишь водном узле матрицы 51, однозначно198514 6 1 О 15 20ра этих сработавших регенеративных 35 ников 69. 45 25 30 50 55 определяемом входными цифрами,которые необходимо перемножить, одновременно будут освещены все фотоприемники 52-54 и их сопротивление будет низким, что вызовет протекание тока от шины 32 питания черезтранзисторы 58 регенеративных оптронов 57 -57 (ш), в оптоэлектронныхмодулях 55 и 56, в которых на базе только одного из ш регенеративных оптронов 57 появится высокий потенциал, А поэтому как в первом 55,так и втором 56 модулях при подаче-управляющего импульса на управляющийвход 18 матрицы 5 замыкается управляемый ключ 50 и эа счет обратнойоптической связи между фотоприемником 59 и светоизлучателем 60 сработает лишь по одному оптрону 57,в каждом из модулей 55 и 56, а номеоптронов будут однозначно определять младшую и старшую цифры результата умножения в позиционном коде,Матрица 6 суммирования работает аналогично матрице 5 умножения с той лишь разницей, что после подачи управляющего сигнала на второй управлякзций вход 19 матрицы 6 и фиксации результата сложения в виде одного сработавшего регенеративного оптрона 68-68 (ш) из ш составляющих модуль 67 и регенеративного оптрона 66 переноса требуется последовательный сдвиг при считывании изматрицы 6 суммирования, что обусловлено принципом работы накапливающего сумматора 7, Это достигается подачей на первый управляющий вход 16 импульсов управления с программного блока управления и рекурентными оптическими связями между регенеративными оптронами 68 О(ш) модуля 67 посредством управляющих фотоприемНаличие оптических входов и выходов позволяет значительно повысить помехозащищенность матрицы умножения, развязать цепи, добиться большой нагрузочной способности по одному оптическому каналу первого и второго как входов, так и выходовКодирующая матрица, собственно матрица фотоприемников, конструктивно легко выполнима, однородна, что упрощает все устройство в целом, 11985141198516 Составитель Е. Захарченкоактор М,Дылын 1 ехред Л.Иартяшова Корректор, 0 а Тираж 709 ПодписноеГосударственного комитета СС делам изобретений и открытий Москва, Ж, Раушская наб.,Заказ 77 ВНИИПИ по 035,

СмотретьЗаявка

3698193, 01.02.1984

ВИННИЦКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КОЖЕМЯКО ВЛАДИМИР ПРОКОФЬЕВИЧ, МАРТЫНЮК ТАТЬЯНА БОРИСОВНА, КРАСИЛЕНКО ВЛАДИМИР ГРИГОРЬЕВИЧ, НАТРОШВИЛИ ОТАР ГЕОРГИЕВИЧ, ТИМЧЕНКО ЛЕОНИД ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: десятичных, умножения, чисел

Опубликовано: 15.12.1985

Код ссылки

<a href="https://patents.su/9-1198514-ustrojjstvo-dlya-umnozheniya-desyatichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения десятичных чисел</a>

Предыдущий патент: Устройство для умножения двоично-десятичных цифр

Следующий патент: Устройство для возведения в квадрат

Случайный патент: Способ изготовления трубного пучка теплообменника