Устройство для выравнивания порядков чисел, представленных в системе остаточных классов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 781812

Авторы: Колесницкий, Червяков

Текст

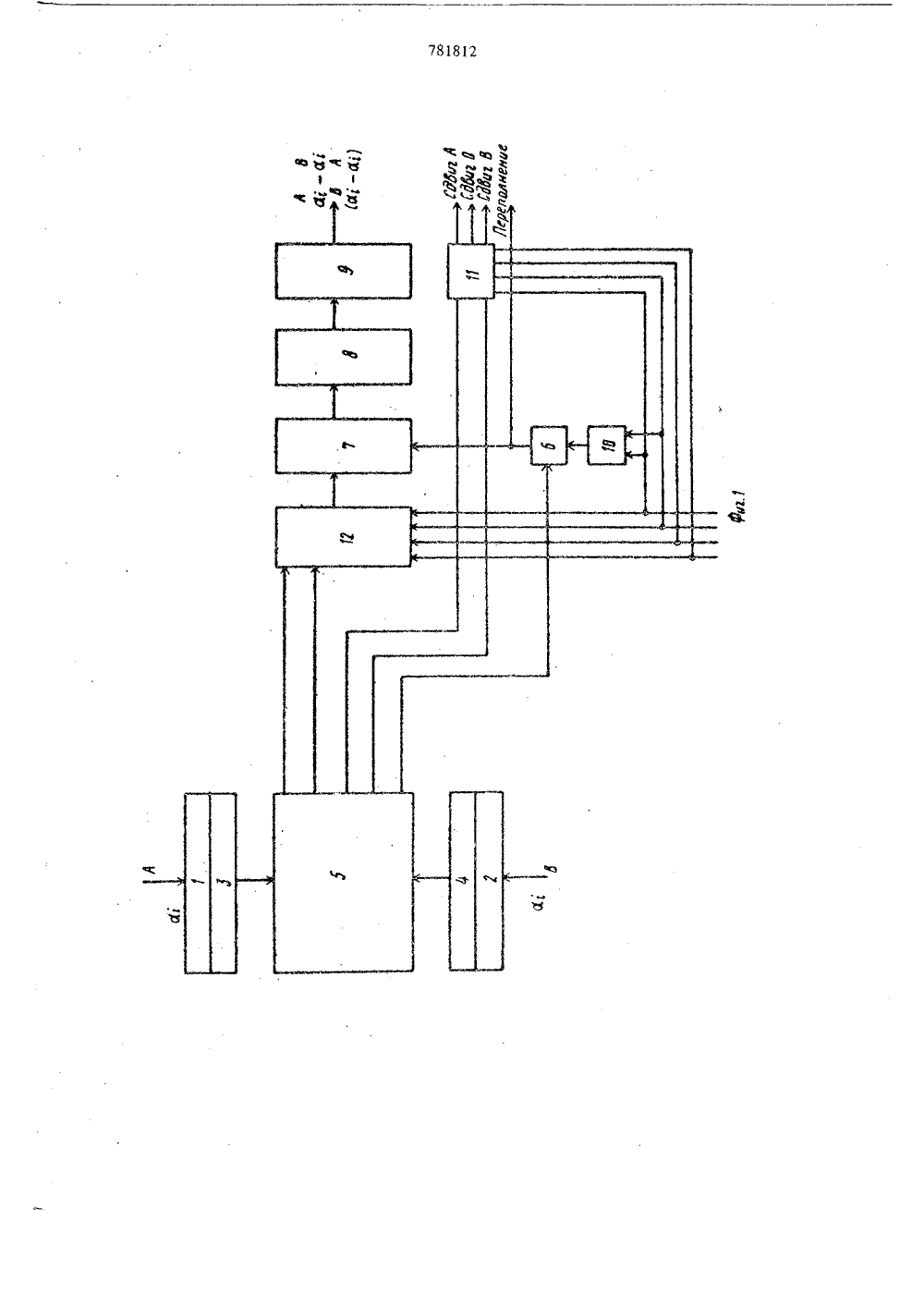

Союз СоветскихСоциалистическихРеспублик ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВйДЕТЕЛЬСТВУ(23) Приоритет Гаеуяарстввнный какнтвт ао делак нзобрегеннй и отнрьпий(54) УСТРОЙСТВО ДЛЯ ВЫРАВНИВАНИЯ ПОРЯДКОВ ЧИСЕЛ,ПРЕДСТАВЛЕННЫХ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВИзобретение относится к в.числительнойтехнике и может быль испольэовало в арифметических устройствах различного назначения,Известно устройство для суммированияи вычитания чисел с переменным основанием,содержащее сумматоры, блок управления, ло 5гические схемы, триггеры блокировки и коррекции, счетчик констант и регистр переменнсго модуля 11.Недостатком его является большой объемооборудования и малое быстродействие,Наиболее близкое к предлагаемому изобре.тенню техническое решение - сумматор в системе остаточных классов (СОК), содержащийдва входных регистра и операционную схему,35выполненную на ферритовых сердечниках, эле.мент ИЛИ, причем каждая выходная шинаодного регистра через элемент ИЛИ и соответствующую обмотку ферритового сердечникаоперационной схемы соединена с каждой выходной шиной друтого регистра (2).Недостатком известного устройства являетсяневозможность определения энака результатасуммирования аппаратными средствами и малая 2скорость определения программными средства.Цель изобретения - повышение быстродействия,Поставленная цель достигается тем, что вустройство, содержащее регистры первого и .второго операндов, выходами соединенные совходами соответствукицих дешифраторов первого и второго операндов, выходы которыхсоединены со входами сумматора по модулюР(Р - простое число), входы регистров явля.ются входамн устройства, дополнительно введены блок анализа разности порядков, блокуправления сдвигом, шифратор, выходной регистр, элемент И, элемент. ИЛИ, элементЗАПРЕТ, причем первый и второй выходысумматора по модулю Р соединены соответственно с первым и вторым входами блокаанализа разности порядков, выход которогосоединен с первым входом элемента ЗАПРЕТ,выходом через шифратор соединенного совходом выходного регистра, выход которогоявляется выходом разности порядков устрой.ства, первый, второй, третий ичетвертый вы781812 4цы третьего и седьмого элементов И являютсяпервым входом блока, первые входы четвертого и восьмого элементов И являются вторымвходом блока, вторые входы первого, второго,третьего и четвертого элементов И группысоединены между собой и являются пятымвходом блока, вторые входы пятого и шестогоэлементов И группы соединены между собойи являются шестым входом блока, вторые вхо 10 ды седьмого, восьмого и девятого элементов Исоединены между собой и являются седьмымвходом блока, второй вход десятого элемента Игруппы является восьмым входом блока.В цифровых вычислительных машинах, рабо.тающих в позиционных системах счисления, информация представляется, как правило, дробными числами. Поэтому при сопряжении таких о- ЦВМ необходимо выбрать масштаб так, чтобы длявсех полученных масштабированных целых чи 2 О сел, употребляемых в вычислениях, их макси.мальное значение по модулю было не больше ы максимально допустимого числа,нредставленногов ЦВМ, работающих в СОК, а минимальное значение величин по модулю не меньше минимально25 допустимого, т.е. чтобы числа находились впределах выбранного диапазона. 3ходы сумматора по модулю Р соединены с соответствующими входами блока управления сдвигом, выходы которого являются выходами сдвига устройства, пятый выход сумматора по модулю Р соединен с первым входом элемента И,выход которого соединен со вторым входом элемента ЗАПРЕТ и является выходом переполнения устройства, первый, второй, третий и четвертый управляющие входы устройства соединены соответственно с пятым, шестым, седьмым и восьмым входами блока управления сдвигом и с третьим, четвер тым, пятым и шестым входами блока анализа разности порядков, седьмой вход которого соединен с пятым выходом сумматора по модулю Р, третий и четвертый управляющие вхб.ды устройства соединены со входами элемента ИЛИ, выход которого соединен со вторым вх дом элемента И, кроме того, блок анализа разности порядков содержит две группы по Р элементов ИЛИ и Р групп по два элемента И, причем выходы элементов ИЛИ первой групп являются выходами блока, выходы элементов И каждой группы соединены со входами соот ветствующих элементов ИЛИ первой группы, первые входы первых элементов И каждой группы соединены с выходами соответствующих .элементов ИЛИ второй группы, первые входы которых соединены между собой и являются первым входом блока, вторые входы элементов ИЛИ второй группы соединены между со.бой и являются вторым входом блока, вторые входы вторых элементов И всех групп соеди.иены между собой и являются седьмым входом блока, первые входы вторых элементов И35 Р.ой, (Р)-ой, (Р)-ой и (Р)-ей групп являются соответственно шестым, пятым, четвертым и третьим входами блока, вторые входы первых элементов И и первые входы вторых элементов И 1-х групп (1 = 1, 2 , Р - 4) соединены между собой и являются третьим входом блока, а также блок управления сдвигом содержит первый, второй и третий элементы ИЛИ и группу элементов И, выходы элементов ИЛИ являются выходами блока, первый, второй,45 третий, четвертый, пятый входы первого, третье. го, девятого, восьмого, пятого элементов И группы, первый и второй входы второго элемента ИЛИ соединены с первыми входами соответственно третьего и четвертого элемен.тов И группы, первый, второй, третий, четвертый, пятый входы третьего элемента ИЛИ соединены соответственно с выходами второго, четвертого, шестого, седьмого, десятого элементов И группы, первые входы первого, пятого и девятого элементов И группы являются четвертым входом блока, первые входы второго, шестого и десятого элементов И группы являются третьим входом блока, первые вхоВ связи с этим целесообразно получить цело.численные мантиссы чисел, представленные вестественной или нормальной форм соответственно в ЦВМ с фиксированной или плавающейзапятой. Полученные целые числа, представлечныев позиционной системе счисления, переводятсяв СОК. В таком случае ЦВМ, работающая в СОК,оперирует целыМи числами, полученными издробных за счет введения масштаба,Известно, что масштабирование любого дробного числа, представленного в естественной илинормальной форме, осуществляется путем сдвигаЙмантиссы влево на о разрядов, где и - количество разрядов мантиссы. Очевидно, полученный порядок масштаба мантиссы является поряд.ком числа, если информация в ЦВМ, работающейв позиционной системе счисления, представленав естественной форме, и одним из слагаемыхпорядка, в случае представления информации внормальной форме.Тогда после масштабирования число записывается в виде где М - целочисленная мантисса;/И - основание системы счисления;6+и - порядок (при естественной форме записи Й =ф О),.Таким образом, мантисса и порядок записываются целыми числами.П р и м е р 1, В естественной форме чис. ло представлено в виде 0,101101. После введе.Блок-схема устройства содержит регистрыпервого и второго операндов 1 и 2, дешифрато.ры первого и второго операндов 3 и 4, сумматор 5 по модулю Р, элемент И 6, элементЗАПРЕТ 7, шифратор 8, выходной регистр 9,элемент ИЛИ 10, блок 11 управления сдвигом,блок 12 анализа разности порядков.Блок-схема, представленная на фиг. 2, содержит элемент ИЛИ 13, первую и вторую группыэлементов ИЛИ 14 и 15, первую, вторую, третью, 1 очетвертую, пятую группы элементов И 16 - 20.В блок управления сдвигом входят группаэлементов И 21, первый, второй, третий элементы ИЛИ 22, 23, 24, элемент НЕ 25.Устройство работает следуюцим образом. 15При выполнении операции выравнивания нарегистры операндов 1 и 2 заносятся операнды4, и я, На блок 11 управления сдвигом и1,блок 12 анализа разности порядка поступает информация о знаках операндов. На элемент ИЛИ10 поступает также информация о знаках опе.рандов. С выхода регистров 1 и 2 коды операндов поступают на дешифраторы 3 и 4.С выходов дешифраторов 3 и 4 операнды,представленные в унитарном коде, подаются 25на вход сумматора по модулю Р,С выходаблока 5 сигналы поступают на вход блока 12анализа разности порядков чисел.При одновременном воздействии сигналовпервого и второго выходов сумматора 5 и сиг.налов, поступающих на входы три, четыре, пять,шесть, в блоке 12 формируется сигнал разностипорядков, который через элемент ЗАПРЕТ 7(если соответствует сигнал переполнения) поступает на вход шифратора 8. Шифратор обес.печивает преобразование унитарного кода в двоичный код. С выхода шифратора информацияв двоичном коде поступает на вход регистра 9.Одновременно с образованием результата раз.ности с третьего и четвертого выходов сумматора 5 сигналы поступают на вход блока управления сдвигом 11. При одновременном воздействии поступивших сигналов, блок 11 формиру.ет сигнал сдвига 1 сдвиг "А" сдвиг В,сдвиг "0") .45Сигнал с выхода блока 11 указывает, какуюиз мантисс нужно сдвинуть влево (сдвиг "А" -сдвигается мантисса операнда А влево; сдвиг"В" - сдвигается мантисса операнда В влево;сдвиг "О - порядки операндов А и В равны),а на сколько разрядов необходимо сдвинуть ее,указывает содержимое регистра 9. В случае, еслипорядки имеют разные знаки, возникаетпереполнение разрядной сетки. Для сигна.лизации переполнения сумматор 5 формируетсигнал на пятом выходе, который поступает наэлемент И 6 и далее на выход устройства.Видно, что для выравнивания порядков отпадает необходимость предварительного сравнива. ния порядков, что особенно важно для ЭВМ, " работающих в СОК, так как в СОК операция сравнения занимает много времени.Таким образом, операция уравнивания поряд. ков выполняется в один такт, что позволяет увеличить общую производительность вычислительной системы, работающей в СОК,Формула изобретения1. Устройство для выравнивания порядковчисел, представленных в системе остаточныхклассов, содержащее регистры первого и второгооперандов, выходами соединенные со входамисоответствующих дешифраторов первого и второго операндов, выходы которых соединенысо входами сумматора по модулю Р(Р - прос.тое число), входы регистров являются входамиустройства, о т л и ч а ю щ е е с я тем,что, с целью повышения быстродействия, оносодержит блок анализа разности порядков,блок управления сдвигом, шифратор, выходнойрегистр, элемент И, элемент ИЛИ, элементЗАПРЕТ, причем первый и второй выходы сум.матора по модулю Р соединены соответственнос первым и вторым входами блока анализаразности порядков, выход которого соединен спервым входом элемента ЗАПРЕТ, выходомчерез шифратор соединенного со входом выходного регистра, выход которого является выхо.дом разности порядков устройства, первый,второй, третий и четвертый выходы сумматорапо модулю Р соединены с соответствующимивходами блока управления сдвигом, выходыкоторого являются выходами сдвига устройства, пятый выход сумматора по модулю Р соединен с первым входом элемента И, выходкоторого соединен со вторым входом элементаЗАПРЕТ и является выходом переполненияустройства, первый, второй, третий и четвертыйуправляющие входы устройства соединены соот.ветственно с пятым, шестым, седьмым и вось.мым входами блока управления сдвигом и стретьим, четвертым, пятым, шестым входамиблока анализа разности порядков, седьмой входкоторого соединен с пятым выходом сумматора по модулю Р, третий и четвертый управляющие входы устройства соединены со входамиэлемента ИЛИ, выход которого соединен совторым входом элемента И,2. Устройство по и. 1, о т л и ч а ю щ е.е с я тем, что блок анализа разности порядковсодержит две группы по Р элементов ИЛИ иР групп по два элемента И, причем выходыэлементов ИЛИ перйой группы являются вы.ходами блока, выходы элементов И каждойгруппы соединены с входами соответствующихэлементов ИЛИ первой группы, первые входы78181первых элементов И каждой группы соединены с выходами соответствующих элементов ИЛИ второй группы, первые входы которых соеди.нсны между собой и являются первым входом блока, вторые входы элементов ИЛИ второй группы соединены между собой и являются вторым входом блока, вторые входы вторых элементов И всех групп соединены между собой и являются седьмым входом блока, первые входы вторых элементов И Р-ой, (Р - 1)-ой, (Р - 2)-ой и (Р - 3)-ей групп являются соответственно шестым, пятым, четвертым и третьим входами блока, вторые входы первых элементов И и первые входы вторых элементов И -ых групп (:1, 2,Р - 4) соединены между собой и являются третьим входом блока. 3.Устройство по п. 1, о т л и ч а ю щ ее с я тем, что блок управления сдвигом содержитпервый, второй и третий элементы ИЛИ и группу элементов И, выходы элементов ИЛИ являются выходами блока, первый, второй, третий, четвертый, пятый входы первого, третьего, девятого, восьмого, пятого элементов И группы, первый и второй входы второго элемента ИЛИ соединены с первыми входами соот./ ветственно третьего и четвертого элементов И группы, первый, второй, третий, четвертый, пя 2 10тый входы третьего элемента ИЛИ соединенысоответственно с выходами второго, четвертого,шестого, седьмого, десятого элементов И груп.пы, первые входы первого, пятого и девятогоэлементов И группы являются четвертым вхо.дом блока, первые входы второго, шестогои десятого элементов И группы являютсятретьим входом блока, первые вхбды третьегои седьмого элементов И являются первым входом блока, первые входы четвертого и восьмогоэлементов И являются вторым входом блока,вторые входы первого, второго, третьего ичетвертого элементов И группы соединены меж.ду собой и являются пятым входом блока, вторые входы пятого и шестого элементов Игрутпты соединены между собой и являютсяшестым входом блока, вторые входы седьмого,восьмого и девятого элементов И соединенымежду собой и являются седьмым входом блока, второй вход десятого элемента И группыявляется восьмым входом блока,Источники информации,принятые во внимание при экспертизе1.,Акушский И. Я Юдицкий Д, И. Машиннаяарифметика в остаточных классах, М., "Сов.радио", 1968,1, 4.2, Авторское свидетельство СССР Нф 377771,кл. 6 06 Г 7/50, 1973,

СмотретьЗаявка

1976539, 11.12.1973

СТАВРОПОЛЬСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. 60-ЛЕТИЯ ВЕЛИКОГО ОКТЯБРЯ

ЧЕРВЯКОВ НИКОЛАЙ ИВАНОВИЧ, КОЛЕСНИЦКИЙ СТАНИСЛАВ ВАЦЛАВОВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: выравнивания, классов, остаточных, порядков, представленных, системе, чисел

Опубликовано: 23.11.1980

Код ссылки

<a href="https://patents.su/8-781812-ustrojjstvo-dlya-vyravnivaniya-poryadkov-chisel-predstavlennykh-v-sisteme-ostatochnykh-klassov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для выравнивания порядков чисел, представленных в системе остаточных классов</a>

Предыдущий патент: Устройство для параллельного счета количества единиц (нулей) в двоичном числе

Следующий патент: Устройство для деления

Случайный патент: Грузоподъемное устройство