Потоковый параллельный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1691845

Автор: Александров

Текст

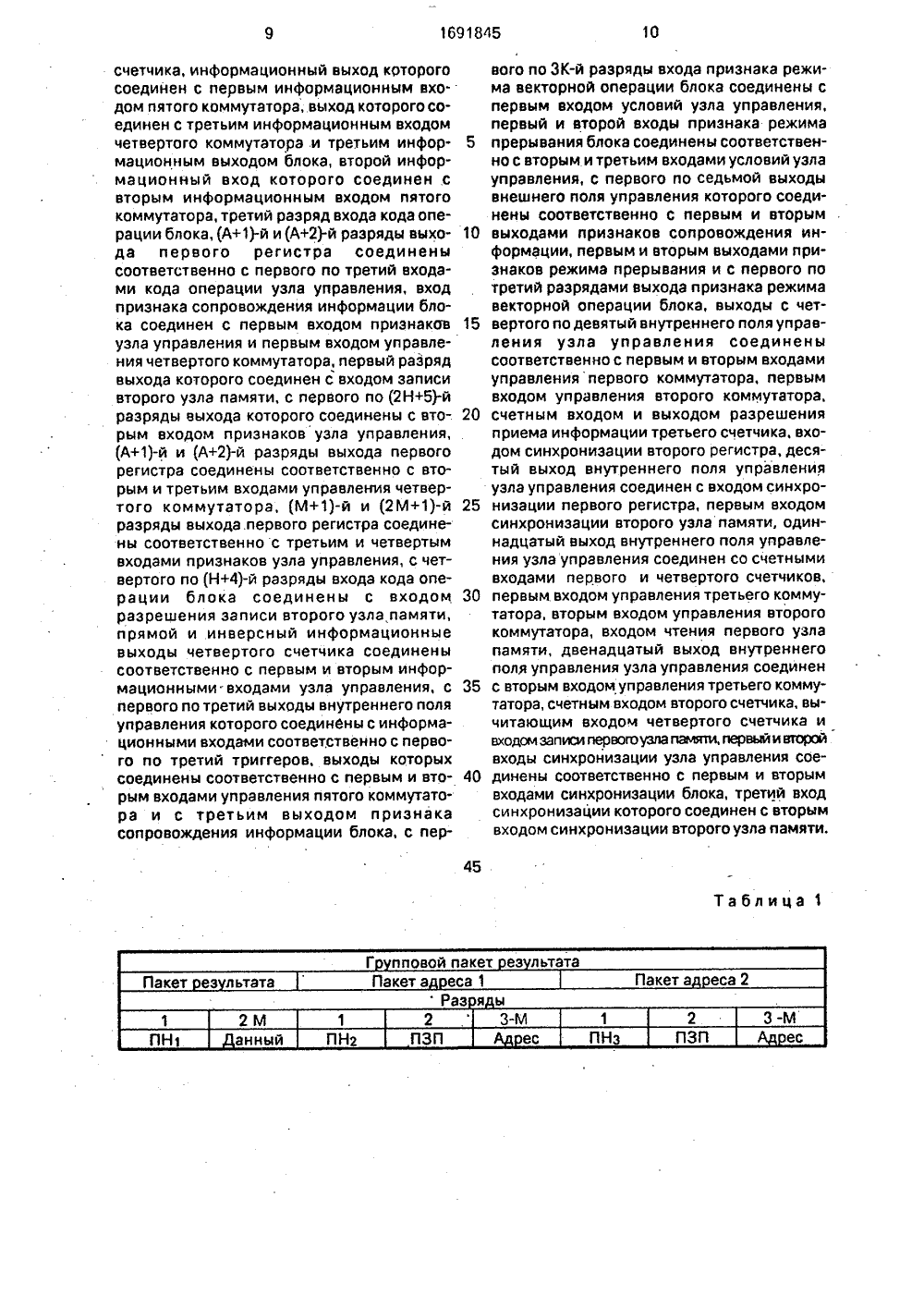

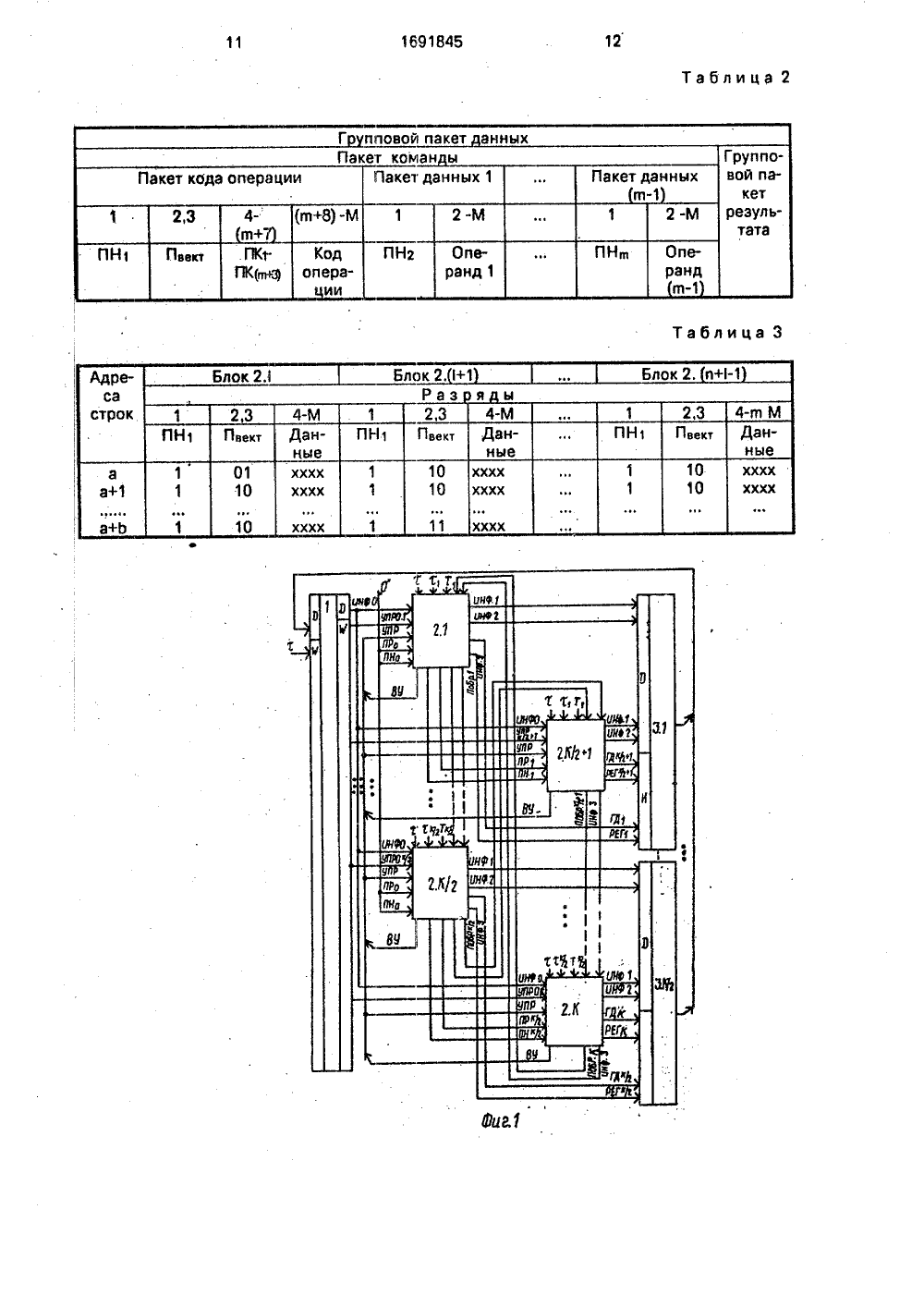

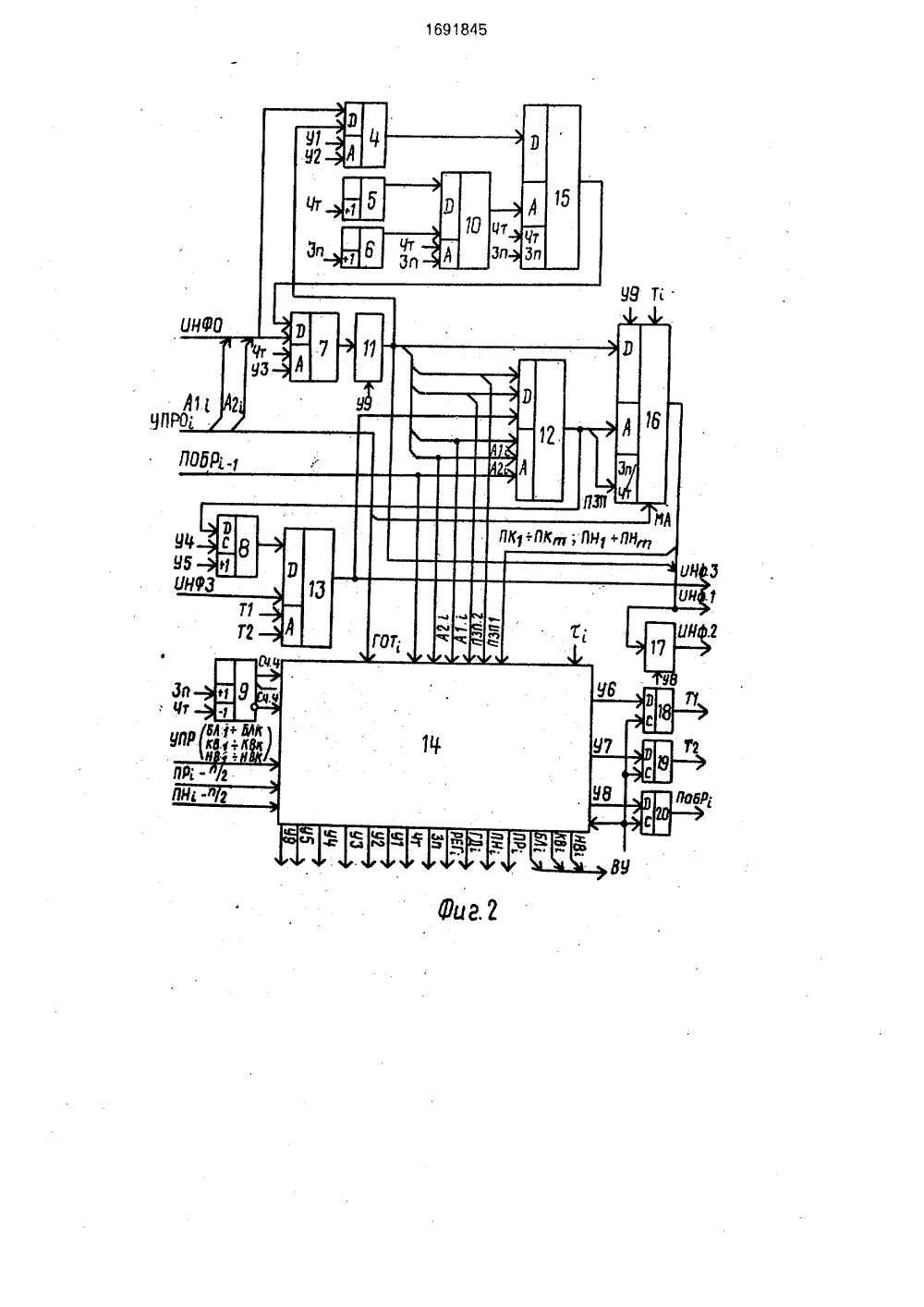

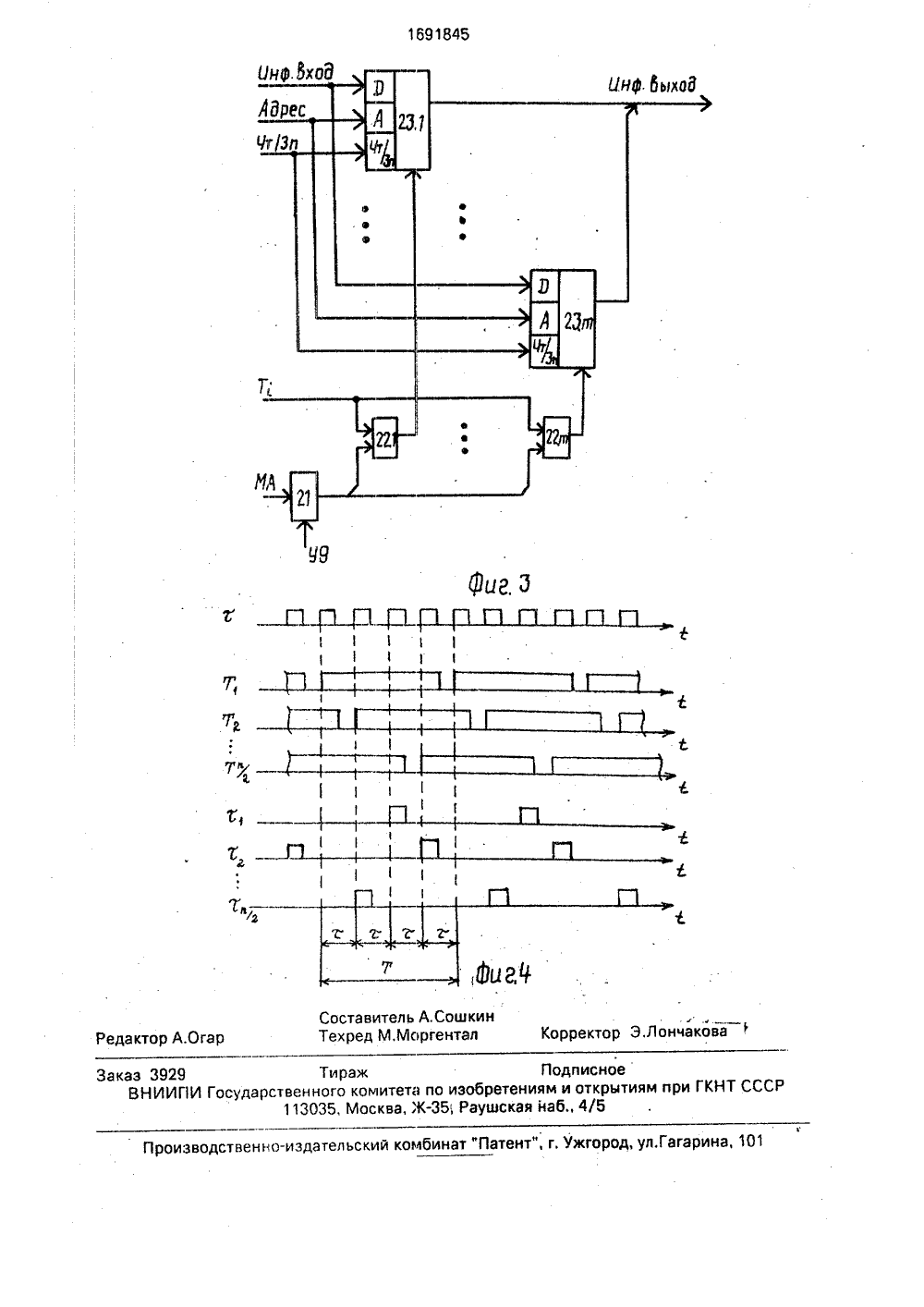

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК ю 0 06 Р 15/О ЕТЕ К АВ КО ЕТЕЛЬСТВУ ла памяти ы сигнало а фиг. 4 - инхронисвой вы- испольельных сти.быстро-нии векема уэ аграмм циональная схвременные дизации.Процессор (фиг,работки, блоки 2.1-2коммутаторы 3.1 - 3. КБлок обработкивый коммутатор 4, пе5 и 6, второй коммутай счетчики 8 и 9,рвый регистр 11, ч лок 1 обкоманд и) содержи К обработ фиг. 2) вклю вый и второ тор 7, третии ретий комм етвертый и и чает персчетчики и четвертатор 10,ятый комфунклельннальнфиг. иональго проя схема - функтыпе ОСУДАРСТВЕННЫЙ КОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯРИ ГКНТ СССР АНИЕ ИЗО(56) МайерсГ, Архитектура современныхЭВМ. Кн. 2 (Пер. с англ.). М.: Мир, 1985,с,251, рис,22.28,Вычислительная техника эа рубежом в1980 году/Под ред. В.С.Бурцева.М.: ИТМ иВТ АН СССР, 1981, с.50.Карцев М.А. Архитектура цифровых вычислительных машин. М Главная редакцияфизико-математической литературы изд-ва"Наука", 1978,Каган Б,М. Электронные вычислительные машины и системы: Учебн, пособие длявузов. М.; Энергоатомиздат, 1985.Авторское свидетельство СССРМ 1608682, кл. 6 06 Р 15/00, 20,08.89.(54) ПОТОКОВЫЙ ПАРАЛЛЕЛЬНЫЙ ПРОЦЕССОР(57) Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах высокой Изобретение относится к цифр числительной технике и может быть зовано в цифровых вычислит системах высокой производительноЦель изобретения - увеличение действия процессора при выполне торных операций.На фиг. 1 представлена ц ная схема потокового парал цессора; на фиг. 2 - функцио а блока обработки команд; на 3 производительности. Цель изобретения - увеличение быстродействия при выполнении векторных операций потокового параллельного процессора. Потоковый параллельный процессор содержит блок обработки, блоки обработки команд коммута-торы, Программа для процессора представляется в виде направленного графа, в узлах которого находятся команды, а дуги указывают направления передачи данных и признаки активизации команд. Команды, для которых есть все операнды, обрабатываются в блоке обработки, на выходе его формируются результат и адреса, по которым производится либо запись результата в память, либо считывание иэ нее следующих команд для их обработки. Это позволяет исключить наиболее сложную и дорогостоящую часть потоковых ЭВМ - ассоциативное ЗУ большой емкости. Наличие нескольких блоков обработки команд позволяеторганиэовать конвейерное считывание и обработку упорядоченных данных (векторов) любой длины без снижения эффективности работы процессора. 1 э.п, флы, 4 ил 3 табл.5 10 первого по третий признаки сопровождения информации; УПРО 1 - вход кода операции блока обработки команд; А 1 ь А 2, ГОТь 30 мутаторы 12 и 13, узел 14 управления, узлы 15 и 16 памяти, второй регистр 17 и с первого по третийтриггеры 18 - 20.Функциональная схема узла 16 памяти представлена на фиг. 3, Он содержит щ-разрядный регистр 21, элементы И 22.1-22,п и запоминающие блоки 23.1 - 23,т.Кроме того, на фиг, 1-3 обозначены: ИНФ 1, ИНФ 2, ИНФЗ - с первого по третий информационные выходы блока обработки команд; ИНФО, ИНФЗн - первый и вторсй информационные входы блока обработки команд; ПРь ПН - первый и второй признаки режима прерывания; ГД РЕГь ПОБР - с МА - первый, второй, третий и с четвертого по (Н+4)-й разряды входа кода операцииблока обработки команд; ВУ - выход реклма векторной операции блока обработки команд; УПР - вход режима векторной операции блока обработки команд; НВь КВь БЛ - с первого по третий разряды, выхода признака векторной операции; НВ 1 - НВк, КВ 1-КВк, БЛ 1 - БЛк - с первого по ЗК-й разряды входа признака векторной операции; Пвект, ПН 1 - ПНн, ПК 1 ПКН+3 с первого по (2 Н+5)-й разряды выхода второго узла памяти.Устройство работает следующим образом,Программа для процессора представляется в виде направленного графа. В узлах графа находятся команды, а дуги указывают направления, по которым передаются данные в виде группового пакета результата,ЗМ разрядов которого формируется в блоке 1 как результат выполнения операции и содержат М-разрядный пакет данных и два М-разрядных пакета адреса (табл. 1), Первый разряд каждого пакета является признаком наличия в нем информации (ПН- "1") либо указывает на ее отсутствие (ПН= "0"), в пакете адреса содержится признак активизацил(ПЗП) команды, Если ПЗП = "1", то по этому адресу производится запись М- разрядного пакета данных. Если ПЗ П = "0", то по этому адресу считывается щ М-разрядная команда, которая содержит М-разрядный пакет операции и. (гп) М-разрядных пакетов данных. Пакет команды и групповой пакет результата на выходе блока памяти объединяются в (а+3) М-разрядный групповой пакетданных (табл. 2). Пакет кода операции содержит признаки участия соответствующих пакетов в операции ПК 1- П Ка+3.В качестве блока 1 обработки может быть использован, например, процессор с шиной данных большой разрядности (в частности, изделие 5 Э 66, Фг 1,700.000). В каждом такте работы блок 1 принимает данные и код операции и на выходе формирует результат выполнения операции в виде группового пакета результата. Выходная шина данных блока 1 соединена с входами всех блоков 2. На управляющих выходах блока 1 формируются сигналы, которые управляют приемом информации в блоки 2, В каждом такте сигналы ГОТ 1 - ГОТк разрешают прием информации в соответствующие блоки памяти, а сигналы А 11-А 1 к и А 21 - А 2 к указывают, какой из двух адресов группового пакета результата используется для обращения в соответствующем блоке 2, сигналы маски (МА) обеспечивают запись М разрядов в строку памяти на соответствующие места и считывание полной гп М-разрядной строки. В каждом такте работы блок 1 обрабатывает до (2+а) М-разрядных операндов, формируя пои этом М-разрядный результат и до двух М-разрядных адресов; такую операцию считают скалярной, Если в операции участвуют больше операндовто такую операцию считают векторной. Она размещается в нескольких блоках 2 (табл, 3) и обрабатывается, соответственно, за большее количество тактов блока 1,В каждом такте производится прием ин-.формации ЗМ-разрядного группового пакета результата и управляющих сигналов А 1 и А 2 в 2 ьй блок обработки команд по сигналу ГОТь Так как такт работы блока 2 дольше такта работы блока 1, то информация накапливается в (ЗМ+2)-разрядном узле памяти, В каждом такте работы блока 2 на выходе ИНФ 1 формируется групповой пакет дан. ных для передачи в блок 1 по управляющемусигналу ГД; = "1",В момент т; могут выдавать данные вблок 1 1-й (1+К/2)-й блоки 2, При этом блок 2 с меньшим номером считывается приоритетным, поэтому формируются сигналы ГД = "1" и ГДн-кд = "0", по которым 1-й блок 2 передает групповой пакет данных в блок 1, а в блоке 2(+К/2) запрос на передачу данных в блок 1 запоминается в виде группового пакета результата в узле 15,В процессоре одновременно могут обрабатываться разные ветви программы. Для синхронизации их обработки и исключения потери информации при формировании команды проверяется соответствие призна ков ПК 1-ПКп в пакете операции и признаковПН 1-ПНП в пакетах операции и данных, Если окажется, что в команде нет всех данных для выполнения операции, то формируется сигнал ГД 1 = "О" и запрос в виде группового пакета результата заноситсяв узел 15, количество занятых ячеек узла 15 контролируется в счетчике 9. Если в узле 15 нет информации, то запрещается чтение из узла памяти. Если узел 15 заполнен, то формируется признак БЛ = "1", который запрещает передачу 5 данных в блок 1 для всех блоков 2, кроме 1-го. Это позволяет не допустить переполнения узла 15 с потерей информации и способствует последовательному перебору запросов из очереди в узле 15. Запросы, для 10 которых нет еще всех данных, возвращаются в конец очереди. Если команда передается в блок 1 для обработки, то запрос исключается из очереди и освобождает ячейку узла 15, при этом устанавливается 15 БЛ = "0".Если из узла 16 считана команда с признаком "Начало вектора", Пвект = "01", то ее передача в блок 1 задерживается на один такт работы блока 2 При этом групповой 20 пакет данных запоминаетсяв регистре 17, а адрес, по которому он был считан, заносится в счетчик 8 и передается в (+1)-й блок 2. Если, векторная команда содержит больше компонентов, чем блоков 2,. то запрос на 25 считывание данных, последовательно обойдя блоки памяти, возвращается в 1-й блок памяти, при этом адрес, содержащийся в счетчике 8, увеличивается на единицу.При выполнении векторной команды 30 для всех блоков 2 разрешается запись результата с выходов блока 1 в узле памяти, Если групповой пакет результата на выходах блока 1 содержит признак чтения иэ узла памяти, то он запоминается в узле па мяти, чтобы исключить передачу в блок 1 новой команды до тех пор, пока не будут обработаны все компоненты векторной команды. Триггеры 18 - 20 необходимы для сохранения управляющих сигналов на всем 40 протяжении такта работы узла памяти.Узел 15 представляет собой (ЗМ+2)-разрядное запоминающее устройство, содержащее Р ячеек. Число Р примерно равно максимальному числу одновременно выпол няемых ветвей программ.(а.М)-разрядное ЗУ обеспечивает запись М разрядов в соответствии с маской (МА), которая содержит одну единицу, и считывание полной (в,М)-разрядной строки, 50 при этом все разряды маски (МА) равны "1".Узел управления обеспечивает формирование в каждом такте управляющих сиг- . налов в соответствии с формулами:БЛ (Сч 4 к+1 Сч 41 " Сч 4 г. ф Сч 4 к"55 "Сч 4 к+1 х, где К=1 одгр;"0" при х РЕГГА = х( % пвект .= "00") ПН 1П Ннннг П Рьп ЖЛ )П = х ГОГОТх ) ГД " йОВТ "ПБЛ);где ПОВН 1" при х(% ПОВТ НВ; ПБЛ);1,"0" при х ПОВТЧТ = х( х ЗП СЧ 4,Сч 4 гКСч 4 к+1;У 1- х(ГОТ- Я);У 2 = (ГДу ПОВТ х;УЗ=1" при КПвект="01 "1 НВуПОБРь 1);0" при х ПОБРУ 4 = Пвект.= "01") НВ)У 5= х(НВ" ПОБР);У 6 = НВ;У 7 = т(НВ ПОБРь 1);У 8 = ПОВТУ 9= х ГОТ;ПОБР = УЧ,На фиг, 4 представлены временные диаграммы синхронизирующих сигналов. Длительность такта работы блока 1 обозначена,блока 2 - Т.Формула изобретения1. Потоковый параллельный процессор,содержащий блок обработки, первый блокобработки команд, первый коммутатор,причем первый вход синхронизации процессора соединен с входом синхронизацииблока обработки, информационный выходкоторого соединен с первым информационным входом первого блока обработки команд, первый и второй информационныевыходы которого соединены соответственно с первым и вторым информационнымивходами первого коммутатора, выход которого соединен с первым информационнымвходом блока обработки, первый и второйвыходы признаков сопровождения информации первого блока обработки команд соединены соответственно с первым и вторымуправляющими входами первого коммутатора, первый выход кода операции блокаобработки соединен с входом кода операции первого блока обработки команд, первый вход синхронизации процессорасоединен с первым входом синхронизациипервого блока обработки команд, второй итретий входы синхронизации которого соединены соответственно с вторым и третьим входами синхронизации процессора, от л ич а ю щ и й с я тем, что, с целью увеличения быстродействия и ри выполнении векторных операций, он дополнительно содержит с второго по К/2-й коммутаторы, где К = (2.Т)/ т; Т - длительность такта работы блока команд; т - длительность такта работы блока обработки, с второго по К-й блоки обработки команд, причем информационный выход блока обработки соединен с первыми информационными входами с второго по К-й блоков обработки команд, первый и второй информационные выходы с второго по К/2-й блоков обработки команд соединены соответственно с первым и вторым информационными входами с второго по К/2-й коммутаторов, выходы которых соединены соответственно с второго по К/2-й информационными входами блока обработки, первый и второй информационные выходы с (К/2+1)-го по К-й блоков обработки команд соединены соответственно с третьим и четвертым информационными входами с первого по КЦ-й коммутаторов, первый и второй выходы признаков сопровождения информации с второго по К/2-йблоков обработки команд соединены соответственно с первым и вторым управляющими входами с второго по К/2-й коммугаторов, первый и второй входы признаков сопровождения информации с (К/2+1)-го по К-й блоков обработки команд соединены соответственно с третьим и четвертым управляющими входами с первого по К/2-й коммутаторов, третий информационный выход и третий выход признака сопровождения информации с первого по К-й блоков обработки команд соединены соответственно с вторым информационным входом и входом признака сопровождения информации с второго по К-й и с первым блоком обработки команд, выходы первого и второго признаков режима прерывания с первого по К/2-й блоков обработки команд соединены соответственно с первым и вторым входами признаков режима прерывания с (К/2+1)-го по К-й блоков обработки команд, с первого по третий выходы признаков режима векторной операции с первого по К-й блоков обработки команд соединены соответственно с первого по ЗК-й входами признаков режима векторной операции с-первого.по К-й блоков обработки команд, с второго по К-й выходы кода операции блока обработки соединены соответственно с входами кода операции с второго по К-й блоков обработки команд, первый вход синхронизации процессора со 5 10 15 20 25 30 35 40 45 50 55 единен с первыми входами синхронизации с второго по К-й блоков обработки команд, вторые и третьи входы синхронизации с второго по К/2-й блоков обработки команд соединены соответственно с четвертого по (К+1)-й входами синхронизации процессора, с второго по (К+1)-й входы синхронизации которого соединены соответственно с вторым и третьим входами синхронизации с (К/2+1)-го по К-й блоков обработки команд.2, Процессор по и, 1, о т л и ч а ю щ и й с я тем, что блок обработки команд содержит первый и второй узлы памяти, с первого по пятый коммутаторы, с первого по четвертый счетчики, первый и второй регистры, с первого по третий триггеры, узел управления, причем первый информационный вход и первый и второй разряды входа кода операции блока соединены с первыми информационными входами первого и второго коммутаторов, выход первого коммутатора соединен с информационным входом первого узла памяти, информационные выходы первого и второго счетчиков соединены соответственно с первым и вторым информационными входами третьего коммутатора, выход которого соединен с входом адреса первого узла памяти, выход которого соединен с вторым информационным входом второго коммутатора, выход которого соединен с информационным входом первого регистра, выход которого соединен с вторым информационным входом первого коммутатора, с первого по А-й разряды выхода первого регистра соединены соответственно с первого по А-й разрядами информационного входа второго регистра и первого информационного выхода блока (где А - количество разрядов группового пакета результата, А = ЗМ; М - количество разрядов пакета данных или адреса), с первого по М-й разряды выхода первого оегистра соединены соответственно с г 1 ервого по М-й разряд информационного входа второго узла памяти, с первого по В-й разряды выхода (где В - количество разрядов пакета команды, В = НМ; Н - количество пакетов данных в пакете команды) второго узла памяти соединены соответственно с (А+1)-го по (А+В)-й разрядами информационного входа второго регистра и первого информационного выхода блока, второй информационный выход которого соединен с выходом . второго регистра, с (М+1)-го по 2 М-й и с (2 М+1)-го по ЗМ-й разряды выхода первого регистра соединены соответственно с первым и вторым информационными входами четвертого коммутатора, выход которого соединен с адресным входам второго узла памяти и информационным входом третьего1691845 10 10 15 20 25 30 35 45 Таблица 1 счетчика, информационный выход которого соединен с первым информационным входом пятого коммутатора, выход которого соединен с третьим информационным входом четвертого коммутатора .и третьим информационным выходом блока, второй информационный вход которого соединен с вторым информационным входом пятого коммутатора, третий разряд входа кода операции блока, (А+1)-й и (А+2)-й разряды выхода первого регистра соединены соответственно с первого по третий входами кода операции узла управления, вход признака сопровождения информации блока соединен с первым входом признаков узла управления и первым входом управления четвертого коммутатора, первый разряд выхода которого соединен с входом записи второго узла памяти, с первого по (2 Н+5)-й разряды выхода которого соединены с вторым входом признаков узла управления, (А+1)-й и (А+2)-й разряды выхода первого регистра соединены соответственно с вторым и третьим входами управления четвертого коммутатора, (М+1)-й и (2 М+1)-й разряды выхода. первого регистра соединены соответственно с третьим и четвертым входами признаков узла управления, с четвертого по (Н+4)-й разряды входа кода операции блока соединены с входом разрешения записи второго узла памяти, прямой и инверсный информационные выходы четвертого счетчика соединены соответственно с первым и вторым информационными. входами узла управления, с первого по третий выходы внутреннего поля управления которого соединены с информационными входами соответственно с первого по третий триггеров, выходы которых соединены соответственно с первым и вто рым входами управления пятого коммутатора и с третьим выходом признака сопровождения информации блока, с первого по ЗК-й разряды входа признака режима векторной операции блока соединены с первым входом условий узла управления, первый и второй входы признака режима прерывания блока соединены соответственно с вторым и третьим входами условий узла управления, с первого по седьмой выходы внешнего поля управления которого соединены соответственно с первым и вторым выходами признаков сопровождения информации, первым и вторым выходами признаков режима прерывания и с первого по третий разрядами выхода признака режима векторной операции блока, выходы с четвертого по девятый внутреннего поля управления узла управления соединены соответственно с первым и вторым входами управления первого коммутатора, первым входом управления второго коммутатора, счетным входом и выходом разрешения приема информации третьего счетчика, входом синхронизации второго регистра, десятый выход внутреннего поля управления узла управления соединен с входом синхронизации первого регистра, первым входом синхронизации второго узла памяти, одиннадцатый выход внутреннего поля управления узла управления соединен со счетными входами первого и четвертого счетчиков, первым входом управления третьего коммутатора, вторым входом управления второго коммутатора, входом чтения первого узла памяти, двенадцатый выход внутреннего поля управления узла управления соединен с вторым входом управления третьего коммутатора, счетным входом второго счетчика, вычитающим входом четвертого счетчика и входом записи первогоузла памяти, первый и второй входы синхронизации узла управления соединены соответственно с первым и вторым входами синхронизации блока, третий вход синхронизации которого соединен с вторым входом синхронизации второго узла памяти,1691845 Редактор А,Ога Заказ 3929 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 Х 1 7 Составитель А.СашкинТехред М,Моргентал Корректор Э.Лончакова

СмотретьЗаявка

4709165, 26.06.1989

П И. Александров

АЛЕКСАНДРОВ ПАВЕЛ ИВАНОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: параллельный, потоковый, процессор

Опубликовано: 15.11.1991

Код ссылки

<a href="https://patents.su/8-1691845-potokovyjj-parallelnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Потоковый параллельный процессор</a>