Микропрограммный процессор с контролем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

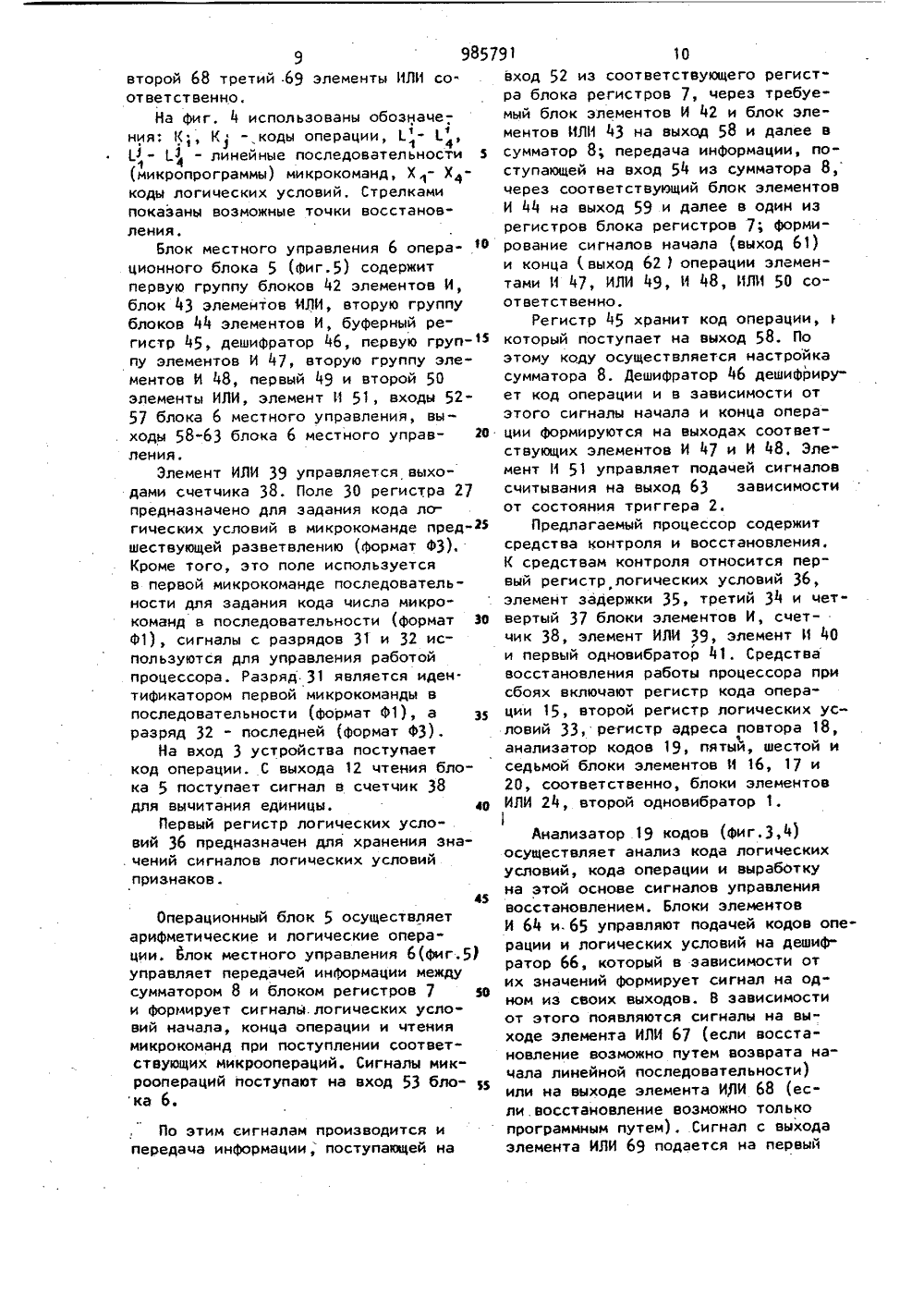

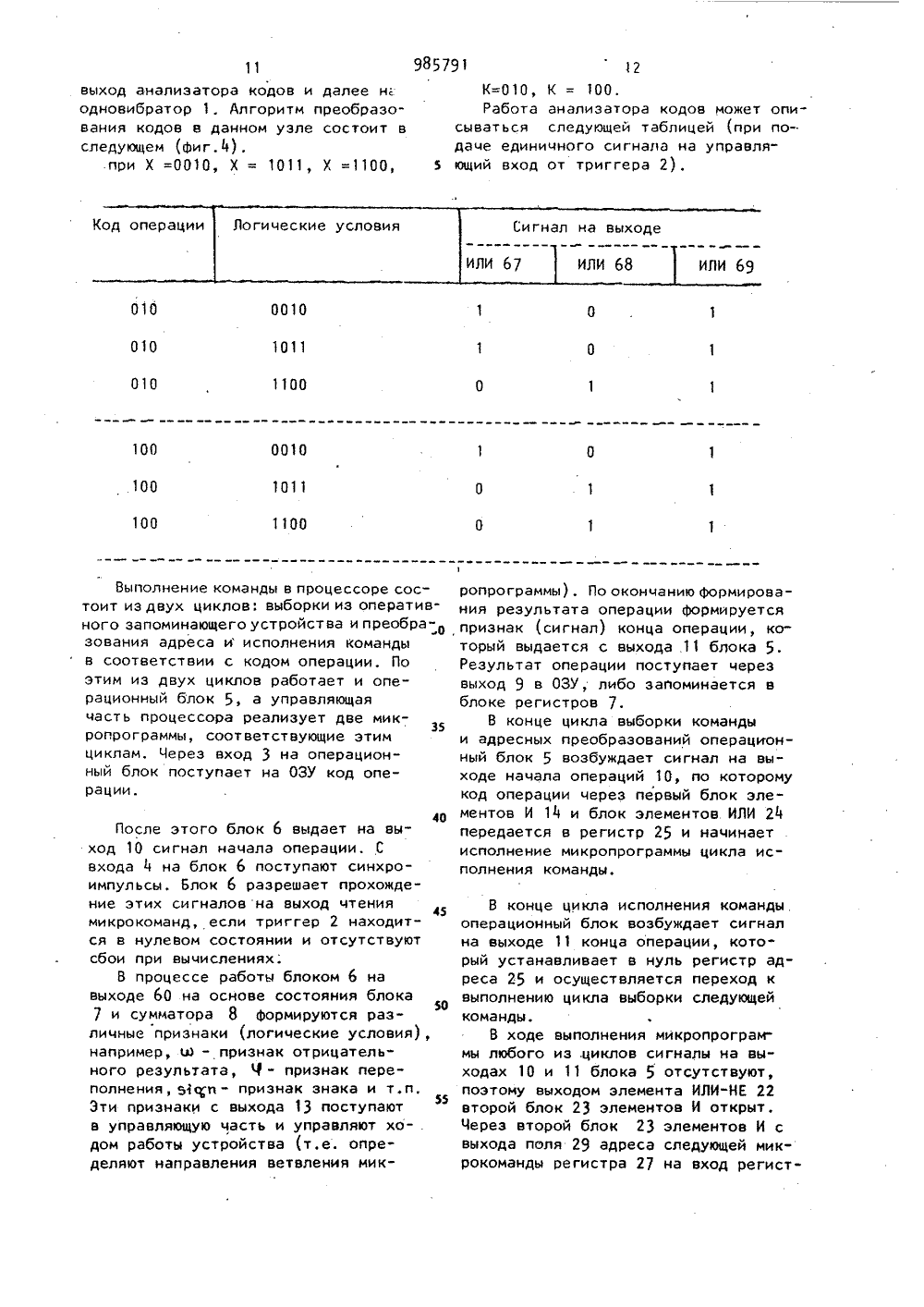

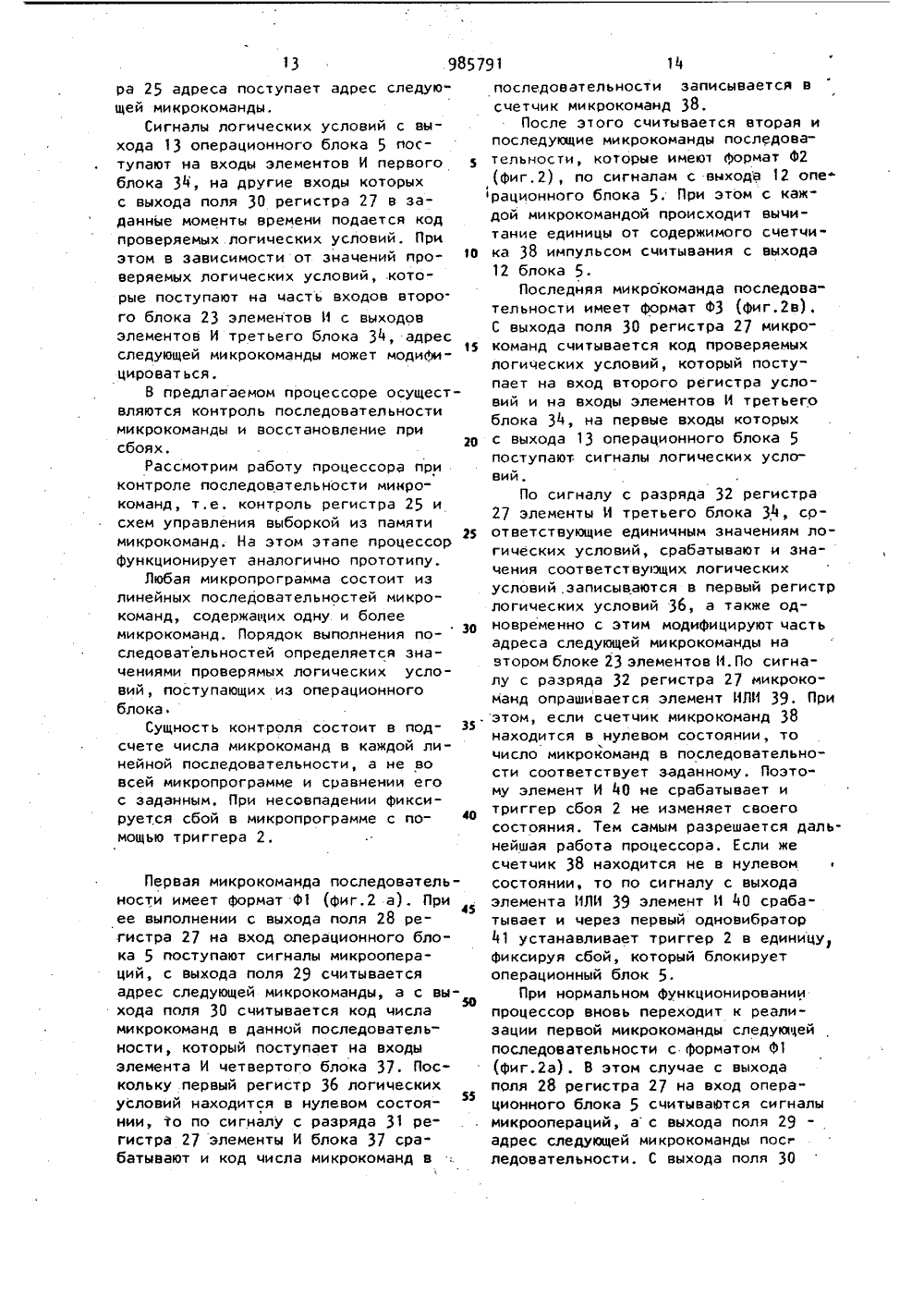

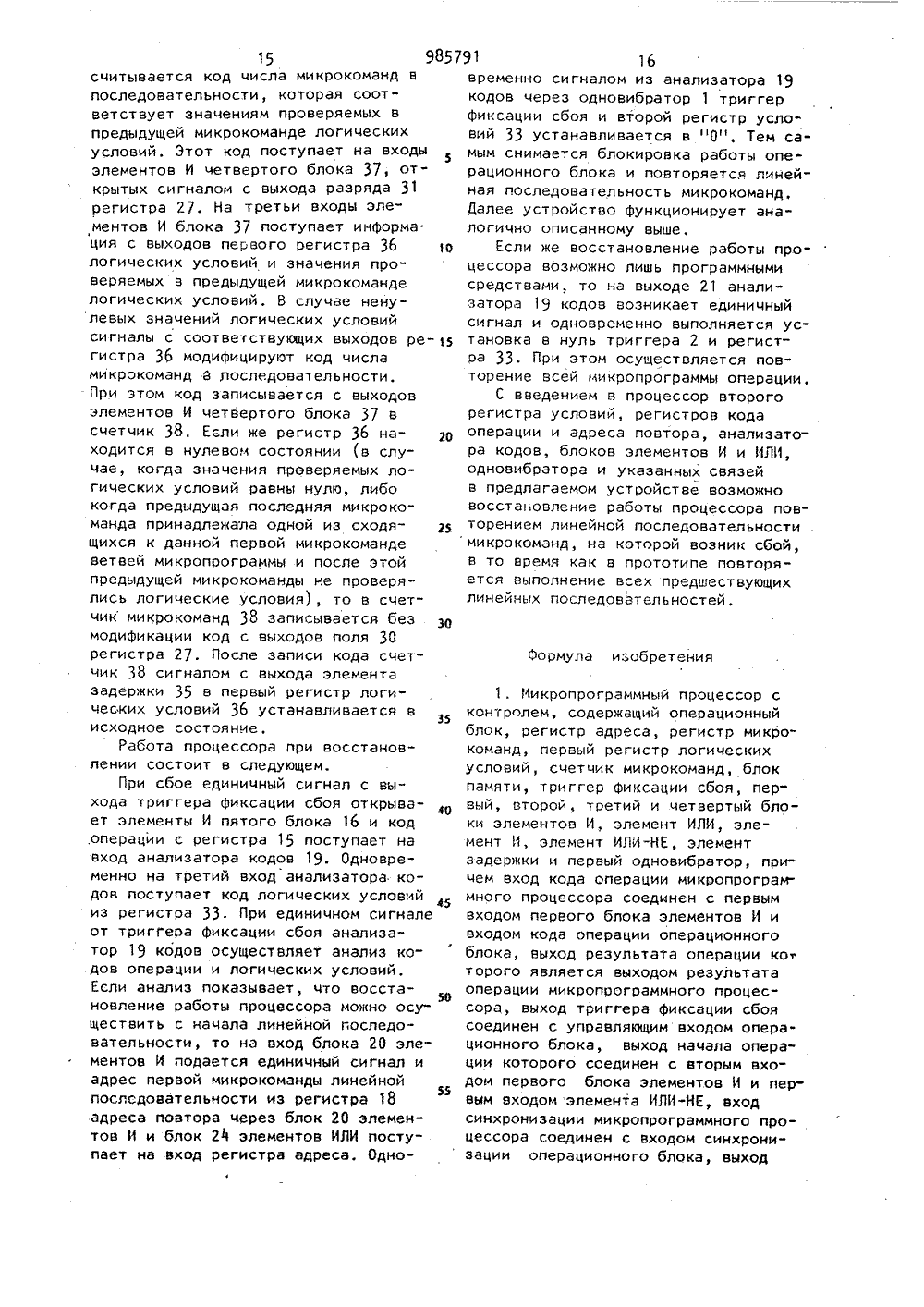

) МИКРОПРОГРАММНЦЙ ПРОЦЕССОР С РОЛЕМ блок,мик.са20 Изобретение относится к вычислительной технике, в частности к процессорам с контролем функционирования и восстановлением при сбоях.Известен программный процессор,включающий в себя операционный блок,блок памяти микрокоманд, регистр мик-.рокоманд, регистр адрвса микрокоманд,счетчик микрокоманд, триггер фиксации сбоя, элементы И, ИЛИ:, НЕ 1 3,Недостатком указанного устройстваявляется низкая оперативность контроля и восстановления работы устройства, большой объем контрольного оборудования.Известен также микропрограммный,процессор с восотановлением присбоях, содержащий операционныйблок памяти, регистры адреса ирокоманд, счетчик, регистр адреповтора, элементы И, ИЛИ 2 1Недостатками этого устройства являются ограниченные функциональныевозможности, обусловленные тем, что,2восстановление информации осуществляется путем рвторения микрокоманд, при выполнении которых обнаружен сбой. Это предъявляет дополнительные требования к характеру микро- команд и средствам их восстановления.Наиболее близким к предлагаемому по технической сущности является процессор, содержащий регистр логических условий, счетчик микрокоманд, четыре блока элементов И, первый элемент ИЛИ, элемент И, элемент ИЛИ-НЕ, элемент задержки, первый одновибратор, триггер фиксации сбоя, регистр микрокомандрегистр адреса, блок памяти и операционный блок, первый вход которого связан с входом процессора и первым входом первого . блока элементов И, второй, третий, и четвертый входы, первый и второй выходы соединены с единичным выходом триггера фиксации сбоя,.входом синхронизирующих импульсов, первым вы 19 Источники информации,принятые во вниеание при экспертизе1. Авторское свидетельство СССРМ 485274, кл. 606 Г 9/16,1974. 985791202. Авторское свидетельство СССР .по заявке Ю 2776555/18-24,кл. О 06 Г 9/16, 1979,3, Авторское свидетельство СССРпо заявке Н 2649225/18-24,кл. О 06 Г 15/20, 1979 (прототип).985791 ь И,Сигаловастелевич Корректор О,Билак. Состави Подписное л ППП "Патент", г, Ужгород, ул. Проектная, 4 ИИПИ Государственного комит по делам изобретений и отк 3035, Москва, Ж, Раушскаходом регистра микрокоманд, выходомрезультата операции и первым выходомтретьего блока элементов И соответственно, третий выход соединен с вторым входом первого блока элементовИ и первым входом элемента ИЛИ-НЕ,четвертый выход соединен с вторымвходом, элемента ИЛИ-НЕ и установочным входом регистра адреса, пятыйвыход соединен с входом управления 10считывания блока памяти и счетнымвходом счетчика микрокоманд, выходыкоторого через первый элемент ИЛИ,первый элемент И и одновибратор соединены с единичным входом триггера 15Фиксации сбоя, а установочный входсоединен с вь 1 ходом четвертого блокаэлементов И, первый вход которогосоединен с выходом регистра логических условий, информационный вход которого связан с выходом третьего блока элементов И и первым выходом второго блока элементов И, выход которого, второй и третий входы соеди:нены соответственно с первым входом 25регистра адреса, выходом элементаИЛИ-НЕ и вторым выходом регистрамикрокоманд, третий выход которогосоединен с вторым входом третьего ичетвертого блоков элементов И, четеертый выход соединен с третьим входом четвертого блока элементов И ичерез элемент задержки с установочным входом первого регистра логических условий, пятый выход соединен стретьим входом одноименного блокаэлементов И и вторым входом первогоэлемента И, вход соединен с выходомблока памяти, вход которого соединенс выходом регистра адреса340Недостатком этого процессора яв-.ляется низкая оперативность восстановления работы при сбоях.При обнаржении ошибки работа процессора блокируется и происходит об- ф 5ращение к ОЗУ для вызова программыанализа ошибки и восстановления работы устройства. Очевидно, что этосравнительно длительный процесс,так как такую программу необходимо 50вызвать, запросить соответствующиеисходные данныеслово состоянияпрограммы ), проанализировать промежуточные результаты решения, еслитаковые имеются и т,д. Кроме того, 55программно необходимо Формироватьадрес микрокоманды повтора, что реализовать затруднительно, так как,например, в ЕС ЭВМ нельзя в программе задавать адреса микрокоманд.Это приводит к необходимости повторного выполнения операции, при выполнении которой произошел сбой, хотя в этом, может быть и нет необходимости ввиду того, что восстановление зачастую можно начать с некоторой внутренней микрокоманды операции.Цель изобретения - повышение быстродействия восстановления вычислительного процесса при сбоях.Поставленная цель достигается тем, что в микропрограммный процессор с контролем, содержащий опера- ционный блок, регистр адреса, регистр микрокоманд, первый регистр логических условий, счетчик микрокоманд, блок памяти, триггер Фиксации сбоя, первый, второй, третий и четвертый блоки элементов И, элемент ИЛИ, элемент И, элемент ИЛИ-НЕ, элемент задержки и первый одновибратор, причем вход кода операции микропрограммного процессора соединен с первым входом первого блока элементов И и входом кода операции операционного блока, выход результата операции которого является выходом результата операции микропрограммного процессора, выход триггера Фиксации сбоя соединен с управляющим входом операцик онного блока, выход начала операции которого .соединен с вторым входом первого блока элементов И и первым входом элемента ИЛИ-НЕ, вход синхронизации микропрограммного процессора соединен с входом синхронизации опе рационного блока, выход конца операции которого соединен с вторым входом элемента ИЛИ-НЕ и установочным входом регистра адреса, выходы адреса и микроопераций регистра микро- команд соединены соответственно с первым входом второго блока элементов И и с входом микроопераций операционного блока, выход чтения микрокоманд которого соединен с управляющим входом блока памяти и счетным входом счетчика микрокоманд, выход логических условий операционного блока соединен с первым входом первого блока элементов И, выход которого соединен с третьим входом второго блока элементов И, выход которого соединен с первым информационным входом регистра адреса, выход регистра адреса соединен с адресным входом985 40 5блока памяти, выход которого соединен с входом регистра микрокоманд, выход логических условий регистра микрокоманд соединен с вторым. входом третьего блока элементов И и первым входом четвертого блока элементов И, выход которого соединен с установочным входом счетчика микрокоманд, первый управляющий выход регистра микрокоманд соединен с вторым входом 1 о четвертого блока элементов И и через элемент задержки с установочным входом первого регистра логических условий, выход которого соединен с третьим входом четвертого блока эле ментов И, выходы счетчика микрокоманд соединены с входами элемента ИЛИ, выход которого соединен с первым входом элемента И, второй управляющий выход регистра микрокоманд соеди О нен с третьим входом третьего блока элементов И и вторым входом элемента И, выход которого через первый одновибратор соединен с единичным входом триггера фиксации сбоя, введены 25 регистр кода операции, регистр адреса повтора, второй регистр логических условий, анализатор кодов, пятый, шестой и седьмой блоки элементов И, блок элементов ИЛИ и второй одновибратор, причем выход первого блока элементов И соединен с входом регистра кода операции и первым входом блока элементов ИЛИ, выход которого соединен с вторым информационным вхо 35 дом регистра адреса, выход регистра кода операции соединен С первым входом пятого. блока элементов И, выход которого соединен с пераым информационным входом анализатора кодов, единичный выход триггера фиксации сбоя соединен с вторым входом пятого блока элементов И и управляющим входом анализатора кодов, первый управляющий выход которого через второй45 одновибратор соединен с нулевым входом триггера фиксации сбоя и установочным входом второго регистра логических условий, выход которого соединен с вторым информационным входом анализатора кодов, выход регист 50 ра адреса и первый управляющий выход регистра команд соединены соответственно с первым и вторым входами шестого блока элементов И, выход которого соединен с входом регистра адреса повтора, выход регистра адреса повтора соединен с первым входом седьмого блока элементов И, выход 791 6которого соединен с вторым входомблока элементов ИЛИ, второй и третий управляющие выходы анализаторакодов соединены соответственно с вторым входом седьмого блока элементовИ и выходом программного восстановления устройства,Кроме того, анализатор кодов содержит первый и второй блоки элементов И, дешифратор, первый, второйи третий элементы ИЛИ, причем первыйи второй информационные входы анализатора кодов соединены с первыми входами первого и второго блоков эле-ментов И соответственно, выходы которых соединены соответственно с первым и вторым входами дешифратора, управляющий вход анализатора кодов соединен с вторыми входами первого и второго блоков элементов И, первая и вторая группы выходов дешифраторов соединены с входами первого и второгоэлементов ИЛИ соответственно, выходтретьего элемента ИЛИ является первым управляющим выходом анализаторакодов, выход первого элемента ИЛИсоединен с первым входом третьегоэлемента ИЛИ и является вторым управляющим выходом анализатора кодов, выход второго элемента ИЛИ соединен свторым входом третьего элемента ИЛИи является третьим управляющим выхо,",дом анализатора кодов.Сущность изобретения состоит в восстановлении работы процессора путемповторения последней линейной последовательности микрокоманд либо всеймикропрограммы в зависимости от кодаоперации и значений логических условий, при которых произошел сбой.Это обеспечивается хранением кодаоперации адреса первой микрокоманды линейной последовательности и кода логических условий, при которыхвыполняется линейная последовательность. При фиксации сбоя посредствоманализатора кодов анализируется кодоперации и логические условия, устанавливается в нуль триггер фиксации сбоя. При возможности восстановления работы процессора повторениемлинейной последовательности микрокоманд адрес ее первой микрокомандызаносится в регистр адреса, послечего начинается повторное выполнениеданной линейной последовательности,В противном случае происходит обращение в ОЗУ для программнога восстановления работы процессора, 985791Реализация процедуры восстановления работы процессора достигаетсяиспользованием следующих новых связей и элементов.Введение регистра кода операции,пятого блока элементов И, второгорегистра логических условий и обусловленных ими связей позволяет хранить и анализировать код операции,логические условия и при возникновении сбоя выдавать сигнал сбросатриггера фиксации сбоя и сигналы восстановления повторением линейной последовательности либо программноговосстановления,Введение шестого блока элементовИ, регистра адреса повтора, седьмогоблока элементов И и обусловленныхими связей позволяет в начале каждой линейной последовательности посигналу с первого управляющего выхода регистра микоокоманд запись 1 ватьадрес ее первой микрокоманды.При восстановлении работы процессора после сбоя повторением линейной последовательности по единичномусигналу с выхода анализатора кодовадрес из регистра повтора через блокэлементов ИЛИ записывается в регистрадреса.Соединение первого управляющеговыхода анализатора кодов через второй одновибратор с нулевым входомтриггера фиксации сбоя и установочным входом второго регистра логических условий позволяет устанавливать их в нуль, прекращая тем самымподачу кода операции через пятыйблок элементов на вход анализаторакодов,Введение укаэанных связей и элементов позволяет повысить скоростьвосстановления вычислительного процесса при сбоях за счет автоматического повтора линейной последовательности микрокоманд, либо обращения кпрограммным средствам восстановления(повторному выполнению соответствую"щих операций). На фиг. 1 изображена Функциональная схема микропрограммного процессора с контролем; на Фиг. 2 - Форматы реализуемых микрокоманд; на Фиг. 3 - функциональная схема анализатора кодов; на Фиг. 4 - примеры восстановления микропрограмм, поясняющие работу анализатора кодов; на Фиг. 5 " функциональная схема уз Анализатор кодов 19 (фиг 3) содержит первый 64 и второй 65 блоки элементов И; дешифратор 66, первый 671 ла местного управления операционногоблока.На фиг. 1 обозначены второй одновибратор 1, триггер 2 фиксациисбоя, вход 3 кода операции микропроцессора, вход 4 синхроимпульсов, операционный блок 5, состоящий из блока 6 местного управления, блока 7регистров, сумматора 8, выход 9 ре зультата операции, выходы 10 и 11начала и конца операций операционного блока соответственно, выход 12чтения микрокоманд, выход 13 логических условий операционного блока, пер вый блок 14 элементов И, регистр 15кода операции, пятый 16 и шестой 17блоки элементов И, регистр 18 адреса повтора, анализатор 19 кодов,седьмой блок 20 элементов И, выход 20 21 программного восстановления процессора, элемент ИЛИ-НЕ 22, второйблок 23 элементов И, блок 24 элементов ИЛИ, регистр 25 адреса, блок 26памяти, регистр 27 микрокоманд, раз деленный на пять полей: поле 28 микроопераций, поле 29 адреса следующеймикрокоманды, поле 30 задания проверяемых логицеских условий ( признаков)или кода числа микрокоманд в послезо довательности, первый 31 и второй 32управляющие разряды соответственно,второй регистр 33 логических условий,третий блок 34 элементов И, элементзадержки 35, первый регистр 36 логи"ческих условий, четвертый блок 37 элементов И, счетчик 38 микрокоманд,первый элемент ИЛИ 39, элемент И 40и первый одновибратор 41.На Фиг. 2 а изображен формат Ф 1первой микрокоманды.; на фиг.2 бФормат Ф 2 второй - последующих микрокоманд (кроме последней ); наФиг. 2 в - формат Ф 3 последней микрокоманды линейной последовательности,В полях 28-29 Форматов Ф 1-Ф 3 записаны сигналы микроопераций ( ИО ) и адрес следующей микрокоманды (Р) соответственно. В поле 30 формата Ф 1задается код числа микрокоманд в последовательности (Й 1), а в ФорматеФ 3 - код проверяемых логических условий (Х). В Формате Ф 2 поле 30 пусто. В разрядах 31 и 32 форматов Ф 1- Ф 3 записаны соответственно 10,00,01,(микропрограммы) микрокоманд, Х - Х 4 коды логических условий. Стрелкамипоказаны возможные точки восстановления.Блок местного управления 6 опера- .10ционного блока 5 (фиг.5) содержитпервую группу блоков 42 элементов И,блок 43 элементов ИЛИ, вторую группублоков 44 элементов И, буферный регистр 45, дешифратор 46, первую группу элементов И 47, вторую группу элементов И 48, первый 49 и второй 50элементы ИЛИ, элемент И 51, входы 5257 блока б местного управления, выходы 58-63 блока 6 местного управпения,Элемент ИЛИ 39 управляется выходами счетчика 38. Поле 30 регистра 27предназначено дпя задания кода псггических условий в микрокоманде пред шествующей разветвлению (формат Ф 3),Кроме того, это поле используетсяв первой микрокоманде последовательности для задания кода числа микрокоманд в последовательности (формат 30Ф 1), сигналы с разрядов 31 и 32 используются для управления работойпроцессора. Разряд 31 является иден.тификатором первой микрокоманды впоследовательости (Формат Ф 1), а 35разряд 32 - последней (формат Ф 3).На вход 3 устройства поступаеткод операции. С выхода 12 чтения блока 5 поступает сигнал в счетчик 38для вычитания единицы. 40Первый регистр логических условий 36 предназначен дпя хранения зна.чений сигналов логических условийпризнаков. вход 52 из соответствующего регистра блока регистров 7, через требуемый блок элементов И 42 и блок элементов ИЛИ 43 на выход 58 и далее в сумматор 8; передача информации, поступающей на вход 54 из сумматора 8, через соответствующий блок элементов И 44 на выход 59 и далее в один из регистров блока регистров 7; Формирование сигналов начала (выход 61) и конца ( выход 62 1 операции элементами И 47, ИЛИ 49, И 48, ИЛИ 50 соответственно.Регистр 45 хранит код операции, который поступает на выход 58. По этому коду осуществляется настройка сумматора 8. Дешифратор 46 дешифриру" ет код операции и в зависимости от этого сигналы начала и конца опера" ции Формируются на выходах соответствующих элементов И 47 и И 48, Элемент И 51 управляет подачей сигналов считывания на выход 63 зависимости от состояния триггера 2.Предлагаемый процессор содержит средства контроля и восстановления. К средствам контроля относится первый регистр логических условий 36, элемент задержки 35, третий 34 и четвертый 37 блоки элементов И, счетчик 38, элемент ИЛИ 39, элемент И 40 и первый одновибратор 41. Средства восстановления работы процессора при сбоях включают регистр кода операции 15, второй регистр логических условий 33, регистр адреса повтора 18, анализатор кодов 19, пятый, шестой и седьмой блоки элементов И 16, 17 и 20, соответственно, блоки элементов ИЛИ 24, второй одновибратор 1.Анализатор 19 кодов (фиг.3,4) осуществляет анализ кода логических условий, кода операции и выработку на этой основе сигналов управления восстановлением. Блоки элементов И 64 и. 65 управляют подачей кодов операции и логических условий на дешиф" ратор 66, который в зависимости от их значений формирует сигнал на одном из своих выходов. В зависимости от этого появляются сигналы на выходе элемента ИЛИ 67 (если восстановление возможно путем возврата начала линейной последовательности) или на вцходе элемента ИЛИ 68 (если.восстановление возможно только программным путем). Сигнал с выхода элемента ИЛИ 69 подается на первый 45Операционный блок 5 осуществляет арифметические и логические операции. Блок местного управления 6(фиг.5) управляет передачей информации между сумматором 8 и блоком регистров 7 50 и Формирует сигналы. логических условий начала, конца операции и чтения микрокоманд при поступлении соответствующих микроопераций. Сигналы микроопераций поступают на вход 53 бло ка 6. По этим сигналам производится ипередача информации, поступающей на 91 1 О985791 010 1011 01 1 О 1ропрограммы) . По окончанию формирования результата операции формируется.р признак (сигнал) конца операции, который выдается с выхода .11 блока 5,Результат операции поступает черезвыход 9 в ОЗУ, либо запоминается вблоке регистров 7,В конце цикла выборки командыи адресных преобразований операционный блок 5 возбуждает сигнал на выходе начала операций 10, по которомукод операции через первый блок элементов И 14 и блок элементов ИЛИ 24передается в регистр 25 и начинаетисполнение микропрограммы цикла ис"полнения команды. Выполнение команды в процессоре состоит из двух циклов: выборки из операти ного запоминающего устройства и преобра зования адреса и исполнения команды в соответствии с кодом операции. По этим из двух циклов работает и операционный блок 5, а управляющая часть процессора реализует две микропрограммы, соответствующие этим циклам, Через вход 3 на операционный блок поступает на ОЗУ код операции. о блок 6 началавцдает на вцперации, Ступают синхроешает прохождевыход чтенияггер 2 находити и отсутствуют наблок разсловия)ель- пере и т. упают ют хо пре- миквыход анализатора кодов и далее н, одновибратор 1. Алгоритм преобразования кодов в данном узле состоит в следующем (фиг.4).при Х =0010, Х = 1011, Х =1100,После этогход 10 сигнал овхода 4 на блок 6 посимпульсы, Блок 6 разрние этих сигналов намикрокоманд, если трися в нулевом состоянисбои при вычислениях;В процессе работы блокомвыходе 60 на основе состояни7 и сумматора 8 формируютсличные признаки (логическиенапример, м - признак отрицаного результата, Ч - признакполнения, в 1 п - признак знакЭти признаки с выхода 13 посв управляющую часть и управлдом работы устройства (т.е.деляют направления ветвления К=010, К = 100.Работа анализатора кодов может описываться следующей таблицей (при по-.даче единичного сигнала на управля ющий вход от триггера 2). В конце цикла исполнения команды,операционный блок возбуждает сигнална выходе 11 конца операции, который устанавливает в нуль регистр адреса 25 и осуществляется переход квыполнению цикла выборки следующейкоманды.В ходе выполнения микропрограммы любого из .циклов сигналы на выходах 10 и 11 блока 5 отсутствуют, 5поэтому выходом элемента ИЛИ-НЕ 22второй блок 23 элементов И открыт,Через второй блок 23 элементов И свыхода поля 29 адреса следующей микрокоманды регистра 27 на вход регистра 25 адреса поступает адрес следующей микрокоманды.Сигналы логических условий с выхода 13 операционного блока 5 поступают на входы элементов И первого з блока 34, на другие входы которых с выхода поля 30 регистра 27 в заданные моменты времени подается код проверяемых логических условий, При этом в зависимости от значений проверяемых логических условий, .которые поступают на часть входов второ. го блока 23 элементов И с выходов элементов И третьего блока 34, адрес5 следующей микрокоманды может модифицироваться.В предлагаемом процессоре осуществляются контроль последовательности микрокоманды и восстановление при сбоях.Рассмотрим работу процессора при контроле последовательности микро- команд, т,е, контроль регистра 25 и схем управления выборкой из памяти микрокоманд. На этом этапе процессор2 функционирует аналогично прототипу.Любая микропрограмма состоит из линейных последовательностей микро- команд, содержащих одну. и более микрокоманд. Порядок выполнения последовательностей определяется значениями проверямых логических условий, поступающих из операционного блока.Сущность контроля состоит в под- З 5 счете числа микрокоманд в каждой линейной последовательности, а не во всей микропрограмме и сравнении его с заданным, При несовпадении фиксируется сбой в микропрограмме с по О мощью триггера 2. Первая микрокоманда последовательности имеет формат Ф 1 (фиг,2 а). При ее выполнении с выхода поля 28 регистра 27 на вход операционного блока 5 поступают сигналы микроопераций, с выхода поля 29 считывается адрес следующей микрокоманды, а с выхода поля 30 считывается код числа микрокоманд в данной последовательности, который поступает на входы элемента И четвертого блока 37. Поскольку первый регистр 36 логических условий находится в нулевом состоянии, то по сигналу с разряда 31 регистра 27 элементы И блока 37 срабатывают и код числа микрокоманд в последовательности записывается в счетчик микрокоманд 38.После этого считывается вторая и последующие микрокоманды последовательности, которые имею 1 формат Ф 2 (фиг,2), по сигналам с выхода 12 операционного блока 5. При этом с каждой микрокомандой происходит вычитание единицы от содержимого счетчика 38 импульсом считывания с выхода 12 блока 5.Последняя микрокоманда последовательности имеет формат Ф 3 (фиг.2 в), С выхода поля 30 регистра 27 микро- команд считывается код проверяемых логических условий, который поступает на вход второго регистра условий и на входы элементов И третьего блока 34, на первые входы которыхс выхода 13 операционного блока 5 поступают сигналы логических условий,По сигналу с разряда 32 регистра 27 элементы И третьего блока 34, срответствующие единичным значениям логических условий, срабатывают и значения соответствующих логических условий записываются в первый регистрлогических условий 36, а также одновременно с этим модифицируют часть адреса следующей микрокоманды на втором блоке 23 элементов И. По сигналу с разряда 32 регистра 27 микрокоманд опрашивается элемент ИЛИ 39. Приэтом, если счетчик микрокоманд 38находится в нулевом состоянии, то число микрокоманд в последовательности соответствует заданному, Поэтому элемент И 40 не срабатывает итриггер сбоя 2 не изменяет своегосостояния. Тем самым разрешается даль.нейшая работа процессора. Если жесчетчик 38 находится не в нулевомсостоянии, то по сигналу с выходаэлемента ИЛИ 39 элемент И 40 срабатывает и через первый одновибратор 41 устанавливает триггер 2 в единицу,Фиксируя сбой, который блокируетоперационный блок 5.При нормальном функционировании процессор вновь переходит к реализации первой микрокоманды следующей последовательности с форматом Ф 1 (фиг.2 а). В этом случае с выхода поля 28 регистра 27 на вход операционного блока 5 считываются сигналы микроопераций, а с выхода поля 29 адрес следующей микрокоманды последовательности, С выхода поля 30считывается код числа микрокоманд в последовательности, которая соответствует значениям проверяемых в предыдущей микрокоманде логических условий. Этот код поступает на входы элементов И четвертого блока 37, открытых сигналом с выхода разряда 31 регистра 27, На третьи входы элементов И блока 37 поступает информа. ция с выходов первого регистра 36 1 О логицеских условий и значения проверяемых в предыдущей микрокоманде логических условий. В случае ненулевых значений логических условий сигналы с соответствующих выходов ре гистра 36 модифицируют код числа микрокоманд 8 лоследова 1 ельности, - При этом код записывается с выходов элементов И четвертого блока 37 в счетчик 38. Еали же регистр 36 на- щ ходится в нулевом состоянии (в случае, когда значения проверяемых логических условий равны нулю, либо когда предыдущая последняя микрокоманда принадлежала одной из сходя З щихся к данной первой микрокоманде ветвей микропрограммы и после этой предыдущей микрокоманды не проверялись логические условия), то в сцетцик микрокоманд 38 записывается без модификации код с выходов поля 30 регистра 27. После записи кода счетчик 38 сигналом с выхода элемента задержки 35 в первый регистр логических условий 36 устанавливается в исходное состояние.Работа процессора при восстановлении состоит в следующем.При сбое единичный сигнал с выхода триггера фиксации сбоя открывает элементы И пятого блока 16 и код .операции с регистра 15 поступает на вход анализатора кодов 19. Одновременно на третий вход анализатора кодов поступает код логицеских условий из регистра 33, При единичном сигнале от триггера Фиксации сбоя анализатор 19 кодов осуществляет анализ кодов операции и логических условий, Если анализ показывает, цто восстановление работы процессора можно осуществить с начала линейной госледовательности, то на вход блока 20 элементов И подается единицный сигнал и адрес первой микрокоманды линейной5 последовательности из регистра 18 адреса повтора церез блок 20 элементов И и блок 24 элементов ИЛИ поступает на вход регистра адреса. Одновременно сигналом из анализатора 19 кодов через одновибратор 1 триггер фиксации сбоя и второй регистр усло" вий 33 устанавливается в "0", Тем самым снимается блокировка работы операционного блока и повторяется линейная последовательность микрокоманд, Далее устройство функционирует аналогично описанному выше.Если же восстановление работы процессора возможно лишь программными средствами, то на выходе 21 анализатора 19 кодов возникает единичный сигнал и одновременно выполняется установка в нуль триггера 2 и регистра 33, При этом осуществляется повторение всей микропрограммы операции.С введением в процессор второго регистра условий, регистров кода операции и адреса повтора, анализатора кодов, блоков элементов И и ИЛИ, одновибратора и указанных связей в предлагаемом устройстве возможно восстановление работы процессора повторением линейной последовательности микрокоманд, на которой возник сбой, в то время как в прототипе повторяется выполнение всех предшествующих линейных последовательностей.Формула изобретения1. Иикропрограммный процессор с контролем, содержащий операционный блок, регистр адреса, регистр микро- команд, первый регистр логических условий, сцетчик микрокоманд, блок памяти, триггер Фиксации сбоя, первый, второй, третий и четвертый блоки элементов И, элемент ИЛИ, элемент И, элемент ИЛИ-НЕ, элемент задержки и первый одновибратор, прицем вход кода операции микропрограмм. много процессора соединен с первым входом первого блока элементов И и входом кода операции операционного блока, выход результата операции кот торого является выходом результата операции микропрограммного процессора, выход триггера фиксации сбоя соединен с управляющим входом операционного блока, выход начала операции которого соединен с вторым входом первого блока элементов И и первым входом элемента ИЛИ-НЕ, вход синхронизации микропрограммного процессора соединен с входом синхронизации операционного блока, выходконца операции которого соединен свторым входом элемента ИЛИ-НЕ и установочным входом регистра адреса, выходы адреса и микроопераций регистрамикрокоманд соединены соответственно 3с первым входом второго блока элементов И и с входом микрооперацийоперационного блока, выход итениямикрокоманд которого соединен с управляющим входом блока памяти и сиет ным входом счетчика микрокоманд, выход логических условий операционногоблока соединен с первым входом первого блока элементов И, выход которогосоединен с третьим входом второго Иблока элементов И,.выход которогосоединен с первым инФормационным входом регистра адреса, выход регистраадреса соединен с адресным входомблока памяти, выход которого соеди внен с входом регистра микрокоманд,выход логических условий регистра микрокоманд соединен с вторым входомтретьего блока элементов И и первымвходом четвертого блока элементов И, 23выход которого соединен с установоиным входом счетиика микрокоманд, первый управляющий выход регистра микрокоманд соединен с вторым входом четвертого блока элементов И и через зоэлемент задержки с установочным входом первого, регистра логииеских условий, выход которого соединен стретьим входом четвертого блока элементов И, выходы счетчика микрокомандзсоединены с входами элемента ИЛИ,выход которого соединен с первымвходом элемента И, второй управляющий выход регистра микрокоманд соединен с третьим входом третьего блокаэлементов И и вторым входом элемента И, выход которого через первыйодновибратор соединен с единичнымвходом триггера фиксации сбоя, о тл. и ч а ю щ и й с я тем, ито, сцелью повышения быстродействия восстановления выиислительного процесса при сбоях, в микропрограммныйпроцессор введены регистр кода операции, регистр адреса повтора, второй регистр логических условий, анализатор кодов, пятый, шестой и седьмой блоки элементов И, блок элементов ИЛИ и второй одновибратор, причем выход первого блока элементов Исоединен с входом. регистра кода операции и первым входом блока элементов ИЛИ, выход которого соединен свторым информационным входом регист ра адреса, выход регистра кода операции соединен с первым входом пятого блока элементов И, выход которого соединен с первым информационнымвходом анализатора кодов, единииныйвыход триггера фиксации сбоя соединен с вторым входом пятого блока элементов И и управляющим входом анализатора кодов, первый управляющий выходкоторого иерез второй одновибраторсоединен с нулевым входом триггерафиксации сбоя и установочным входомвторого регистра логических условий,выход которого соединен с вторым ин"формационным входом анализатора кодов,выход регистра адреса и первый управляющий выход регистра команд соединены соответственно с первым и вторым входами шестого блока элементовИ, выход которого соединен с входомрегистра адреса повтора, выход регистра адреса повтора соединен с первым входом седьмого блока элементовИ, выход которого соединен с вторымвходом блока элементов ИЛИ, второй,третий управляющие выходы анализато"ра кодов соединены соответственно свторым входом седьмого блока элементов И и выходом программного восстановления микропрограммного процессора,2. Процессор по п,1, о т л и и аю щ и й с я тем, ито анализатор кодов содержит первый и второй блокиэлементов И, дешифратор, первый, второй и третий элементы ИЛИ, причемпервый и второй информационные входыанализатора кодов соединены с первымивходами первого и второго блоков элементов И соответственно, выходы которых соединены соответственно спервым и вторым входами дешифратора, управляющий вход анализатора кодов соединен с вторыми входами первого и второго блоков элементов И,первая и вторая группы выходов дешифратора соединены с входами первогои второго элементов ИЛИ соответственно, выход третьего элемента ИЛИ является первым управляющим выходоманализатора кодов, выход первогоэлемента ИЛИ соединен с первым входом третьего элемента ИЛИ и являетсявторым управляющим выходом анализатора. кодов, выход второго элементаИЛИ соединен с вторым входом третьего элемента ИЛИ и является третьим управляющим выходом анализаторакодов.

СмотретьЗаявка

3310256, 02.07.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ПЛАХТЕЕВ АНАТОЛИЙ ПАВЛОВИЧ

МПК / Метки

МПК: G06F 15/20

Метки: контролем, микропрограммный, процессор

Опубликовано: 30.12.1982

Код ссылки

<a href="https://patents.su/13-985791-mikroprogrammnyjj-processor-s-kontrolem.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор с контролем</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для цифрового функционального преобразования

Случайный патент: Стенд для исследования торцового выпуска руды