Систолический процессор для вычисления четырехточечного дискретного преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

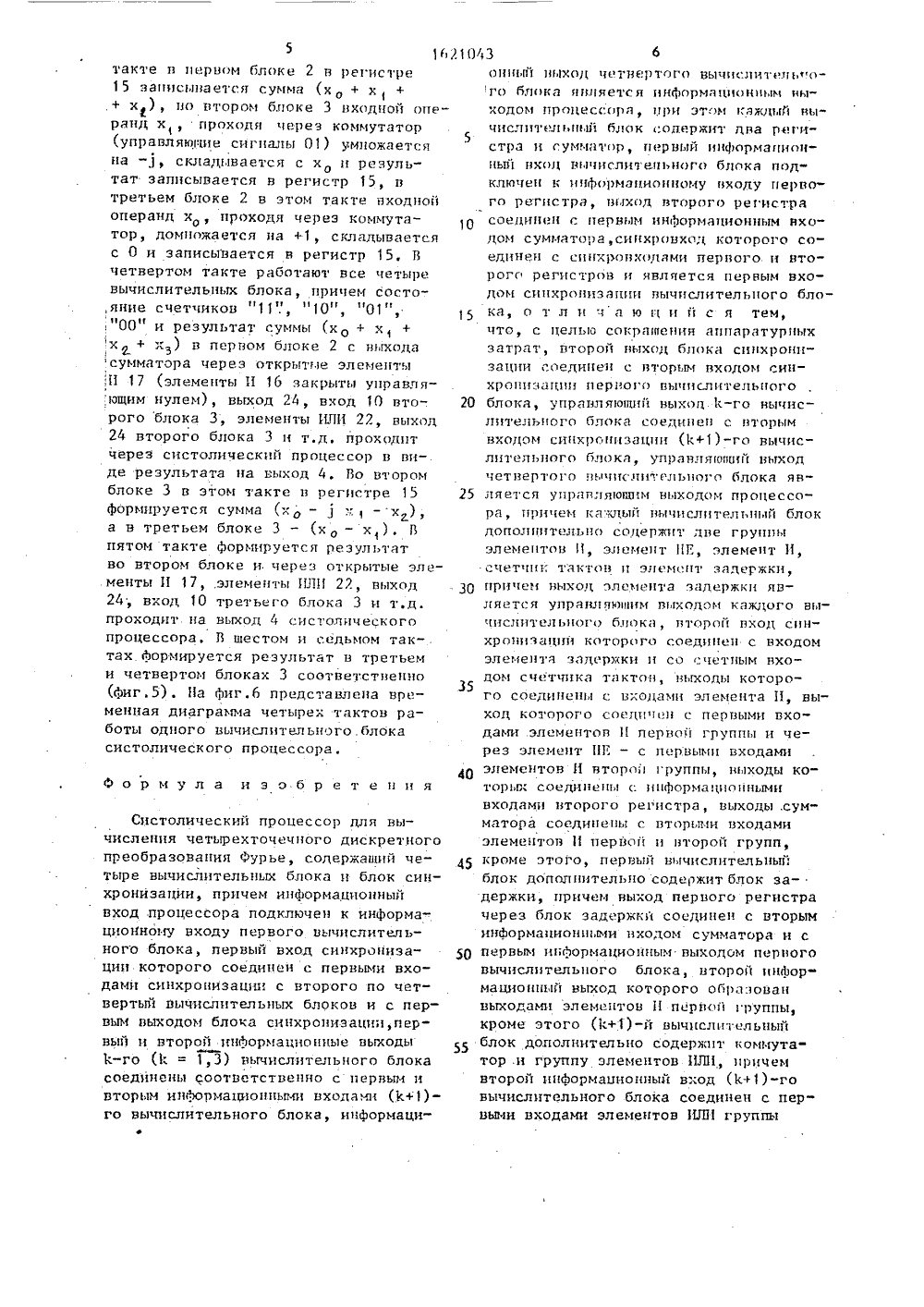

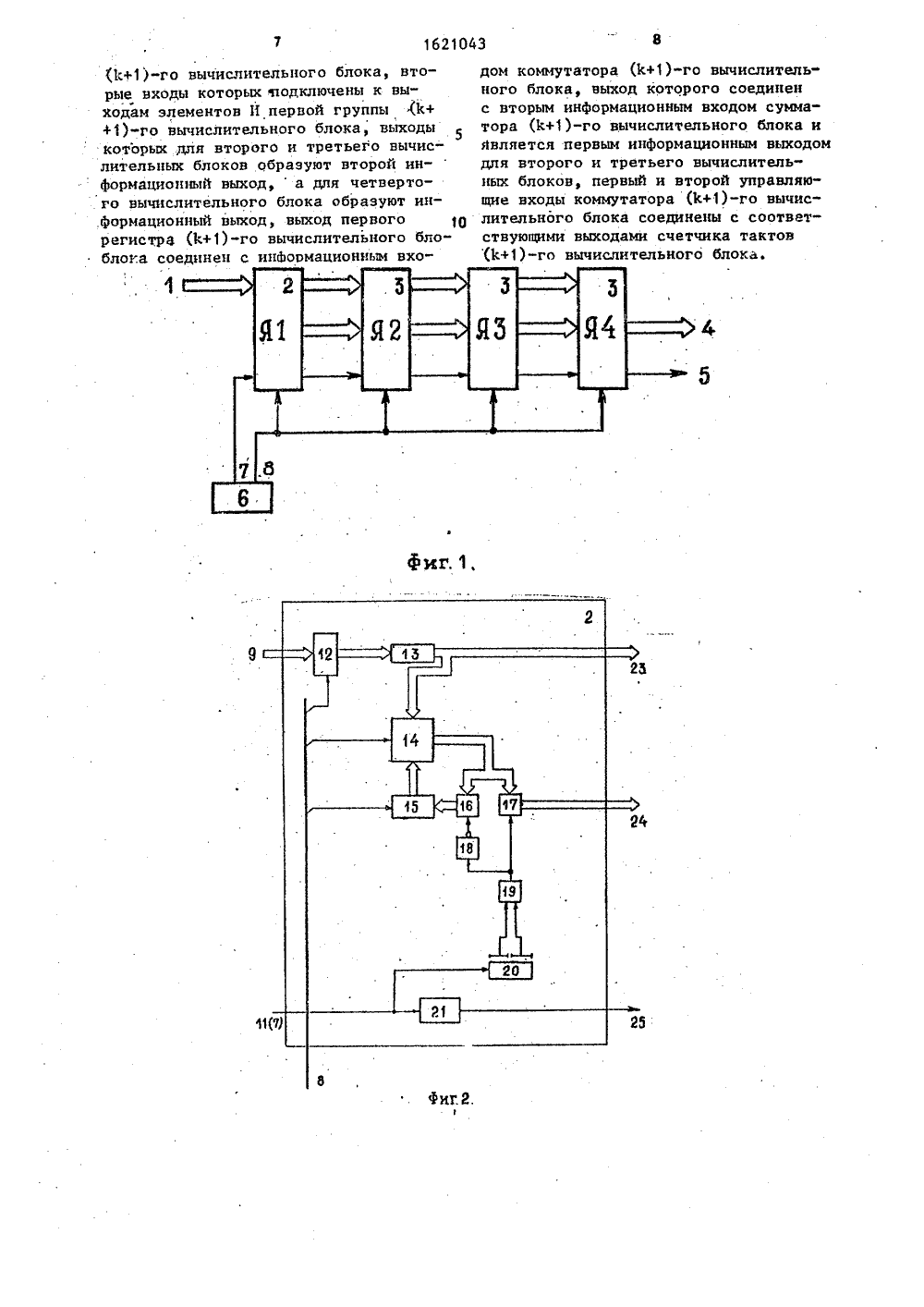

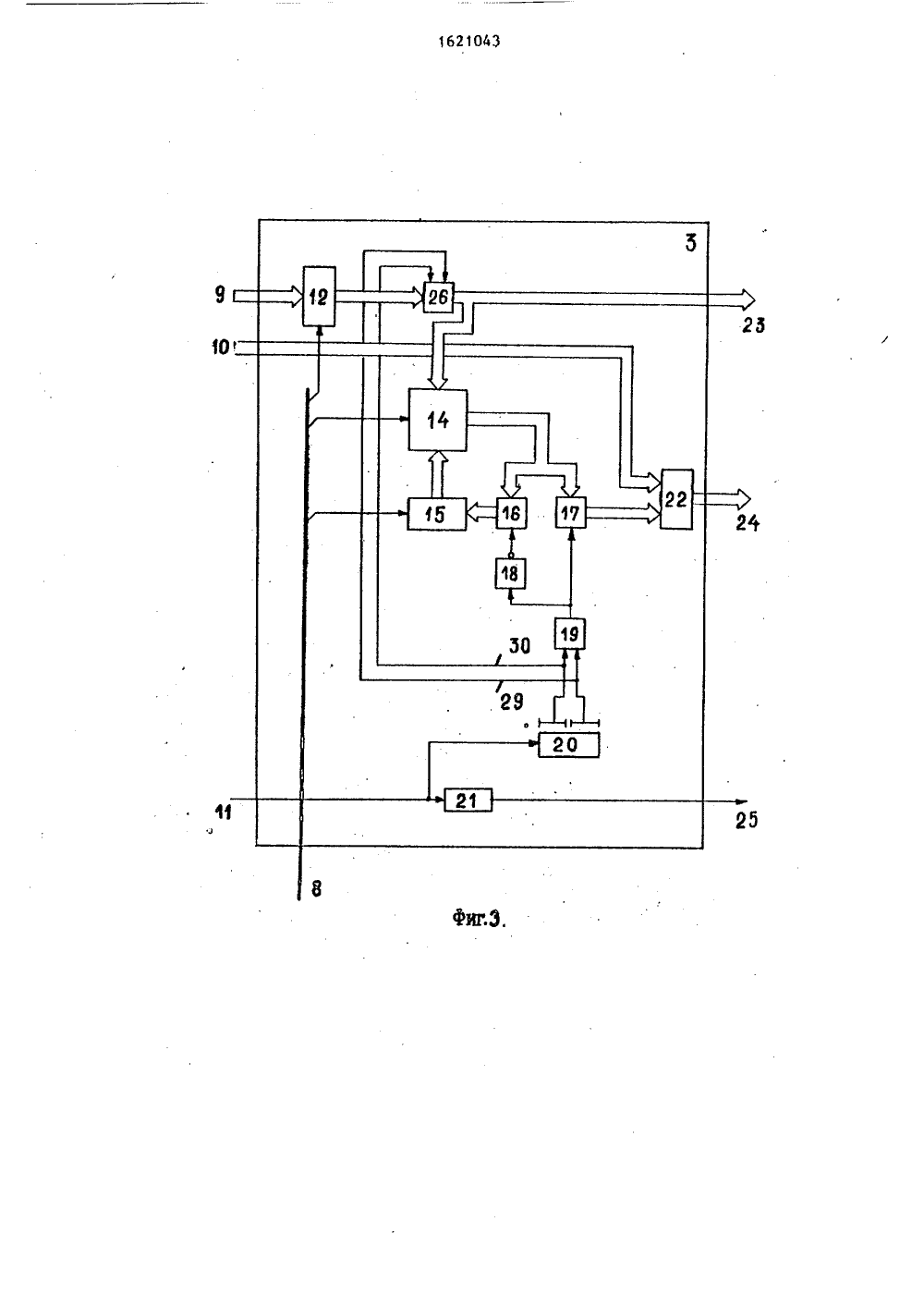

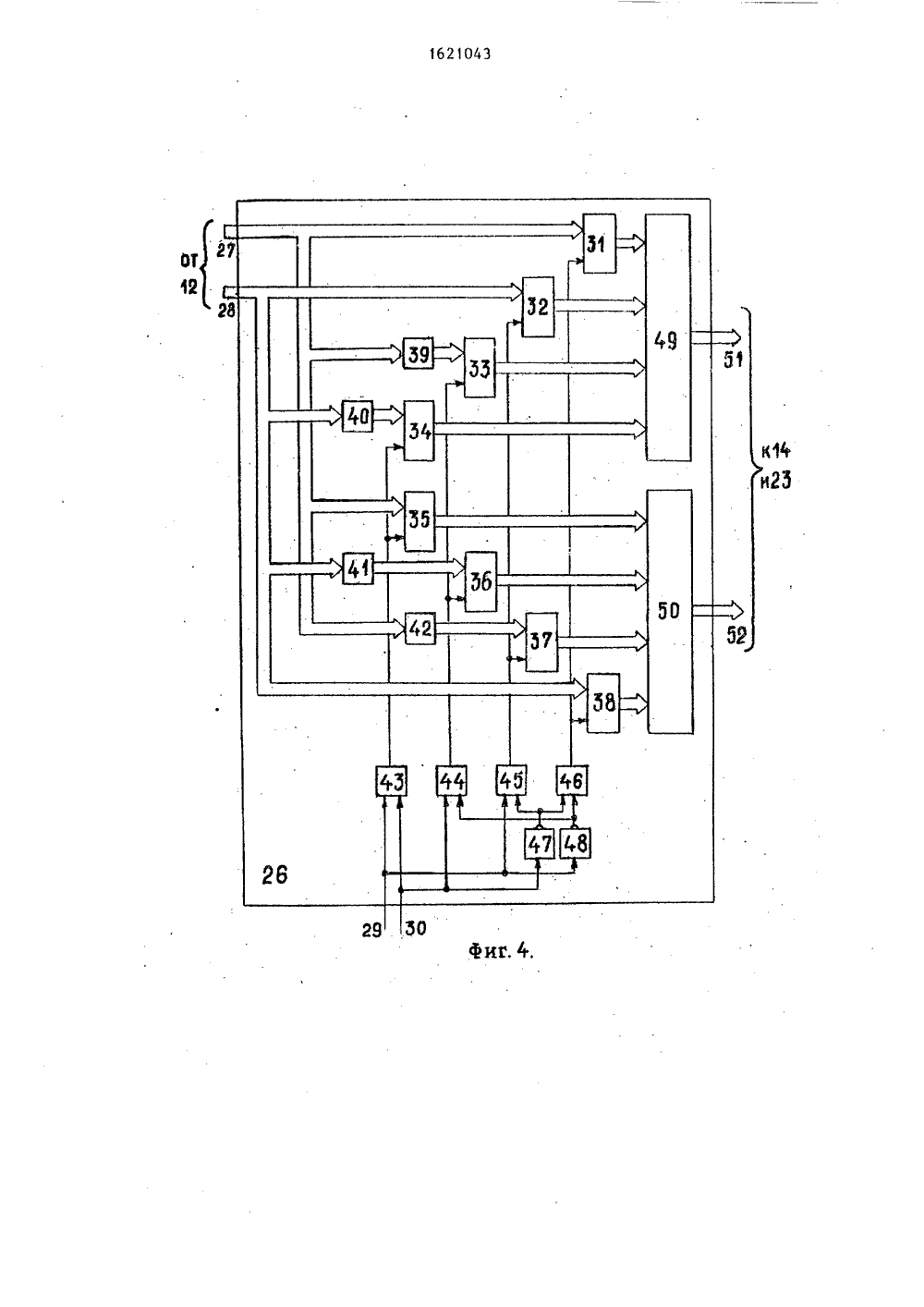

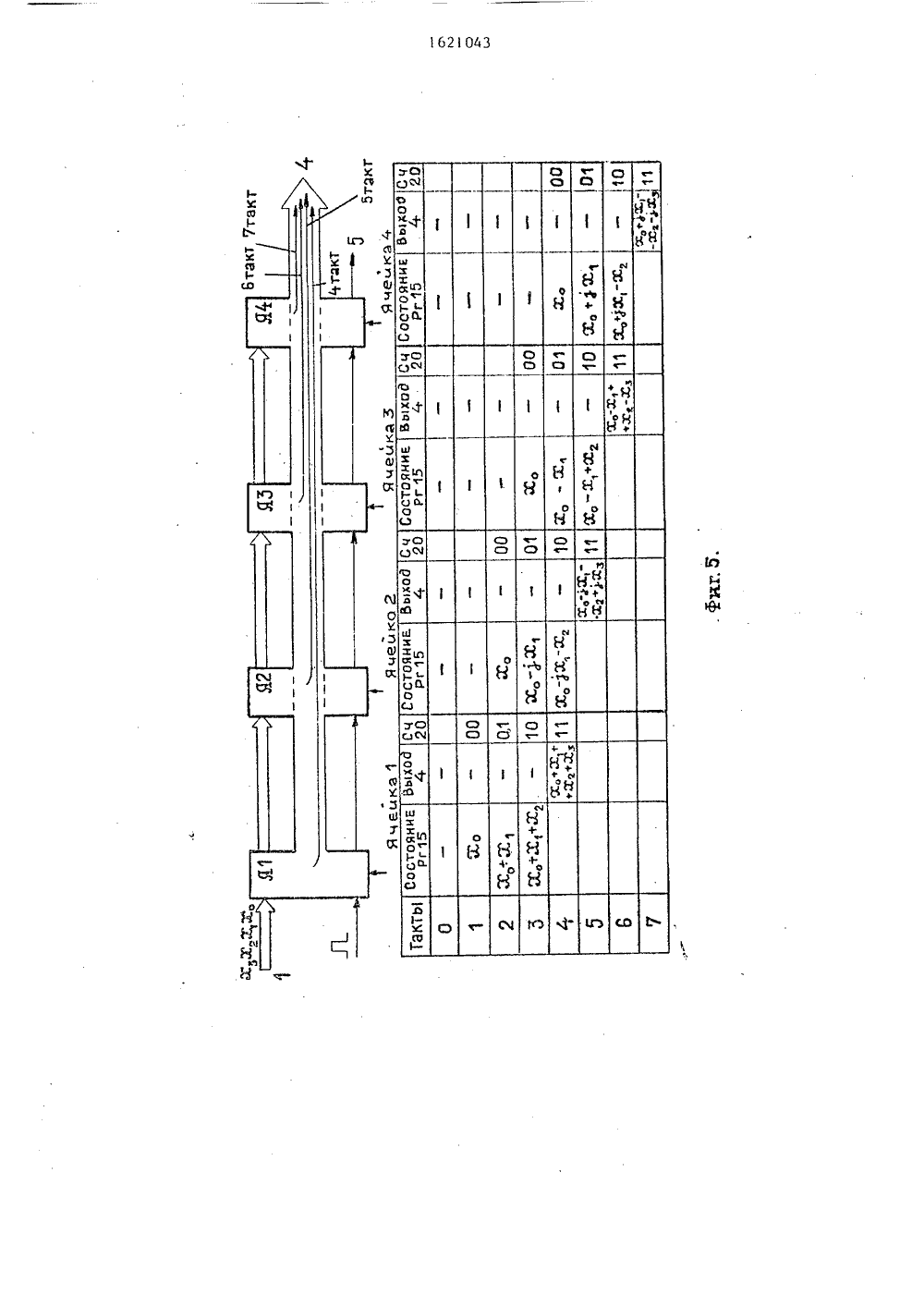

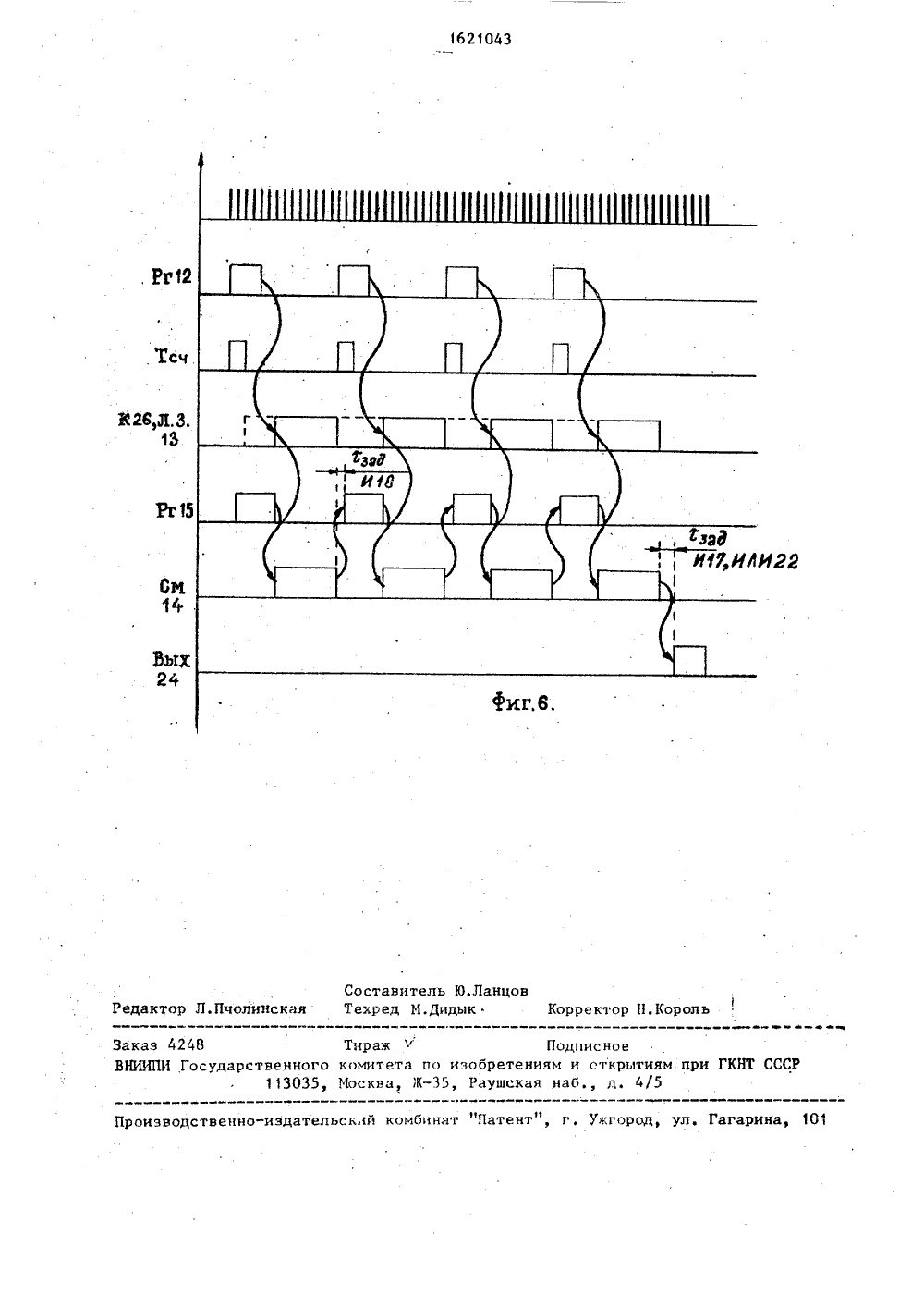

(1)5 С 06 Р 15/33 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИЯ А ВТОРСКОМ,К СВИДЕТЕЛЬСТ(71) Ленинградский институт точноймеханики и оптики(56) Авторское свидетельство СССР1196894, кл. Г 06 Р 15/332, 1983.Тезисы докладов Всесоюзной конференции 1 етоды и микроэлектронныесредства цифрового преобразованияобработки сигналов.Рига. 1986,с.504-507,(54) СИСТОЛИЧЕСКИЙ ПРОЦЕССОР ДЛЯ ВЫЧИСЛЕ 1 ПЯ 1 ЕТ 11 РЕХТО 1 ЕЧНО ГО ДИСКРЕТНОГОПРЕОБРАЗОВАНИЯ ФУРЬЕ Изобретение отнсоится к вычислительной технике и может быть использовано в специализированных системах обработки сигналов высокойпроизводительности.Цель изобретения - сокращение аппаратурньгх затрат. "Па фиг.1. представлена функциональная схема систолического процессора четырехточечного дискретного преобразования Фурье; на фиг.2 - функционапьная схема первого вычислительного блока", на фиг.3 - функциональная схема (к+1)-го (1 с = 1, 3) вычислительного блока; на фиг.4 - функциональная схема коммутатора; на фиг.5 - динамика работы вычислительных блоков по тактам; на фиг,б - временная диаграмма работы вычислительных блоков. 2(57) Изобретение относится к вычислительной технике и может быль использовано в специапизцрованных системах обработки сигналов высокой производительности, Целью изобретения является сокращение аппаратурных затрат за счет выведения цз структуры систолического процессора умножителей. Поставленная цель достигается тем, что н сцстолцческом процессоре для вычисления четырехточьчного ДПФ, со- стоящем из четырех линейно связанных вычислцтельных блоков, каждая ячейка матрицы содержит дополнительно группу элементов ИЛИ, коммутатор, две группы элементов И, элемент И, элемент Н 1:, блок задержки тактов, элемент задержки. б ил ., 1 табл. Процессор содержит информационный вход 1, первый вычислительный блок 2, с второго по четвертый вычислительные блоки 3, информационный выход 4, упранляюций выход 5, блок б синхронизации,второй 7 и первыц 8 выходы блока синхронизации.Вычислительные блоки 2 и 3 содержат информационные входы 9 и 10, второй вход 11 синхронизации,первый регистр 12, блок 13 задержки, сумматор 14, второй регистр 15, группы 16 и 17 элементов И, элемент НЕ 18, элемент И 19, счетчик 20, элемент 21 задержки, группу 22 элементов ИЛИ, чнформационные выходы 23, 24, управляюпвлй выход 25 и коммутатор 26.Коммутатор 26 содержит входы 27 и 28 вецестненной и мнимой частей комплексного числа, управляющие входы 29(2) Умножен:е 51 52 27 28 Е К,векторы размера 4 х 1,2 инфорической еделя ист ретных экспоненФ) 4-го порядкак иг= К,1:оа У ККоЪ ч К Ч К,К,(-Ь); и 30, группы элементов И 31-38, группы элементов НЕ 39 42, элементы И 43 - 46, элементы ИЕ 47 и 48, группыэлементов ИЛИ 49 и 50 и выходы 51 и 52 (фиг.4).Систолическиц процессор четырех- точечного дискретного преобразования Фурье работает следующим образом,Устройство осуществляет выполнение 10 процедуры ДПФ: где С и Х - четырехкомпоцентные векторы, т.е.компоненты которых опмацию на входе ивыходматрицы;Е - матрица дискФциальцых функций (ДЗс элементами 1 = И/4); 1,и б О 3, т е,Умножение осуществляется на тривиальные множители 1,"1, 3, -1, Голь умножителя в предлагаемой систолической матцице выполняет коммутатор 26. " Компоненты вектора входных данных представляют собой комплексные числа, т.е. х = а + 3 Ь,где а = Ре(х) вещественная, а Ь = 1 о,(х) - мнимая части комплексного числа, На входы 27 и 28 коммутатора поступают вещественная а и мнимая Ъ части комплексного операнда х. В качестве инициирующих сигналов коммутатора выступают сигналы К и ".1 двухразрядного счет чика 20 и в зависимости от комбинации К К 1 (см. таблицу) формируется рельтат Ч 1 и . на выходах 51 и 52 коммутатора 26 соответственно, а именно; 5 ) У = К,К,Ь Ч К 1 Ко(-а) М ККо(-Ь)Ч где 7и У, - функция коммутаторапо выходам.1",1:о Вход комму Выход комму татора татора.01 а Ь310 а 3 Ь -111 а 1 Ъ +1 Входнои операнд х поступает на входной регистр 12 первого блока 2 (фиг,2) в первый такт времени (фиг,5) и с задержкой на блоке 13, равной задержке коммутатора 26, передается на выход 23 блока 2 и соответственно ца регистр 12 второго блока 3, а также поступает на первый вход сумматора 14В первом такте просходит сложение хо с О, поступающим на второй вход сумматора из регистра 15, далее с выхода сумматора хо поступает через открытую группу элементов И 16 на информационный вход регистра 15. В первом такте времени состояние счетчика "00" и, следовательно, на вторых входах элементов И 17, имеются запрещающие "0", а ца вторых входах И 16 - разрешающие "1". Во втором такте включается в работу второй блок 3 (фиг.3), при этом счетный импульс с задержкой в один такт ца элементе 21 первого блока 2 приходит ца счетный вход счетчика 20 второго блока 3, В этом такте состояние счетчика первого блока "01", а второго блока - "00". Таким образом, входной операнд хо во втором блоке, проходя через коммутатор 26 (управляющие сигналы "00") умножается на +1, в первом блоке во втором такте происходит сложение входного операнда х с накопленным х и запись хо + х в регистр "5. В третьем такте (фиг.5) включается в работу третий блок 3, при этом с учетом задержки счетного импульса состояние счетчиков первого, второго и третьего вычислительных блоков "10" "01", "00. В этомА 2такте в цером блоке 2 в регистре 15 зацисыается сумма (х о + х+ + х ), о втором блоке 3 входной операнд х, проходя через коммутатор (управляющие сигналы 01) умножается на "1, складивается с х и результат записывается в регистр 15, в третьем блоке 2 в этом такте входной операнд х, проходя через коммутатор, домцожается на +1, складывается с 0 и записывается в регистр 15. В четвертом такте работают все четыре вычислительных блока, причем состо,яние счетчиков "11"., "10", "01", "00" и результат суммы (х + х, + х + х.) в пером блоке 2 с выхода сул 1 матора через открытые элементы ,И 17 (элементы И 1 б закрыты управляющим нулем), выход 24, вход 10 вто-. рого блока 3, элементы ИЛИ 22, выход 24 второго блока 3 и т.д, проходит через систолический процессор в виде результата на выход 4. Во втором блоке 3 в этом такте в регистре 15 формируется сумма (х -.;. в х ), а в третьем блоке 3 - (хо - х). В пятом такте форлпруетс я ре з ул ьтат во втором блоке и. через открытые элементы И 1 7, .элементы ИЛИ 22, выход 24, вход 10 третьего блока 3 и т,д. проходит на выход 4 систолического процессора. В шестом и седьмом так-. тах форсмируется результат в третьем и четвертом блоках 3 соответственно (фиг.5). На фиг.6 представлена временная диаграмма четырех тактов работы одного вычислительного. блока систолического процессора. Формула изобретения1043оцгпп ыход четвертого Вьчислите ьфого блока яляется ннфорл 1 ационилм ныходом процессора, при этом каждый вычислительный блок содержит л,па регистра и сумматор, первый информационныц ход вычислительного блсдка подключен ь информационному ходу первого регистра, ыход второго регистра 1015 20303540 соединен с первым информационным входом сумматора,сицхровход которого соединен с синхропходдми первого.и второгс регистров и является первым входом сицхроцизапии пычислительиого блока, о т л и ч д ю щ и й с я тем, что, с целью сокращения аппардтурцых затрат, второй выход блока синхронизации соедицец с вторым входом синхрониздцгцю первого вычислительного блока, упрдвляющиц ыхоп 1 с-го пычислнтельцого блока соединен с торымвходом синхронизации (1 с+1) ГО Вычислитсдлы ого блока, управляющий выходчетвертого пычислич. елього блока является управляющим выходом процессора, причем каждый ычислительцый блокдополнительно содержит две груги 1 ыэлементов И, элемент НГ, элемент И,счетчик тактов и элемент задержки,причем выход элемента задержки является управляющим выходом каждого аычислителдцоо блока, торой ход хроцизацни которого соединен с входом элемента задсржки и со счетным входом счетчика тактов, ыходы которого соединены с входами эледлента И, выход которого соедн ец с первыми входалпл элементов И первой группы и через элемент НГ - с первыми входами элементов И второй группы, пыходы которьг соединены с информационными входами тораго регистра, выходы .сум50 55 Систолический процессор для вычисления четырехточечцого дискретного преобразования Фурье, содержащий четыре вычислительных блока и блок синХронизации, причем информациоцный вход процессора подключен к информациоцному входу первого вычислительного блока, первый вход синхронизации которого соединен с первыми входами синхронизации с второго по четвертый вычислительных блоков и с первым выходом блока синхроцизацци,первый и второй информационные вьгходы 1 с-го (Е = 1,3) вычислительного блока соединены соответственно с первым и вторым информационными входами (1 с+)- го вычислительного блока, ицформациматора соединены с вторыми входамиэлементо И первой и торой групп,кроме этого, первый вычислительныйблок дополнительно содержит блок задержки, причем выход первого регистра через блок задержкй соединен с вторым информационными ходом сумматора и с первым информационным выкодом первого вычислительного блока, второй ицформациогиилй выход которого о 61 дзован выходами элементов И первой группы, кроме этого О+1)-й вычислительный блок дополнительно содержит коммутатор .и группу элементов ИЛИ, нрцчем второй информационный вход (с+1)-го вычислительного блока соединен с первыми входами элементов ИЛИ группы(1 с+1)-го вычислительного блока, вторые входы которых подключены к выходам элементов Й первой группы Ф+4 1)-го вычислительного блока, выходыкоторых дпя второго и третьего вычислительных блоков образуют второй информационный выход,а для четвертого вычислительного блока образуют инФормационный выход, выход первого 1 Орегистра (1+1)-го вычислительного блоблока соединен с инйоомационным входом коммутатора (М 1)-го вычислительного блока, выход которого соединенс вторым информационным входом сумматора (1+1)-го вычислительного блока иявляется первым информационным выходомдля второго и третьего вычислительных блоков, первый и второй управляющие входы коммутатора Ос+1)-го вычислительного блока соединены с соответствующими выходами счетчика тактовЬ 1)-го вычислительного блока.1621043 И 22 Составитель Ю.Ланцовктор Л,Пчолинская Техред Г 1.Дидык Корректор Н.Коро одписн СССР при ГКНТ Гос н нПроизводственно-издательский комбинат 11 атент , г. Ужгород, ул. Гагарина, 1 И 26,Л.З 1 З

СмотретьЗаявка

4458080, 23.05.1988

ЛЕНИНГРАДСКИЙ ИНСТИТУТ ТОЧНОЙ МЕХАНИКИ И ОПТИКИ

КУХАРЕВ ГЕОРГИЙ АЛЕКСАНДРОВИЧ, НОВОСЕЛОВ НИКОЛАЙ ДМИТРИЕВИЧ, ТРОПЧЕНКО АЛЕКСАНДР ЮВЕНАЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/332

Метки: вычисления, дискретного, преобразования, процессор, систолический, фурье, четырехточечного

Опубликовано: 15.01.1991

Код ссылки

<a href="https://patents.su/8-1621043-sistolicheskijj-processor-dlya-vychisleniya-chetyrekhtochechnogo-diskretnogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Систолический процессор для вычисления четырехточечного дискретного преобразования фурье</a>

Предыдущий патент: Устройство для моделирования алгоритма деятельности человека-оператора

Следующий патент: Коррелятор

Случайный патент: Инерционный сепаратор пыли