Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1553984

Авторы: Дрель, Мугинштейн, Шварц

Текст

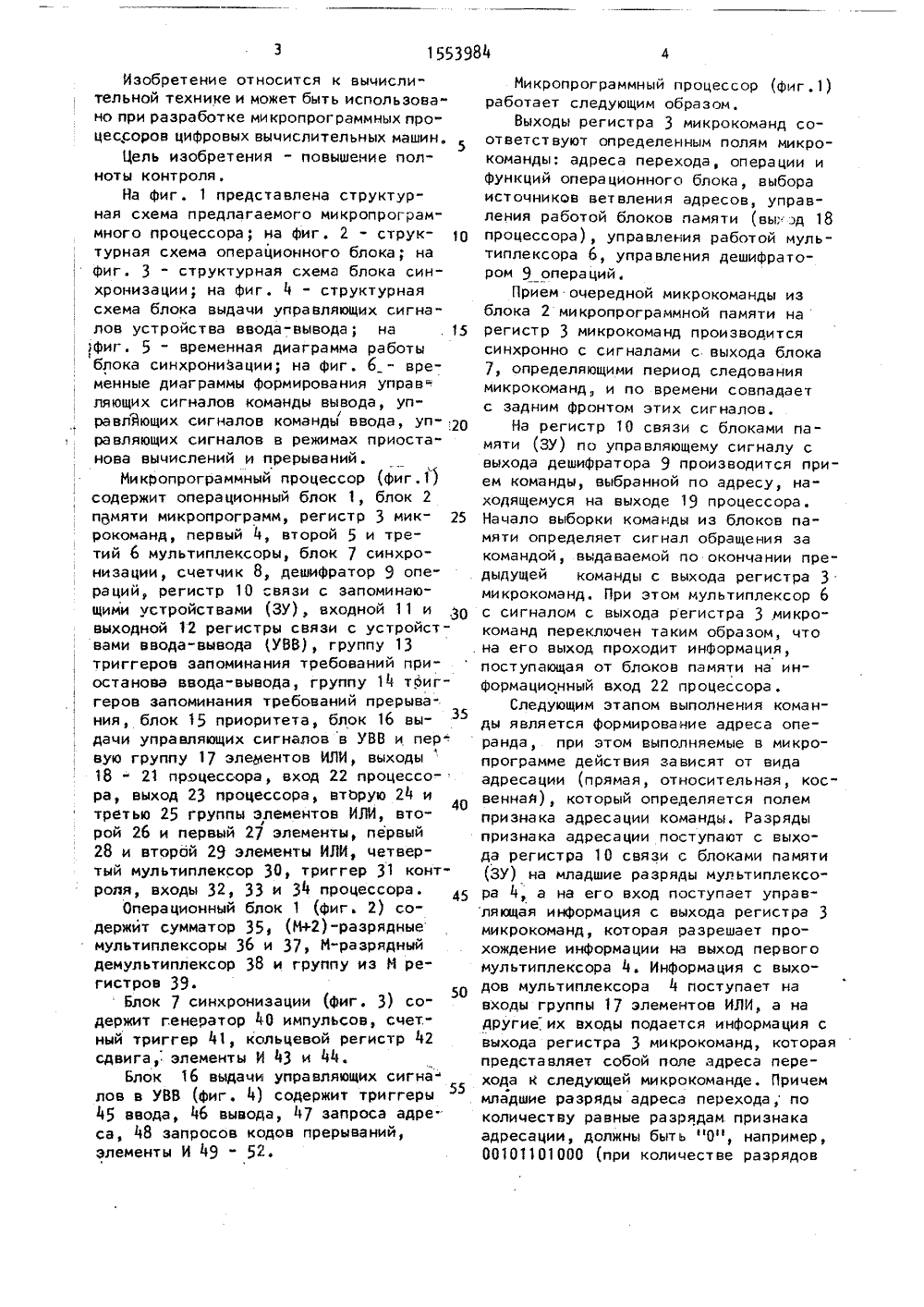

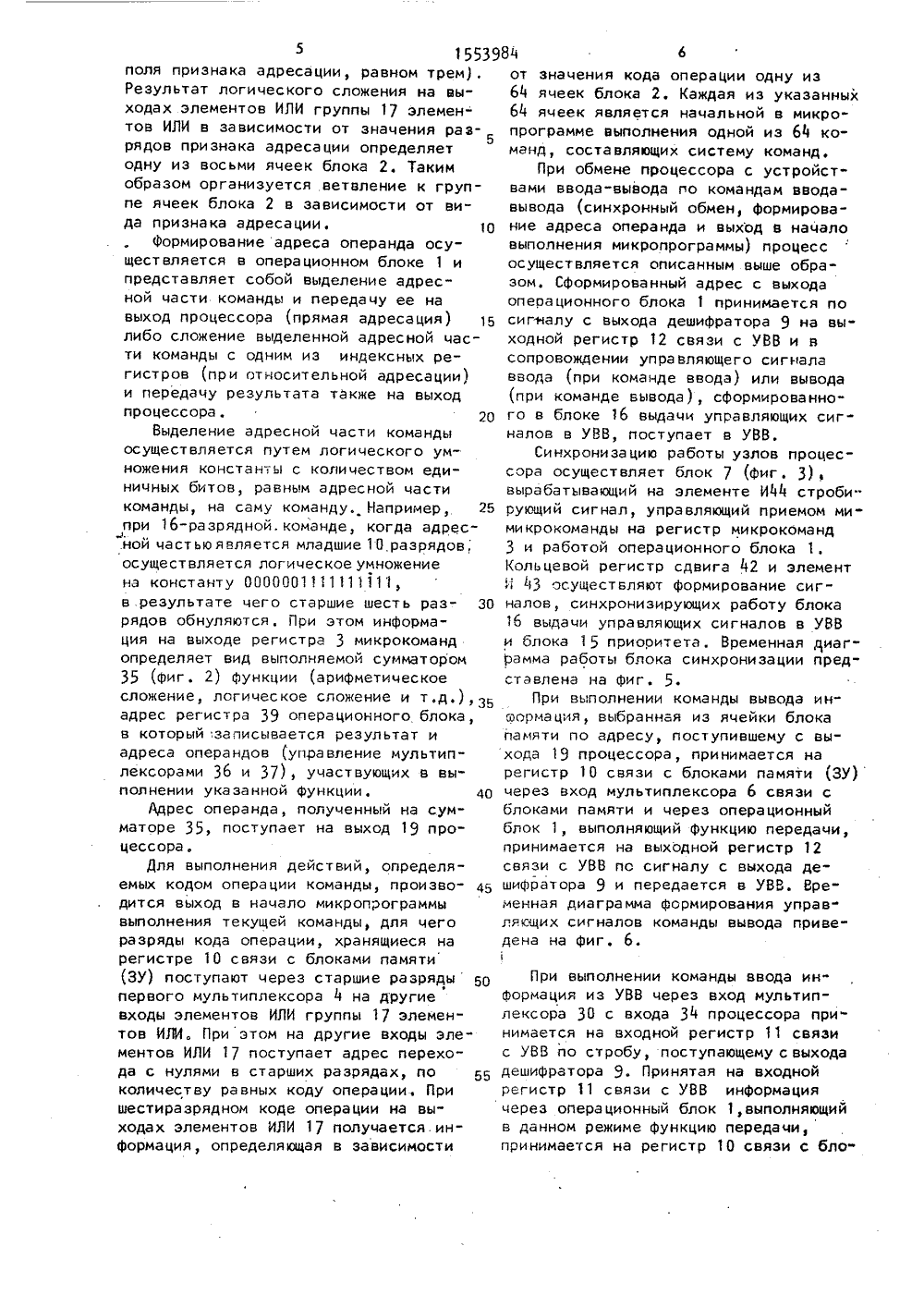

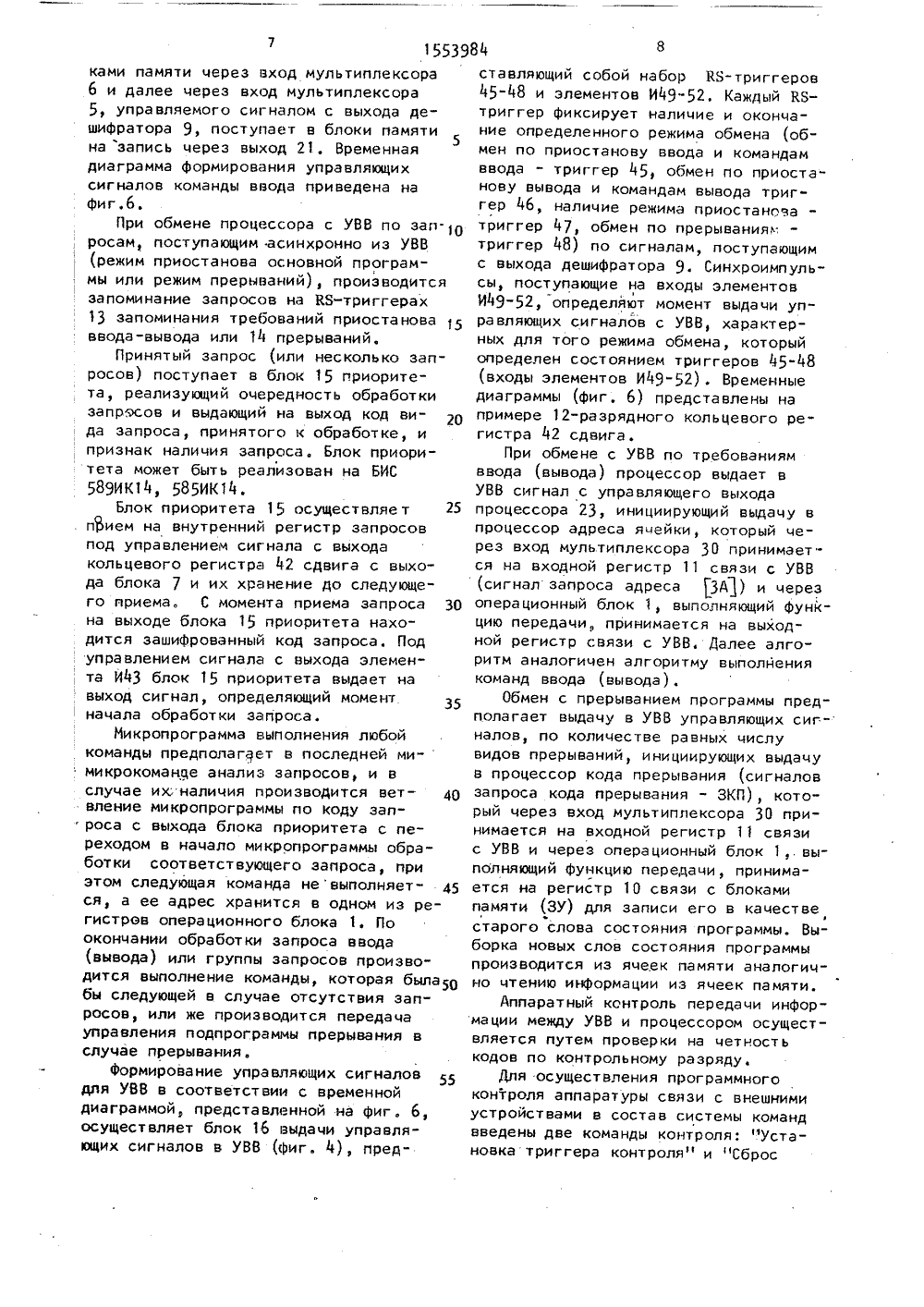

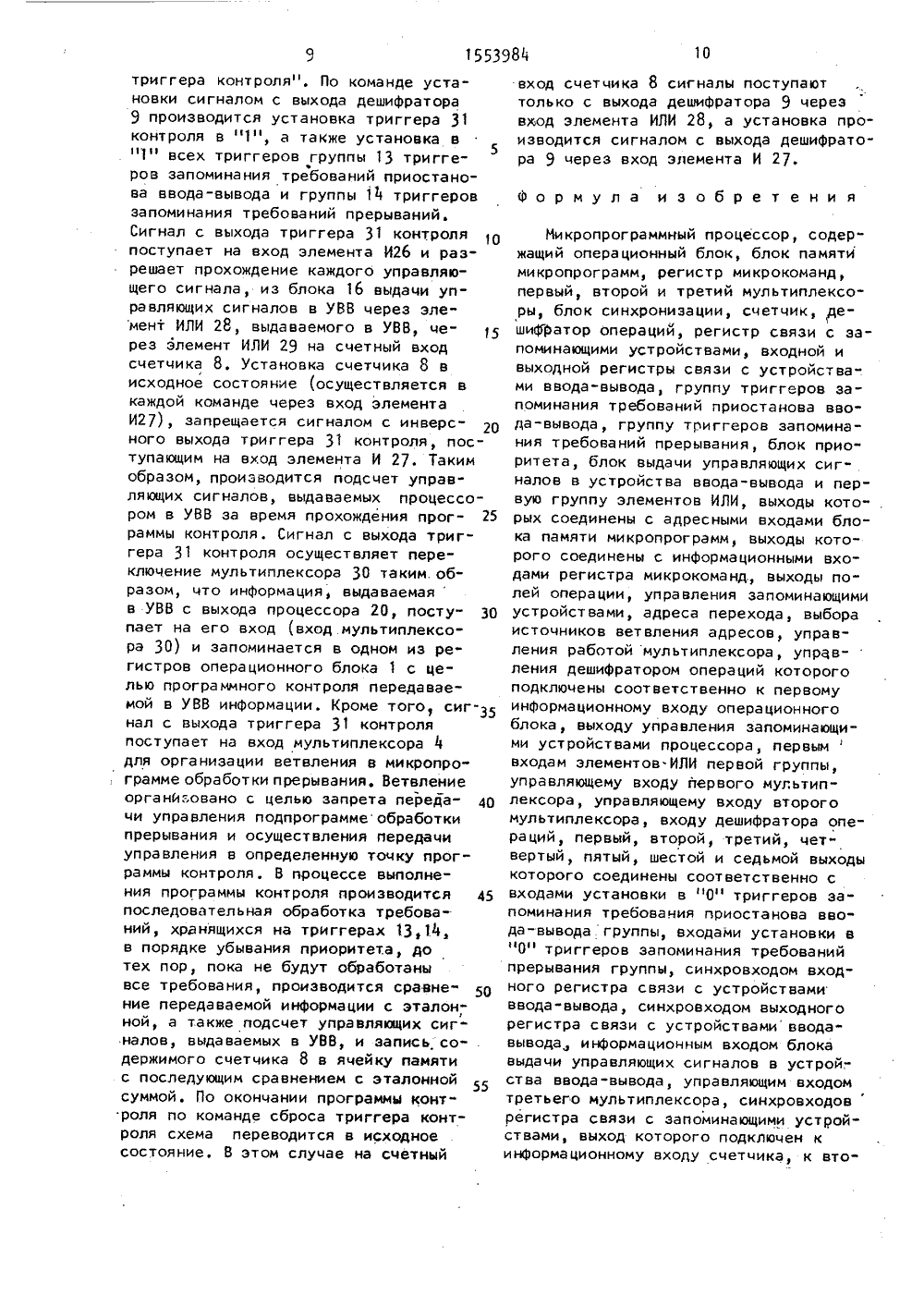

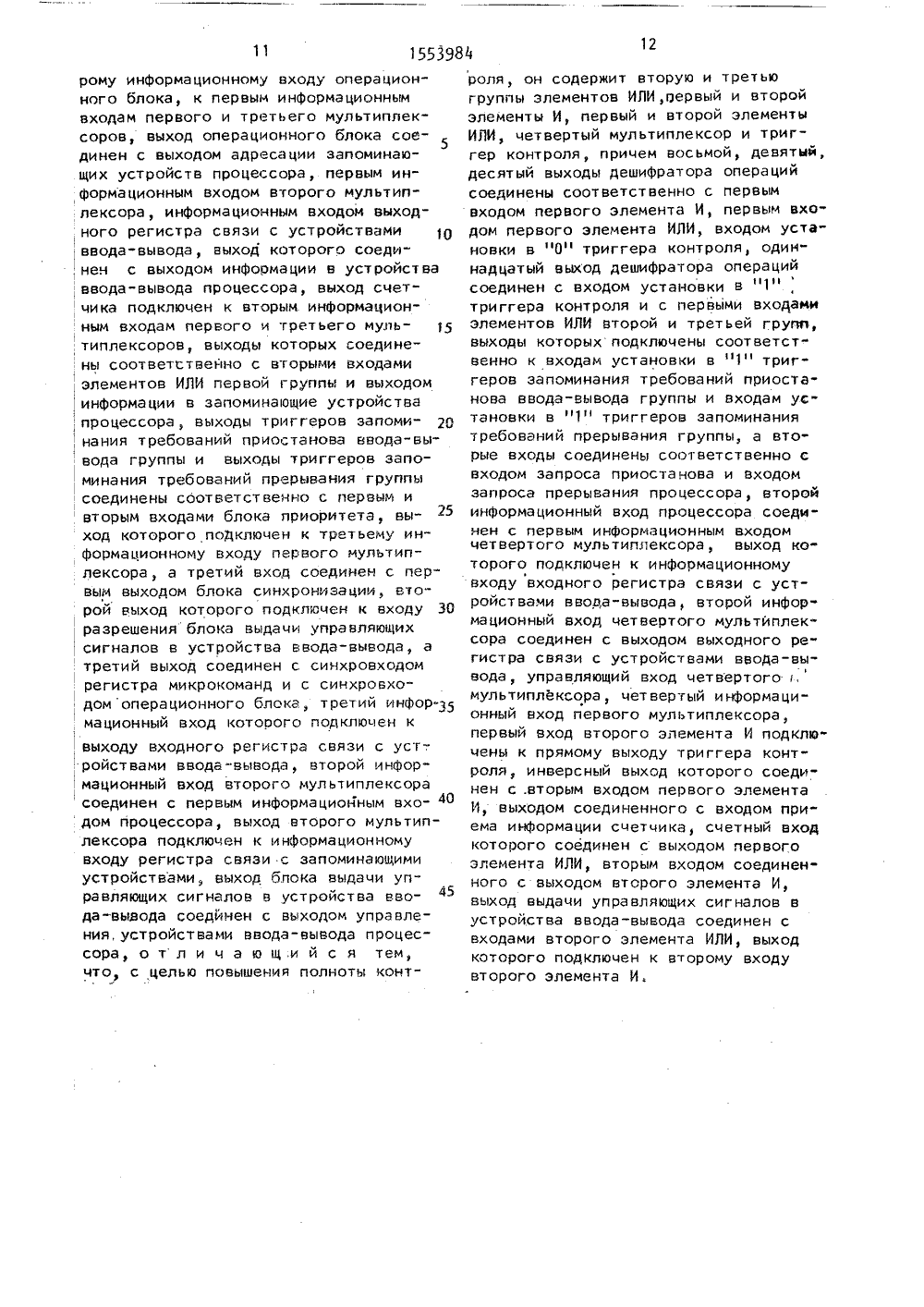

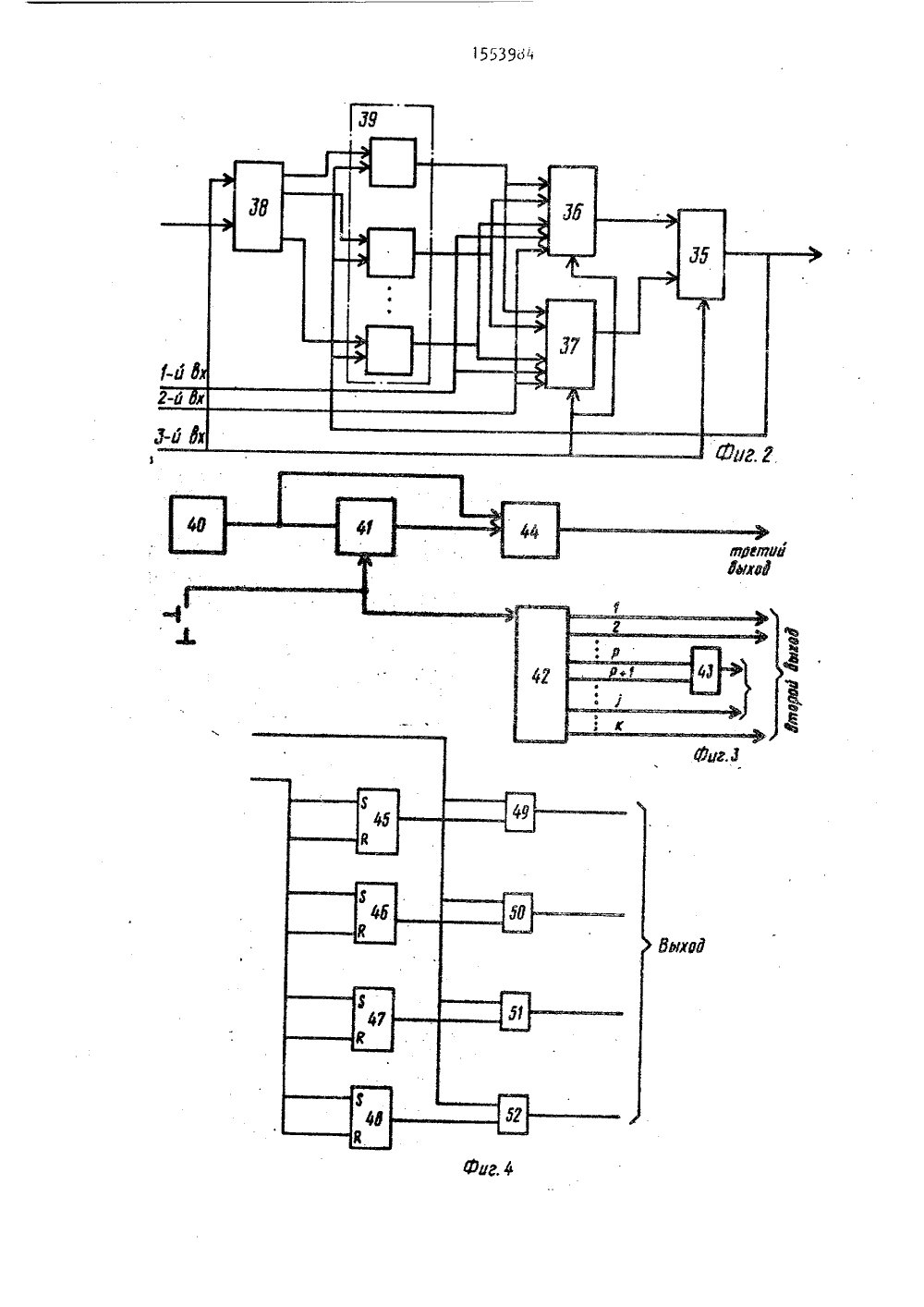

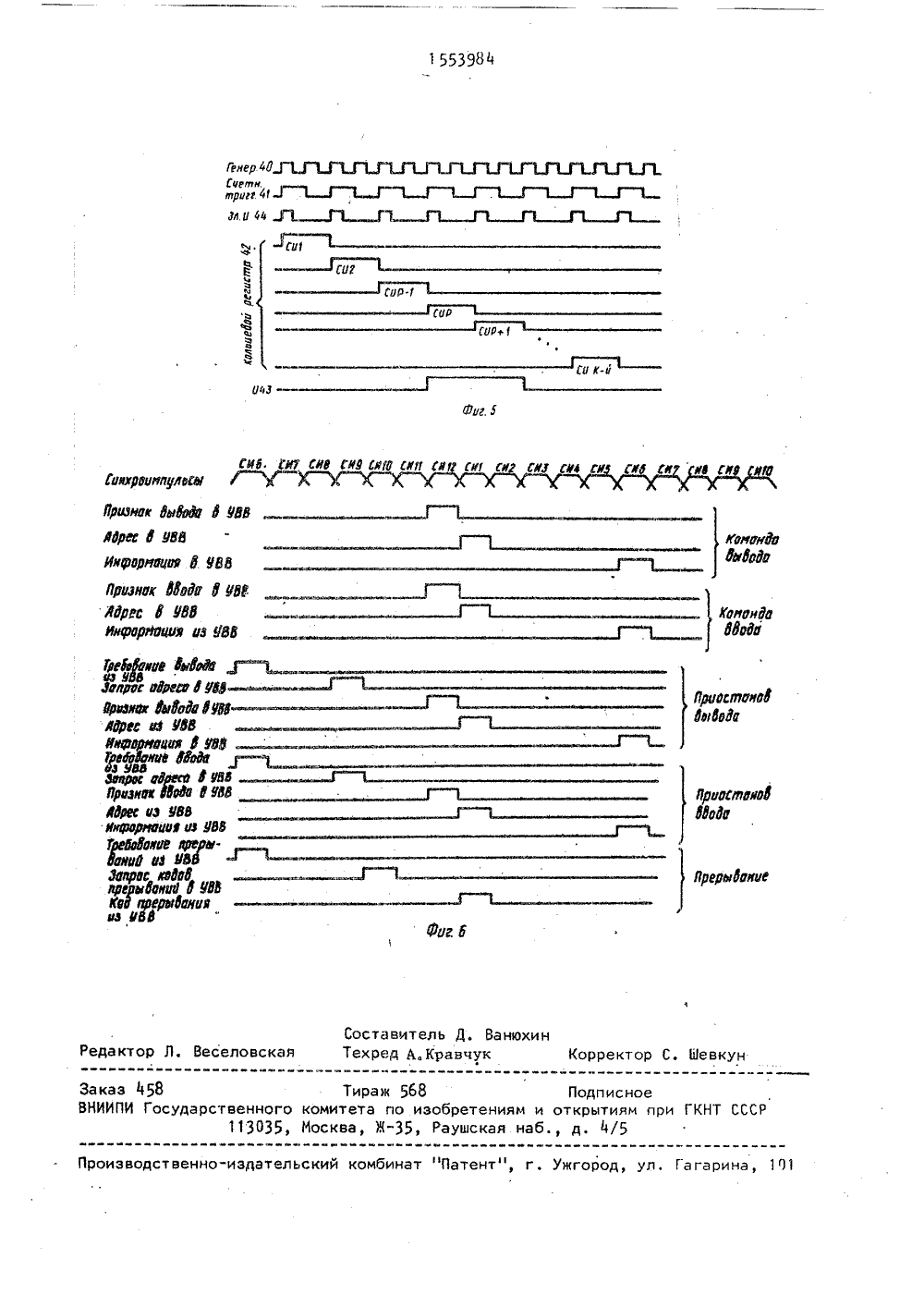

СОЮЗ СОВЕТСКИХ, ОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК ив Я 15539 15/00, 11/26 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИЯ ЕТЕЛЬСТ К АВТОРСКОМУ(56) АвторскоеИ 985791 кл,Авторское сИ 1024927, кл. юл. У 12 И.С. Мугинш свидетельство СССРС 06 Р 15/20, 1980.видетельство СССРС 06 Г 15/00; 1981.(54) МИКРОПРОГРАММНЫЙ ПРОЦЕССОР (57) Изобретение относится к вычислительной технике и может быть использовано при разработке микропрограммных процессоров цифровых вычислительных машин, Цель изобретения - повышение полноты контроля. Это достигнуто за счет подсчета управляющих сигналов, выдаваемых: в устройства ввода-вывода (УВВ), запоминания информации, переданной в УВВ, и программного анализа достоверности переданных управляющихЯф 2сигналов и информации. Микропрограммный процессор содержит операционный блок 1, блок 2 памяти микропрограмм, регистр 3 микрокоманд, первый мультиплексор 4, второй мультиплексор 5, третий мультиплексор 6, блок 7 синхронизации, счетчик 8, дешифратор 9 операций, регистр 10 связи с блоками памяти, входной регистр 11 связи с устройствами ввода-вывода, выходной регистр 12 связи с устройствами ввода-вывода, группу триггеров 13 запоминания требований приостанова, группу триггеров 14 запоминания требова" ний прерывания, блок 15 приоритета, блок 1 б выдачи управляющих сигналов в УВВ первую группу элементов ИЛИ 17. Кроме того, в процессор введены вторая и третья группы элементов ИЛИ 24, 25, второй и первый элементы И 26,27, первый и второй элеМенты ИЛИ 28,29, четвертый мультиплексор 30 и триггер контроля 31, б ил.Изобретение относится к вычислительной технике и может быть использова"но при разработке микропрограммных процессоров цифровых вычислительных машин.Цель изобретения - повышение полноты контроля,На фиг. 1 представлена структурная схема предлагаемого микропрограммного процессора; на Фиг. 2 - структурная схема операционного блока; нафиг. 3 - структурная схема блока синхронизации; на фиг. 4 - структурнаясхема блока выдачи управляющих сигналов Устройства ввода-вывода; на , 15фиг. 5 - временная диаграмма работыблока синхронизации; на фиг, б - временные диаграммы формирования управляющих сигналов команды вывода, уп/равляющих сигналов команды ввода, управляющих сигналов в режимах приостанова вычислений и прерываний.Микропрограммный процессор (фиг.1)содержит операционный блок 1, блок 2памяти микропрограмм, регистр 3 микрокоманд, первый 4, второй 5 и третий 6 мультиплексоры, блок 7 синхронизации, счетчик 8, дешифратор 9 операций, регистр 10 связи с запоминающими устройствами (ЗУ), входной 11 ивыходной 12 регистры связи с устройст -вами ввода вывода (УВВ) группу 13триггеров запоминания требований приостанова ввода-вывода, группу 14 тоиггеров запоминания требований прерыва.ния, блок 15 приоритета, блок 16 выдачи управляющих сигналов в УВВ и первую группу 17 элементов ИЛИ, выходы18 - 21 процессора, вход 22 процессора, выход 23 процессора, вторую 24 итретью 25 группы элементов ИЛИ, второй 26 и первый 27 элементы, первый28 и второй 29 элементы ИЛИ, четвертый мультиплексор 30, триггер 31 контроля, входы 32, 33 и 34 процессора, 45Операционный блок 1 (фиг. 2) содержит сумматор 35, (М+2)"разрядныемультиплексоры 36 и 37, М-разрядныйдемультиплексор 38 и группу из М регистров 39Блок 7 синхронизации (Фиг. 3) содержит генератор 40 импульсов счетный триггер 41, кольцевой регистр 42сдвига, элементы И 43 и 44,Блок 16 выдачи управляющих сигна"лов в УВВ (Фиг, 4) содержит триггеры5545 ввода, 46 вывода, 47 запроса адреса, 48 запросов кодов прерываний,элементы И 49 52Микропрограммный процессор (фиг.1) работает следующим образом.Выходы регистра 3 микрокоманд соответствуют определенным полям микро- команды; адреса перехода, операции и функций операционного блока, выбора источников ветвления адресов, управления работой блоков памяти (вы: эд 18 процессора), управления работой мультиплексора 6, управления дешифратором 9 операций.Прием очередной микрокоманды из блока 2 микропрограммной памяти на регистр 3 микрокоманд производится синхронно с сигналами с выхода блока 7, определяющими период следования микрокоманд и по времени совпадает с задним фронтом этих сигналов.На регистр 10 связи с блоками памяти (ЗУ) по управляющему сигналу с выхода дешифратора 9 производится прием команды, выбранной по адресу, находящемуся на выходе 19 процессора. Начало выборки команды из блоков памяти определяет сигнал обращения за командой, выдаваемой по окончании предыдущей команды с выхода регистра 3 микрокоманд, При этом мультиплексор 6 с сигналом с выхода регистра 3 .микро- команд переключен таким образом, что на его выход проходит информация, поступающая от блоков памяти на информационный вход 22 процессора,Следующим этапом выполнения команды является формирование адреса операнда, при этом выполняемые в микропрограмме действия зависят от вида адресации (прямая, относительная, косвенная), который определяется полем признака адресации команды. Разряды признака адресации поступают с выхода регистра 10 связи с блоками памяти (ЗУ) на младшие разряды мультиплексора 4, а на его вход поступает управляющая информация с выхода регистра 3 микрокоманд, которая разрешает прохождение информации на выход первого мультиплексора 4. Информация с выходов мультиплексора 4 поступает на входы группы 17 элементов ИЛИ, а на ДРугие, их входы подается инФормация с выхода регистра 3 микрокоманд, которая представляет собой поле адреса перехода к следующей микрокоманде. Причем младшие разряды адреса перехода, по количеству равные разрядам признака адресации, должны быть "0", например, 00101101000 (при колицестве разрядов5 15539поля признака адресации, равном трем),Результат логического сложения на выходах. элементов ИЛИ группы 17 элементов ИЛИ в зависимости от значения раз 5рядов признака адресации определяетодну из восьми яцеек блока 2. Такимобразом организуется .ветвление к группе ячеек блока 2 в зависимости от вида признака адресации. 1 ОФормирование адреса операнда осуществляется в операционном блоке 1 ипредставляет собой выделение адресной части команды и передачу ее навыход процессора (прямая адресация) 15либо сложение выделенной адресной части команды с одним из индексных регистров (при относительной адресации)и передачу результата также на выходпроцессора . 20Выделение адресной части командыосуществляется путем логического умножения константы с количеством единичных битов, равным адресной частикоманды, на саму команду. Например, 25при 16-разрядной. команде, когда адрес.ной частью является младшие 10.разрядов,осуществляется логическое умножениена константу 0000001111111111,в результате чего старшие шесть разрядов обнуляются, При этом информация на выходе регистра 3 микрокомандопределяет вид выполняемой сумматором35 (Фиг. 2) Функции (арифметическоесложение, логическое сложение и т.д,),адрес регистра 39 операционного блока,в который записывается результат иадреса операндов (управление мультиплексорами 36 и 37), участвующих в выполнении указанной функции, 40адрес операнда, полуценный на сумматоре 35, поступает на выход 19 процессора,Для выполнения действий, определяемых кодом операции команды, производится выход в начало микропрограммывыполнения текущей команды, для чегоразряды кода операции, хранящиеся нарегистре 1 О связи с блоками памяти(ЗУ) поступают через старшие разрядыпервого мультиплексора 4 на другиевходы элементов ИЛИ группы 17 элементов ИЛИ. При этом на другие входы элементов ИЛИ 17 поступает адрес перехода с нулями в старших разрядах, поколичеству равных коду операции, Пришестиразрядном коде операции на выходах элементов ИЛИ 17 получается.информация, определяющая в зависимости от значения кода операции одну иэ 64 ячеек блока 2. Каждая из укаэанных 64 ячеек является начальной в микропрограмме выполнения одной из 64 команд, составляющих систему команд.При обмене процессора с устройст" вами ввода-вывода по командам ввода- вывода (синхронный обмен, формирование адреса операнда и выход в начало выполнения микропрограммы) процесс осуществляется описанным выше образом. Сформированный адрес с выхода операционного блока 1 принимается по сигналу с выхода дешифратора 9 на выходной регистр 12 связи с УВВ и в сопровождении управляющего сигнала ввода (при команде ввода) или вывода (при команде вывода), сформированного в блоке 16 выдачи управляющих сигналов в УВВ, поступает в УВВ.Синхронизацию работы узлов процессора осуществляет блок 7 (Фиг. 3)вырабатывающий на элементе И 44 стробирующий сигнал, управляющий приемом мимикрокоманды на регистр микрокоманд 3 и работой операционного блока Кольцевой регистр сдвига 42 и элемент И 43 осуществляют Формирование сигналов, синхронизирующих работу блока 16 выдачи управляющих сигналов в УВВ и блока 15 приоритета. Временная диаг 1 амма работы блока синхронизации представлена на Фиг. 5.При выполнении команды вывода ин" яормация, выбранная из ячейки блока памяти по адресу, поступившему с выхода 19 процессора, принимается на регистр 10 связи с блоками памяти (ЗУ) церез вход мультиплексора 6 связи с блоками памяти и через операционный блок 1, выполняющий Функцию передачи, принимается на выходной регистр 12 связи с УВВ по сигналу с выхода дешифратора 9 и передается в УВВ, Временная диаграмма формирования управляющих сигналов команды вывода приведена на Фиг. 6. При выполнении команды ввода информация иэ УВВ через вход мультиплексора 30 с входа 34 процессора принимается на входной регистр 11 связи с УВВ по стробу, поступающему с выхода дешифратора 9. Принятая на входной регистр 11 связи с УВВ информация через операционный блок 1,выполняющий в данном режиме функцию передачи, принимается на регистр 1 О связи с бло1553984 ками памяти через вход мультиплексора6 и далее через вход мультиплексора5, упра вляемого сигналом с выхода дешифратора 9, поступает в блоки памятина запись через выход 21, Временнаядиаграмма формирования управляющихсигналов команды ввода приведена нафиг.6.При обмене процессора с УВВ по запросам, поступающим асинхронно из УВВ(режим приостанова основной программы или режим прерываний), производитсязапоминание запросов на НЗ-триггерах13 запоминания требований приостановаввода-вывода или 14 прерываний,Принятый запрос (или несколько запросов) поступает в блок 15 приоритета, реализующий очередность обработкизапросов и выдающий на выход код вида запроса, принятого к обработке, ипризнак наличия запроса. Блок приоритета может быть реализован на БИС589 ИК 14 585 ИК 14.Блок приоритета 15 осуществляет. прием на внутренний регистр запросовпод управлением сиг нала с выходакольцевого регистра 42 сдвига с выхода блока 7 и их хранение до следующего приема. С момента приема запросана выходе блока 15 приоритета находится зашифрованный код запроса. Подуправлением сигнала с выхода элемента И 43 блок 15 приоритета выдает навыход сигнал, определяющий момент.начала обработки запроса.Микропрограмма выполнения любойкоманды предполагает в последней ми: микрокоманце анализ запросов, и вслучае их,"наличия производится ветвление микропрограммы по коду зап" роса с выхода блока приоритета с переходом в начало микропрограммы обработки соответствующего запроса, приэтом следующая команда невыполняется, а ее адрес хранится в одном из регистров операционного блока 1Поокончании обработки запроса ввода(вывода) или группы запросов производится выполнение команды, которая былабы следующей в случае отсутствия запросов, или же производится передачауправления подпрограммы прерывания вслучае прерывания.формирование управляющих сигналовдля УВВ в соответствии с временнойдиаграммой, представленной на фиг. 6,осуществляет блок 16 выдачи управляющих сигналов в УВВ (фиг. 4), представляющий собой набор КВ-триггеров45-48 и элементов И 49-52. Каждый КВтриггер фиксирует налицие и окончание определенного режима обмена (обмен по приостанову ввода и командамввода - триггер 45, обмен по приостанову вывода и командам вывода триггер 46, наличие режима приостановатриггер 47, обмен по прерывания.триггер 48) по сигналам, поступающимс выхода дешифратора 9. Синхроимпульсы, поступающие на входы элементовИ 49-52, определяют момент выдачи управляющих сигналов с УВВ, характерных для того режима обмена, которыйопределен состоянием триггеров 45-48(входы элементов И 49-52), Временныедиаграммы (фиг. 6) представлены напримере 12-разрядного кольцевого регистра 42 сдвига .При обмене с УВВ по требованиямввода (вывода) процессор выдает вУВВ сигнал с управляющего выхода 25 процессора 23, инициирующий выдацу впроцессор адреса ячейки, который через вход мультиплексора 30 принимается на входной регистр 11 связи с УВВ(сигналзапроса адреса 3 А 1) и через ЗО операционный блок 1, выполняющий функцию передачи принимается на выходной регистр связи с УВВ. Далее алгоритм аналогичен алгоритму выполнениякоманд ввода (вывода),Обмен с прерыванием программы предполагает выдачу в УВВ управляющих сигналов, по количестве равных числувидов прерываний, инициирующих выдачув процессор кода прерывания (сигналов 40 запроса кода прерывания - ЗКП), который через вход мультиплексора 30 принимается на входной регистр 11 связис УВВ и через операционный блок 1,. выполняющий функцию перецаци, принима ется на регистр 10 связи с блокамипамяти (ЗУ) для записи его в качествестарого слова состояния программы. Выборка новых слов состояния программыпроизводится из ячеек памяти аналогично чтению информации из ячеек памяти.Аппаратный контроль передачи информации между УВВ и процессором осуществляется путем проверки на цетностькодов по контрольному разряду.Для осуществления программногоконтроля аппаратуры связи с внешнимиустройствами в состав системы командвведены две команды контроля: "Установка триггера контроля" и "Сбростриггера контроля". По команде установки сигналом с выхода дешифратора 9 производится установка триггера 31 контроля в "1" а также установка в15 "1" всех триггеров группы 13 триггеров запоминания требований приостанова ввода-вывода и группы 1 ч триггеров запоминания требований прерываний.Сигнал с выхода триггера 31 контроля поступает на вход элемента И 26 и разрешает прохождение каждого управляющего сигнала, из блока 16 выдачи управляющих сигналов в УВВ через элемент ИЛИ 28, выдаваемого в УВВ, через элемент ИЛИ 29 на счетный вход счетчика 8, Установка счетчика 8 в исходное состояние (осуществляется в каждой команде через вход элемента И 27), запрещается сигналом с инверсного выхода триггера 31 контроля, поступающим на вход элемента И 27. Таким образом, производится подсчет управляющих сигналов, выдаваемых процессором в УВВ за время прохождения прог раммы контроля. Сигнал с выхода триггера 31 контроля осуществляет переключение мультиплексора 30 таким образом, что информация, выдаваемаяв УВВ с выхода процессора 20, посту пает на его вход (вход мультиплексора 30) и запоминается в одном иэ регистров операционного блока 1 с целью программного контроля передаваемой в УВВ информации. Кроме того, сиг-З 5 нал с выхода триггера 31 контроля поступает на вход мультиплексора 4 для организации ветвления в микропро" грамме обработки прерывания. Ветвление организовано с целью запрета переда чи управления подпрограмме обработки прерывания и осуществления передачи управления в определенную точку программы контроля . В процессе выполнения программы контроля производится 45 последовательная обработка требований, хранящихся на триггерах 13, 14, в порядке убывания приоритета, до тех пор, пока не будут обработаны все требования, производится сравне" ние передаваемой информации с эталон" ной, а также подсчет управляющих сигналов, выдаваемых в УВВ, и запись содержимого счетчика 8 в ячейку памяти с последующим сравнением с эталонной суммой. По окончании программы конт" роля по команде сброса триггера контроля схема переводится в исходное состояние, В этом случае на счетный вход счетчика 8 сигналы поступают только с выхода дешифратора 9 через вход элемента ИЛИ 28, а установка производится сигналом с выхода дешифратора 9 через вход элемента И 27.Формула изобретенияНи кропрог раммный процессор, содержащий операционный блок, блок памяти микропрограмм, регистр микрокоманд, первый, второй и третий мультиплексоры, блок синхронизации, счетчик, дешифратор операций, регистр связи с запоминающими устройствами, входной и выходной регистры связи с устройствами ввода-вывода, группу триггеров запоминания требований приостанова ввода-вывода, группу триггеров запоминания требований прерывания, блок приоритета, блок выдачи управляющих сигналов в устройства ввода-вывода и первую группу элементов ИЛИ, выходы кото" рых соединены с адресными входами блока памяти микропрограмм, выходы которого соединены с информационными входами регистра микрокоманд, выходы полей операции, управления запоминающими устройствами, адреса перехода, выбора источников ветвления адресов, управления работои мультиплексора, управления дешифратором операций которого подключены соответственно к первому информационному входу операционного блока, выходу управления запоминающими устройствами процессора, первымвходам элементов.ИЛИ первой группы, управляющему входу первого мультиплексора, управляющему входу второго мультиплексора, входу дешифратора операций, первый, второй, третий, четвертый, пятый, шестой и седьмой выходы которого соединены соответственно с входами установки в "0" триггеров запоминания требования приостанова ввода-вывода. группы, входами установки в "0" триггеров запоминания требований прерывания группы, синхровходом входного регистра связи с устройствами ввода-вывода, синхровходом выходного регистра связи с устройствами ввода- вывода, информационным входом блока выдачи управляющих сигналов в устрой; ства ввода-вывода, управляющим входом третьего мультиплексора, синхровходов регистра связи с запоминающими устройствами, выход которого подключен к информационному входу счетчика, к вто"рому информационному входу операционного блока, к первым информационным входам первого и третьего мультиплексоров, выход операционного блока соединен с выходом адресации запоминающих устройств процессора, первым информационным входом второго мультиплексора, информационным входом выходного регистра связи с устройствамиввода-вывода, выход которого соедич ; неч с выходом информации в устроиства ввода - вывода процессора, выход счетчика подключен к вторым информационным входам первого и третьего мультиплексоров, выходы которых соединены соответственно с вторыми входами элементов ИЛИ первой группы и выходоминформации в запоминающие устройствапроцессора, выходы триггеров запоми- рц : нания требований приостанова ввода-вы, вода группы и выходы триггеров запо,минания требований прерывания группысоединены соответственно с первым и вторым входами блока приоритета, выход которого подключен к третьему информационному входу первого мультиплексора, а третий вход соединен с первым выходом блока синхронизации, второй выход которого подключен к входу ЗО 1 разрешения блока выдачи управляющих ; сигналов в устроиства ввода-вывода, атретий выход соединен с. синхровходом регистра микрокоманд и с синхровхо, домоперационного блока третий инфор-З 5мационный вход которого подключен квыходу входного регистра связи с уст-. ройствами ввода-вь 1 вода, второи инфори мационный вход второго мультиплексорасоединен с первым информационным вхо О дом процессора, выход второго мультиплексора подключен к информационному входу регистра связи с запоминающими устройствами, выход бпока выдачи управляющих сигналов в устройства ввода-вьаода соедйнен с выходом управления, устройствами ввода-вывода процессора, о т л и ч а ю щ,и й с я тем, что, с целью повышения полноты контроля, он содержит вторую и третьюгруппы элементов ИЛИ,первый и второйэлементы И, первый и второй элементыИЛИ, четвертый мультиплексор и триггер контроля, причем восьмой, девятый,десятый выходы дешифратора операцийсоединены соответственно с первымвходом первого элемента И, первым входом первого элемента ИЛИ, входом уста"новки в "0" триггера контроля, один"надцатый выход дешифратора операцийсоединен с входом установки в "1",триггера контроля и с первыми входамиэлементов ИЛИ второй и третьей грущу,выходы которых подключены соответст"венно к входам установки в "1" триггеров запоминания требований приостанова ввода-вывода группы и входам установки в "1" триггеров запоминаниятребований прерывания группы, а вторые входы соединены соответственно свходом запроса приоста нова и входомзапроса прерывания процессора, второйинформационный вход процессора соединен с первым информационным входомчетвертого мультиплексора, выход которого подключен к информационномувходу входного регистра связи с устройствами ввода-вывода, второй информационный вход четвертого мультиплексора соединен с выходом выходного регистра связи с устройствами ввода-вывода, управляющий вход четвертого ,мультиплексора, четвертый информационный вход первого мультиплексора,первый вход второго элемента И подключены к прямому выходу триггера контроля, инверсный выход которого соединен с .вторым входом первого элементаИ, выходом соединенного с входом приема информации счетчика, счетный входкоторого соединен с выходом первогоэлемента ИЛИ, вторым входом соединенного с выходом второго элемента И,выход выдачи управляющих сигналов вустройства ввода-вывода соединен свходами второго элемента ИЛИ, выходкоторого подключен к второму входувторого элемента И..1 са . юрюющФФй Воин дийЬ Ф 4 ж Ф вв ууи(РОрОэдм д йрцзив Уюй Ядри Р УИЖюфщРЙщцф д ффЬвив Вйа у - 1йввйии вувввв и ууу= д -йивииии виувуи уЮ84 ж а И 8ЭФЮюиив у ууу -вуИивии уувуи ГОрава ЖЙ Ю ОдФюс и уиививуивиив а уиуГ ааа ув еЗюрае дэйввувииувииу Ф уууФд рыйвиюи У ЯриааптМай ставитель Д. Ванюхред А,Кравчук ин Корректор С, Ыевкун Реда кто еселовская Заказ МВНИИПИ Г Тираж 568 митета по изобрет сква, 3-35, Раушс Подписниям и открытияя наб., д. 4/5 КНТ СССР дарственного 113035, Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 1

СмотретьЗаявка

4342851, 14.12.1987

ПРЕДПРИЯТИЕ ПЯ Ю-9578

ДРЕЛЬ ЛЕОНИД ИСААКОВИЧ, МУГИНШТЕЙН ИЗРАИЛ СЕМЕНОВИЧ, ШВАРЦ ЭММАНУИЛ ЕХЕЗКЕЛЕВИЧ

МПК / Метки

МПК: G06F 11/26, G06F 15/00

Метки: микропрограммный, процессор

Опубликовано: 30.03.1990

Код ссылки

<a href="https://patents.su/8-1553984-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Устройство постоянной памяти

Следующий патент: Коррелятор

Случайный патент: Линейный асинхронный двигатель