Процессор цифровой вычислительной системы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

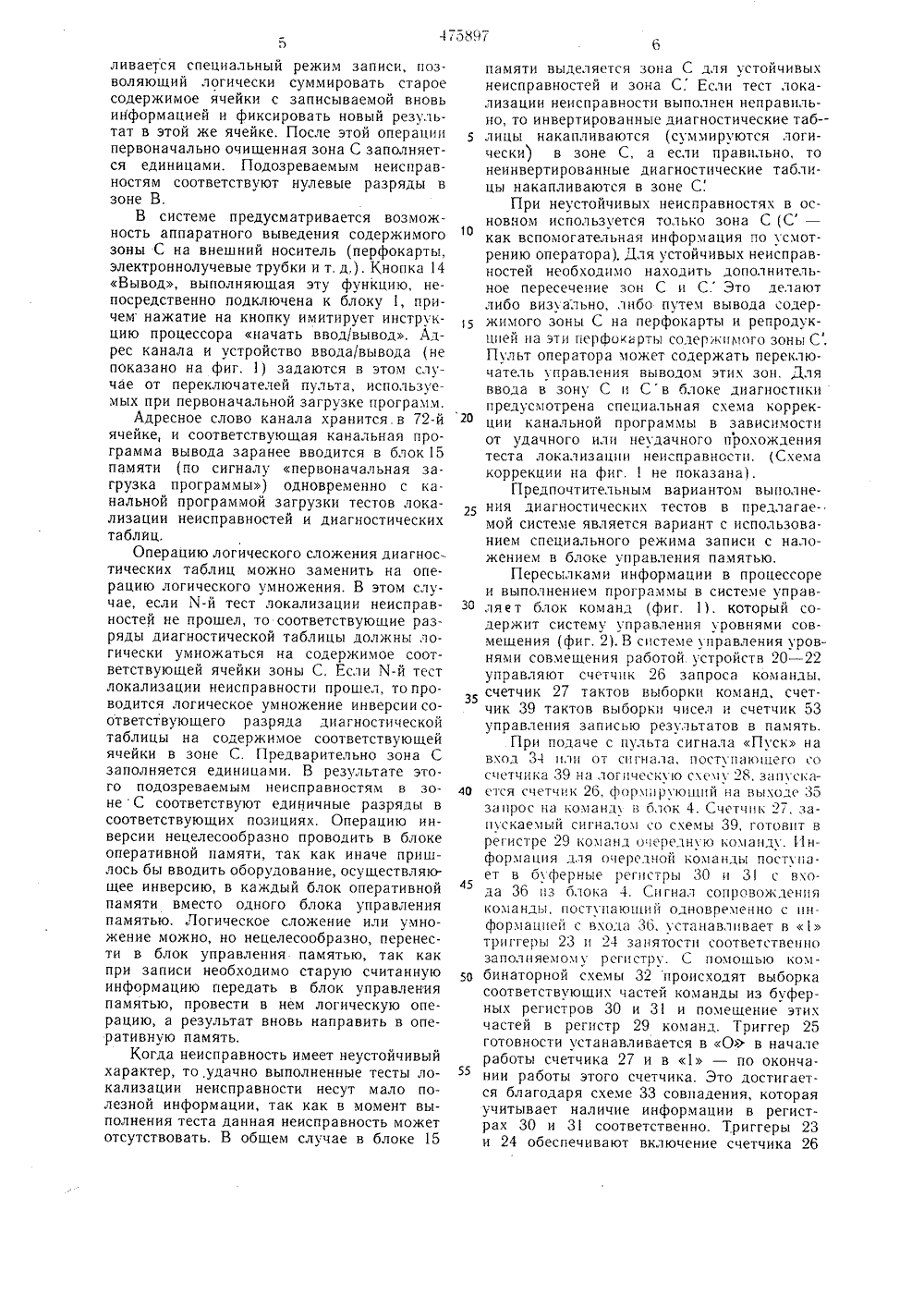

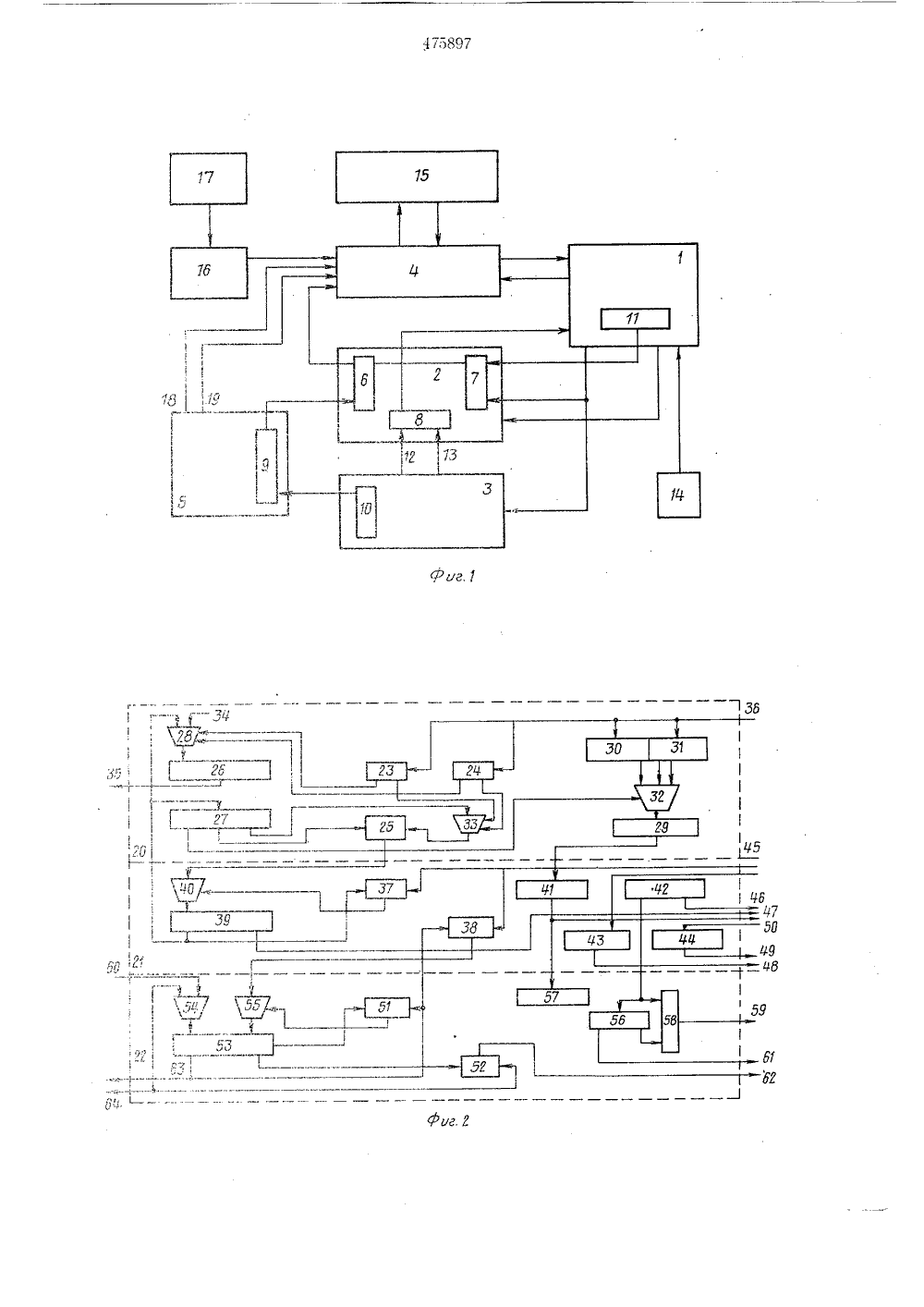

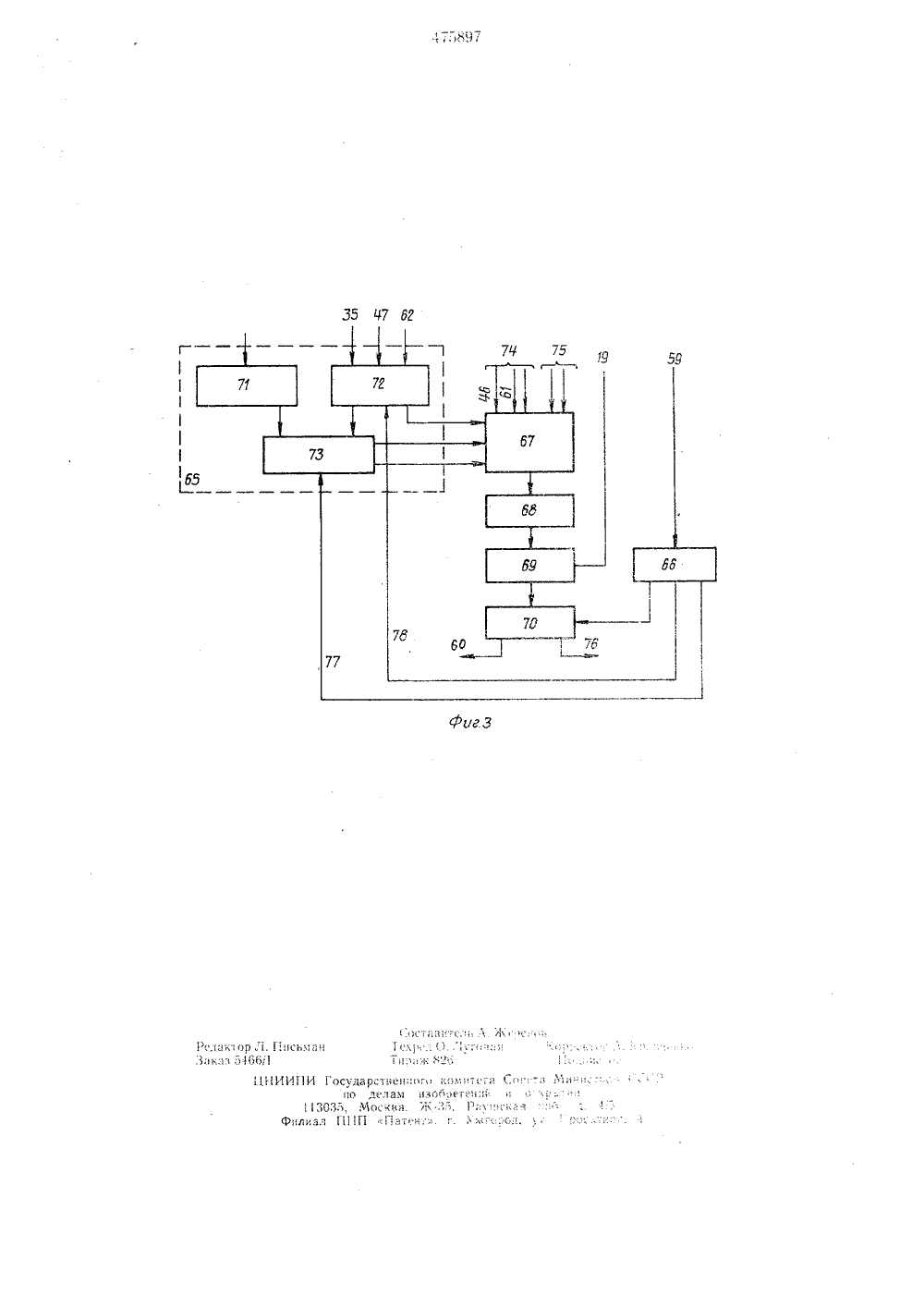

Союз СоветскихСоциапистимескихРеспубпик ОП ИСАНИЕ ИЗОБРЕТЕНИЯ(11) 475897 ) ТОР СКОМУ СВИДЕТЕЛЬСТВУ свид-в 61) Дополнительное к авт, 22) Заявлено 14,06,71 (21) 51) М. К 1668568/1( 06 Р 15/00 6 06 Г 11/00 присоединением заявки М Государственный комите Совета Министров ССС по делам изобретений н открытий) Дата опубликования сания к,6.0 К, Левин, В. С, АнтоноБ. Михайлов, О, Д. Жуебарт, И. С, Храмцов, Иапилина, Ю. А. Коханов,Б. А. Пряхин и В, В(54) ПРОЦЕСС ЦИфРОВОИ ВЫЧИСТЕМЫ Изобретение относится к цифровой вычислительной технике, в частности к структурам центральных процессоров вычислительной системы, содержащей набор квази- независимых блоков, работаюиих с совмещением во времени, включая встроенный 5 блок диагностики.Известны процессоры цифровых вычислительных систем, содержащие квазинезависимые блоки, такие как блок команд, блок управления памятью, подключенный к блоку памяти и включающий в себя входные и выходные регистры, пульт управления.Однако такие процессоры вычислительных систем имеют недостаточно высокое быстродействие, их диагностическая аппаратура сложна, что вызвано ее автономностью и универсальностью, и, кроме того, в них не используется оборудование местных блоков управления, имеющихся в различных подсистемах системы, для диагностики процессора.Разделение функций контроля и диагностики процессора между отдельными подсистемами путем использования оборудования местных блоков управления этих под систем является существенно новым и принципиально отличает данный процессор от известных.Цель изобретения - сокращение оборудования и повышение быстродействия процессора.Это достигается тем, что в процессоре выход наложения и выход инверсии блока диагностики соединены с третьим и четвертым входами блока управления памятью, информационный выход блока диагностики подключен к четвертому входу двоичного арифметического устройства, а пятый и шестой входы двоичного арифметического устройства - соответственно к выходу прерываний и выходу кода условий десятичного арифметического устройства, выход результата которого соединен с входом блока диагностики. Второй выход двоичного арифметического устройства подключен к первому входу блока команд, второй вход которого связан с вторым входом процессора.На фиг. 1 представлена блок-схема процессора цифровой вычислительной системы; на фиг. 2 приведен пример построения подсистемы управления уровнями совмещенияблока команд; на фиг. 3 - пример построения блока управления памятью процессора.Предлагаемый процессор содержитблОк 1 команд, двоичное арифметическоеустройство 2, десятичное арифметическоеустройство 3, блок 4 управления оперативной памятью и блок 5 диагностики. Двоичное арифметическое устройство 2 имеет входной - выходной регистр 6, коммутатор 7и триггеры 8. Входной - , выходной регистр 6соединен с регистром 9 информации и фотографирования блока 5 диагностики, а этотрегистр - с регистром 10 результата десятичного арифметического устройства 3.Блок 1 команд содержит управляющие триггеры 11, соединенные с коммутатором 7 двоичного арифметического устройства 2. Десятичное арифметическое устройство 3 связано с двоичным арифметическим устройством 2 шинами прерываний и кода условий,подсоединенными соответственно к выходам 12 и 13 устройства 3.К блоку 1 подключена кнопка 14 Вывод. Блок 4 соединен с блоком 15 памяти,а та кже через канал 16 - - с накопителем 17 на магнитной ленте, Выходы наложения 18 и инверсии 19 подключают блок 5диагностики к блоку 4 управления памятью.В состав схемы, представленной на фиг. 2входит подсистема управления уровнями совмещения блока команд, которая состоит изтрех частеи: устройства 20 выборки команд,устройства 21 выборки чисел и устройства 22отсылки результата.Устройство 20 выборки команд содержит триггеры 23, 24 занятости, триггер 25готовности, счетчик 26 запроса команды,счетчик 27 тактов выборки команд, логическую схему 28, регистр 29 команд, буферныерегистры 30, 31, комбинаторную схему 32и схему 33 совпадения. Вход 34 связан спультом, а выход 35 и вход 36 - с блоком 4 управления памятью,В устройство 21 выборки чисел введенытриггер 37 занятости, триггер 38 готовности, счетчик 39 тактов выборки чисел, комбинаторная схема 40, регистр 41 команд, регистр 42 адреса числа, регистр 43 первогочисла .и регистр 44 второго числа. Вход 45и выходы 46, 47 соединены с блоком 4, авыходы 48, 49, 50 - с блоками 2 и 3.Устройство 22 отсылки результата состоит из триггера 51 занятости, триггера 52запроса записи, счетчика 53 управления записью результатов в блок 15 памяти, логических схем 54, 55, регистров 56, 57 и схемы 58 сравнения адресов. Выход 59, вход 60и выходы 61 и 62 связаны с блоком 4, авыход 63 и вход 64 - с блоком 2.Блок 4 управления памятью содержитузел 65 приоритета, схему 66 разрешенияконфликтов, входные логические схемы 67,входные регистры 68, схему 69 инверсиии выходные регистры 70. В состав узла 65входят схема 71 приоритета каналов, схе ма 72 приоритета процессора и схема 73 приоритета обобщенных запросов. Вход 74 соединен с процессором, входы 75 - с каналами, а выход 76 - с блоком 15 памяти, Схема 66 связана со схемой 73 шиной 77 и со схемой 72 - шиной 78,Блок 1 команд процессора цифровой вычислительной системы выполняет функции центрального управления работой системы, в которой используется совмещение во времени работы отдельных подсистем, т. е. отдельные блоки системы, такие как 5 1 Облок команд, двоичное арифметическое устройство 2, десятичное арифметическое уст 50 ной к выходу 18. Блок 14 управления памятью, в свою очередь, передает его в блок 15 памяти по адресу, полученному блоком 4 от канала 16. Когда требуется инверсия диагностической таблицы, блок 5 формирует на выходе 19 сигнал инверсия, который заставляет блок 4 инвертировать информацию, передаваемую каналом 16 перед ее наложением, в зоне С. В блоке 15 памяти устанавройство 3 и блок 4 управления памятью, работают квазинезависимо и параллельно во времени. Так как к современным вычислительным системам предъявляется требование работы с высокой степенью надежности, а также требование сокращения времени простоя при выполнении ремонта, то в систему введены блок 5 диагностики и специальный режим работы тесты локализации неисправностей в котором использованы специальные диагностические таблицы. Тестовые данные размещены на магнитной лен те в накопителе 17.Тестовые данные, например тест И, находятся до диагностической таблицы, относящейся к (М - 1)-му тесту, за которой следует (И+1) -й тест и Я-я диагностическая таблица, размещаемая за ним. Диагностическая таблица представляет собой совокупность двоичных разрядов. В ней каждой единице соответствует какое-либо оборудование системы, неисправности которого способны влиять на выполнение тестов лока-, з 5 лизации неисправностей, В фиксированныхобластях блока 15 памяти выделены три зоны: А, В - для последовательного ввода тестов локализации неисправности,и зона С- для накопления диагностических таблиц.Если тест локализации неисправности про Ошел удачно, необходимо осуществить логическое сложение (г=х:У ), где х - элементы зоны С, а р - соответствующие элементы диагностической таблицы. Диагностическая таблица инвертируется и ло гически складывается с зоной С (в случае,если тест локализации неисправности прошел удачно). Для этого в момент ввода Х-й диагностической таблицы в блок 15 памяти блок 5 диагностики выдает в блок 4 сигнал наложение по шине, подключен 475897ливается специальный режим записи, позволяющий логически суммировать старое содержимое ячейки с записываемой вновь информацией и фиксировать новый результат в этой же ячейке. После этой операции первоначально очищенная зона С заполняется единицами. Подозреваемым неисправностям соответствуют нулевые разряды в зоне В.В системе предусматривается возможность аппаратного выведения содержимого зоны С на внешний носитель (перфокарты, электроннолучевые трубки и т. д.). Кнопка 14 Вывод, выполняющая эту функцию, непосредственно подключена к блоку 1, причем нажатие на кнопку имитирует инструкцию процессора начать ввод/вывод. Адрес канала и устройство ввода/вывода (не показано на фиг. 1) задаются в этом случае от переключателей пульта, используемых при первоначальной загрузке программ.Адресное слово канала хранится.в 72-й ячейке, и соответствующая канальная программа вывода заранее вводится в блок 15 памяти (по сигналу первоначальная загрузка программы) одновременно с канальной программой загрузки тестов локализации неисправностей и диагностических таблиц.Операцию логического сложения диагностических таблиц можно заменить на операцию логического умножения. В этом случае, если М-й тест локализации неисправностей не прошел, то соответствующие разряды диагностической таблицы должны логически умножаться на содержимое соответствующей ячейки зоны С. Если Х-й тест локализации неисправности прошел, то проводится логическое умножение инверсии соответствующего разряда диагностической таблицы на содержимое соответствующей ячейки в зоне С. Предварительно зона С заполняется единицами. В результате этого подозреваемым неисправностям в зонеС соответствуют единичные разряды в соответствующих позициях. Операцию инверсии нецелесообразно проводить в блоке оперативной памяти, так как иначе пришлось бы вводить оборудование, осуществляющее инверсию, в каждый блок оперативной памяти вместо одного блока управления памятью, Логическое сложение или умножение можно, но нецелесообразно, перенести в блок управления памятью, так как при записи необходимо старую считанную информацию передать в блок управления памятью, провести в нем логическую операцию, а результат вновь направить в оперативную память.Когда неисправность имеет неустойчивый характер, то,удачно выполненные тесты локализации неисправности несут мало полезной информации, так как в момент выполнения теста данная неисправность может отсутствовать. В общем случае в блоке 15 памяти выделяется зона С для устойчивых неисправностей и зона С; Если тест локализации неисправности выполнен неправильно, то инвертированные диагностические таб лицы накапливаются (суммируются логически) в зоне С, а если правильно, то неинвертированные диагностические таблицы накапливаются в зоне С,При неустойчивых неисправностях в основном используется только зона С (С - 10как вспомогательная информация по усмотрению оператора), Для устойчивых неисправностей необходимо находить лополнительное пересечение зон С и С. Это делают либо визуально, либо путем вывода содер жимого зоны С на перфокарты и репродукцией на эти перфокарты солержимого зоны С, Пульт оператора чожет содержать переключатель управления выводом этих зон. Для ввода в зону С и Св блоке диагностики предусмотрена специальная схема коррекции канальной программы в зависимости от удачного или неудачного прохожления теста локализации неисправности. (Схема коррекции на фиг. 1 не показана).Предпочтительным вариантом вьшолне ния диагностических тестов в предлагаемой системе является вариант с использованием специального режима записи с наложением в блоке управления памятью.Пересылками информации в процессореи выполнением программы в системе управзо ляет блок команд (фиг. 1). который содержит систему управления уровнями совмещения (фиг. 2). В системе управления уровнями совмещения работой устройств 20 - 22 управляют счетчик 26 запроса команды, счетчик 27 тактов выборки команд, счетчик 39 тактов выборки чисел и счетчик 53 управления записью результатов в память.При полаче с пульта сигнала Пуск навхол 34 или от сигнала, поступающего со счетчика 39 на логическую скочу 28, здпускд ется счетчик 26, форчируюшпй на выхолс 35запрос нд команл в блок 4. Счетчик 27, запускаемый сигналом со схемы 39, готовит в регистре 29 команд о 1 ерелную комднлу. 11 нформация лля очерелной команды поступает в буферные регистры 30 и 31 с входа 36 нз олока 4. Сигнал сопровожления команды, поступающий олновременно с информацией с вхолд 36, устанавливает втриггеры 23 и 24 занятости соответственно заполняемому регистру. С помощью ком бинаторной схемы 32 происходят выборкасоответствующих частей команды из буферных регистров 30 и 31 и помещение этих частей в регистр 29 команд. Триггер 25 готовности устанавливается в 0 в начале работы счетчика 27 и в 1 - по окончании работы этого счетчика. Это достигается благодаря схеме 33 совпадения, которая учитывает наличие информации в регистрах 30 и 31 соответственно. Триггеры 23 и 24 обеспечивают включение счетчика 265 1 О 5 20 35 40 45 50 55 запроса команды в тех случаях, когда информация из регистра 31 полностью передана в регистр 29 команд.Следующий уровень совмешения запускается при наличии в триггере 25 единицы, что указывает на готовность устройства 20 выборки команд, и нуля В триггере 37 занятости. что указывает на незанятость устройства 21 выборки чисел. При этом начиняет работать счетчик 39, запускаемый через комбинаторную схему 40, в результате чего принимается очередная команда в репстр. 41 и формируется адрес числа в регистре 42. Адрес числа с выхода 46 и запрос числя с Выхода 47 передаются В блок 4. Числа, подлежащие обработке, формируются в регистре 43 первого числа и в регистре 44 второго числя, поступая в эти регистры из блскя памяти.Г 1)иГГе),7 хстссвливсяетс 5 в 1 В момент начала с;етя В счетчике 39.и сбрасывается В О сигялсм сопвовождения, пост( :яксцВхслх 4 . 1 ) Гер л Гото. Ос Г хтяняВливяетс 5 В 1 сиГня:с)ы, поступяюцим по входу 45, сбрасывается в О Вачялс работы седуюшего уровня сигналом, иоступак)шим по Выходу 63. Уровень отсылки результата начинает работать при условии, что триггер 38 няхолится в 1 и при наличии О В триггере 51 занятости урозня, что Обеспечивается логической схемей 55. Этот уровень принимает адрес отсь ки рс:ульта Гс и репстр бо из рсгстра 42 и кохснд В регистр 57 из регистр 11.Г 1 с )ВНОГС Нерво о тятя ссетссикя )3 фс есн сГял нячяля Операции ня Выходе 63 и Ос) шсствляется передача чисел по выходам 48, 49 и команды по Выходу 50 в олоке 2 и 3.Дсльнейця 5 раоотя хстройствя 22 нячиняетс с четвертогс такта счетчика 53 либо по с.ипялу конец работь арифметического устройства, поступающему по Входх 64 В том слхчае, когда нет записи В память, либо и сипгалу результат запися, проходяцсехх по Входу 60 из блока 4, если имела место запись в память, что обесечивается логической схемой 54 на входе четвертого разряда счетчика 53. Запрос на запись В блок 4 дяегся с выхода 62 от триггера 52 запроса записи, я адрес зяНгси - с выхода 61 в блсн( 4.Триггер 5 зя 5 Г сс Ги устанавливается в 1 при начале счета в счетчике 53 и сбрасывассся в конце рабогы этого счетчика.ДЛЯ РсЗРЕсЕЯ КОфЛИКТНЫХ СсТУсЦИЙ, Возникающих при совпадении адреса отсылки результата с адресом числя, для регистров 42. 56 предусмотрена схеха 58 сравнеия адресов. При совпадении адресов в этих реггсрсх схема 58 Вырябягывсет сиГ- нял отмены запрося числя, поступаюций В ОлОк 4 с ыхода О 9. КОфликтные ст ЯЦИИС С ЕРВсОтея О;СЯНОЙ, О ДЛЛ анализа и разрешения других конфликтных ситуаций не требуется отмена запроса.Команда Вывод с пульта (от кнопки) реализуется путем засылки в регистр 56 информации с пульта и принудительного исполнения инструкции вывода информации из канала.Блок команд обращается в блок 15 памяти для Чтения команд и операндов и записи результатов выполнения операции, Так как запросы на обращение в память могут возникнуть в различных блоках одновременно, то их обработку необходимо осуществлять в приоритетном порядке. Запросы от каналов 16 подаются на схему 71 приоритета каналов, а запросы от блока 1 - на схему 72 приоритета процессора. Управление узлом 65 осуществляется сигналами сброса по шине 77 и сигналами блокировки по шл 5 се 78, поступающими со схемы 66 разрешения конфликтов на схему 73 приоритета обобщенных запросов и схему 72 приоритета процессора соответственно. Выходные сигналы узла 65 управляют работой входных логических схем 67, на которые проходят входные данные от процессора по входу 74 и входные данные от каналов по входам 75.Узел 65 разносит по времени выполнение этих запросов в блоке 4. На входные регистры блока 4 принимаются входные данные от того абонента процессора, который в данный момент получил, приоритет. Схема 66 разрешения конфликтов выделяет код номера устройства блока памяти, к которому в данный момент проводится обращение, и анализирует состояние этого устройства. Г 1 ри занятости устройства блока памяти его номер запоминается в схеме 66, а в узел 65 посылаются сигналы сброса схемы 73 и блокировки схемы 72, которые вызывают начало просмотра запросов каналов. Как только устройство блока памяти, в которое обращался данный блок процессора, освобождается, схема 66 посылает в узел 65 сигнал, который в случае отсутствия запросов от каналов вновь устанавливает приоритет процессора, Если данный абонент процессора обращается в свободное устройство блока памяти, то это устройство запускается, и в соответствующий абонент процессора посылается сигнал Ответ. По этому сигналу абонент процессора формирует следующий запрос в блок памяти.При обнаружении конфликта между обращениями от различных блоков процессора вырабатываются сигналы отмены запросав блок памяти, который поступает на схему 66 разрешения конфликтов блока 4, В случае наличия этого сигнала сбрасывается соответствующий запрос в узле 65 и если этотзапрос уже начал обрабатываться, его обработка прекращается, а узел 65 приоритета переходит к просмотру следующих за просОВ. При этом сиГнал От)е сот 5)с.ствующему абоненту по входу 60 от вы.,о, - ного регистра 70 не выдается.Инверсия информации осущсствляс к в схеме 69, При подаче этой инверсии с вх(:.- ных регистров 68 блока 4 на его вьхо,1 ыс регистры 70 и наличии соотвстствуоц(сигнала на выходе 19 блока 5 д 1(с;:- ки. Информация, записанная во 13 х)лно .реги(.тре 68, инвсртируется схс;ой 69 и 1:. -5 г) реписывается в выходные регистры 70 свя. занные с блоком памяти по Вых,в, ).Выход 18 наложения тра(нзиом(;)(,одит через блок 4 управления пам 5 ть; н соответствуюгцие вентили, осуцестзляюп;,.:;управление регенерацией игформаци В бл;)- ке памяти. Эти Вентили на фиг. 8 не показаны.С Ц, ЬК) СОКР 1 Ц;ЕНИ 51 ИСГ 2 Г)Х 5. (3 блоке 4 входной-выходной регнсг,устройства 2 связан с регистрм 9. ;)Ослсдний, В свою очередь, -- с вьх( .-,:",ымс регистром 10 устройства 3. Зто позьоляс Вместо т 13 ех Входов по пнфОРма 31)и наГ 1) (от устройств 2 и 3 и блока 51 и,;сть один - от устройства 2. Послсло)атсь)1,.5.пересылка результата из ус Грайства 3 блока О лимтирОЯЗ)с пО Време 1 .)Сс 51 тичные оперзши и режим д 3 згпост),ь; слабо Влияют н 2 и Ооиз )дите;ьнос Гь :1)сте) 1, Кроме того, регистр 9 информацииф( г)афирования используется для оз)оса с;)стоянии О(.новньх реги)с ров п)0)цессп;.3ПЗГностике с послелу 10 ше)й записью В (1 ч)1:,.СИРОВ 2 ИН 0 ЗОН ПЗМЯ 51.Упрощение стр(ктуры б,Ока :,;:; Гигзет - ся помещение.; в устройство 2 ксра 7, управление кгорым осушес"Гв,я т.я -, от управляюних тоиггеров 11 блока 1 команд. Комм "татОр 7 ООГЗ)из)е Г псрсп Оь операндов так, чтобы упростить 5:ослелу ощую обработк и зпись резузьтзта в регистры общео назначения блока 1 1 П; . казаны на фи. 11. 1 Г)именение кол)13 2 Ор(1 4 В ГОЗВО)яЕТ ОВЫСТЬ бЫСТгродЕй(ГГ(И ЗЗ С)С СОВМЕЦЕ)НИ 5 1 РЬЕ)2 И ВЬСТЗЗЛС 1151 О 1")ЗИЛОВВ В Трсб)уему 0 ЗОг( ВХО,1 НОГО-ВЫХ(;Н.)- ГО реГистр 5 ) без пос.елуюп)его 5,Г)нл(с- НИЯ РЗСГ.)51)ИЯ ИНфОР)ЗЦИ .1 Э): Р( ГИС РЕ.,.)551 ТОГО. Ч ООЫ МаС.Х 2. ЬНО Х Ро(- ТИТЬ ОЛОК, ЗЫХО(ПРЕгзЫВЗН 1;й И ВЫХОЗ 3 КОЛЗ СГ)З.51 (Л,Я ОПС")ЗЦИЙ фРМЗ 12 С"," )5 Р,) )1505 1 С;),)Н,: (3 КОИ)2)Н,(С И ВЫ - .,:Л Л( ( 1 О,1. (; 1 З 2 351 ГИ, 2 ГЗКЖЕ ф рМЗТЗ. В Котр гМба ОПСрзпла рЗЗМС)(;,),г.) )1 В ол, к);0 Г(;)1,тп) ) строст 32 8 ерсис Грь 1: 3" 5 Г; с )ы 51 3 (тр)ств 31) " р)з;,(; )1,.111,ьн)й системе и(.- ПОЛ ЬЗОВЗНО 1 301)2.,: Е ВЫ" 1 С,011 С ТЕК - и,е Време . ) я) С(к л 11:(йм 51 ти хан:тся тек), цсс з 2 с).( . 1( )с)2, Кор 1)кТ 111)овк,.1 ЭГ 1 31 )н: я )цествг 5 ется с :)0(цьО с)с 1(к( Г)153)ср; (не) показан ;(2 Сртежах (; Иг)(:5:З ,З(13 ср, КОтОрцй В;г Зоа)13,С)ся б-.он( . 1 И НОСт ПаЕт В ,стр;иство , Глс н си:1.:,; 31)ср выи(:Пняте ин( 1)х к 1)1 .1 в 53 дни)е с пла- ВЗО,.,; г 5 гйПО;Сс.")" .3)1(.).".150( ВЬЦИС,1 ИТС,ЬПОЙ СИСТЕМ,.;(, СО 3 ЕРЭКЗ 11,)1. )15 Л 131 НОС ГИКИ. 0.ОК (лравлс:.)я па.,:я:, ., Гос;3 нс Иый с блоком ПЗ МЯТИ )1 01 С)КОМ 1,1)Л, (ЕРВЫ: ВЫХОЛ КОГОРОГО:30 ЛКГ 1 Ос:1:, (:Р)ьм Входах Лсся;ГО 3)1;(,)Т . )г (СРОИ(Т 33 . ЛВОООЙ и тпс 5( Зх.,ц(: )1)(0 сбединсны сол)егс-)Вцнн(3 с Г.тпс)ч)нм выхг)ЛамиЗ; г) (, (Г)1)( Й ВХО (Ь ОЛО; ь)одкл н)цены соот- )С ;,"С (15 :(."), В )ХО 33 )01.(.О) 2 11 сВ) 3 ьхол) Л 3( 1 ч го (3)И(3)м(ГНсско 0Т"СОг)" "" Т ц")ЦЗ 1)К)Е РЦ Е С 1 Ь; ) 01 Х,;, Н . 51 П О )5 Ь 130 Н 1 )О Ы С . тоодсиств 1, В н(3 м 53)х(з.), н 2.10 же(Н 51 1 Вы ХОЛ ИН 13 ЕРС 1 И ОЛКЗ Л:1 ОСТИ Е 1 СС)ЛИ НОНЫ СТВЕТСТВЕННО С ". (: )ПМ 11 СТ 3.",ЕТЫХ 3 ХО ;.с) )И О;10;) 2 М)(РЗГ),С.и ;М 51 г)Ю, ИНФОР)12.

СмотретьЗаявка

1668568, 14.06.1971

ПРЕДПРИЯТИЕ ПЯ М-5769

ЛЕВИН В. К, АНТОНОВ В. С, ШУЛЬГИН А. А, ЕГОРЫЧЕВА Н. В, ЖУКОВ-ЕМЕЛЬЯНОВ О. Л, КЛИМОВ В. В, КОРОЛЕВА Т. М, КОХАНОВ Ю. А, МИХАЙЛОВ И. Б, ПАПИЛИНА Г. С, ПЕБАРТ М. Д, ПОПОВА И. А, ПОЧЕЧУЕВ Ю. А, ПРЯХИН Б. А, ХРАМЦОВ И. С

МПК / Метки

МПК: G06F 15/00

Метки: вычислительной, процессор, системы, цифровой

Опубликовано: 05.10.1978

Код ссылки

<a href="https://patents.su/7-475897-processor-cifrovojj-vychislitelnojj-sistemy.html" target="_blank" rel="follow" title="База патентов СССР">Процессор цифровой вычислительной системы</a>

Предыдущий патент: Регулирующая сборка ядерного реактора

Следующий патент: Полупроводниковый переключающий прибор

Случайный патент: 345346