Аналоговый декодер расширенного кода голея

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

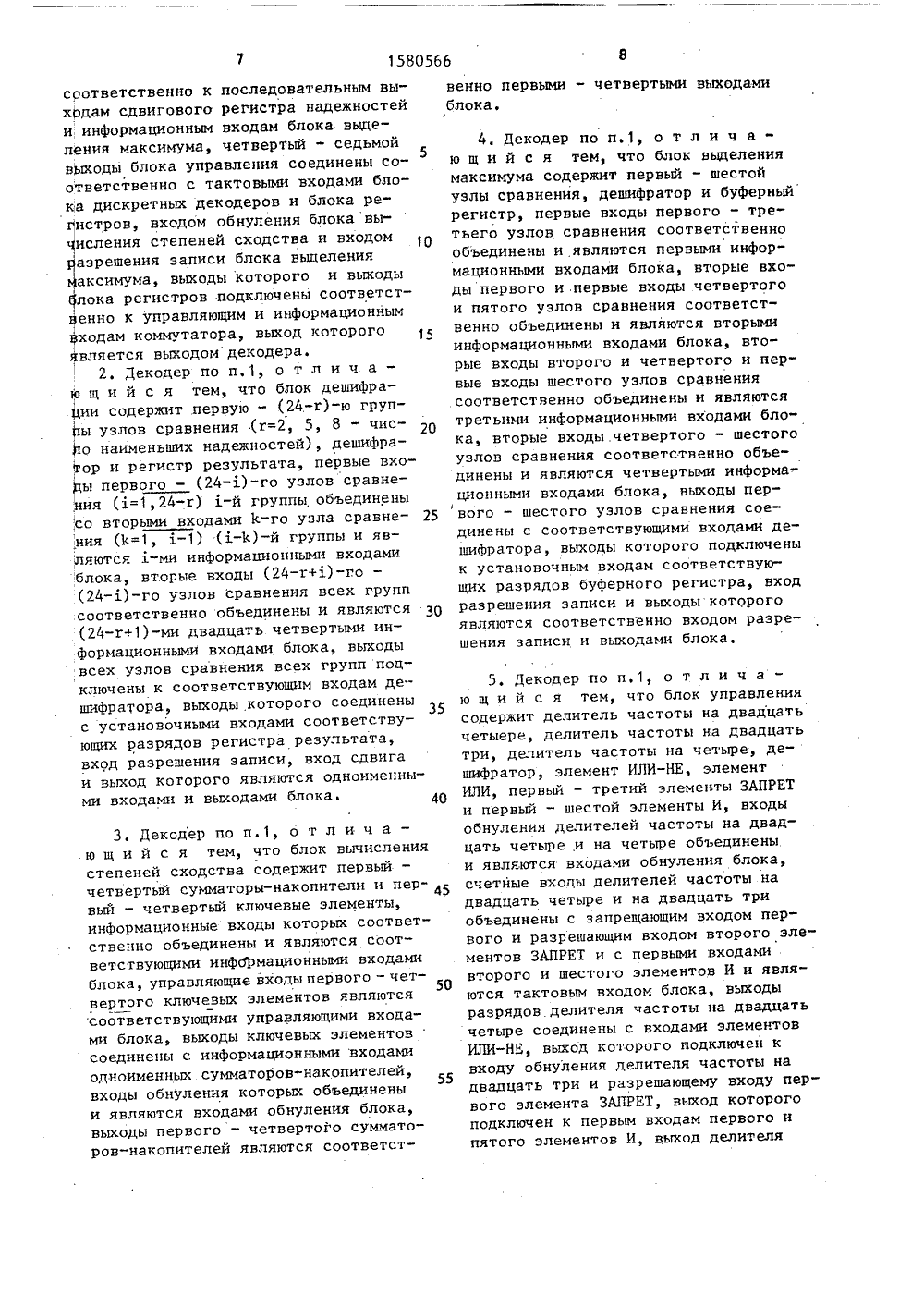

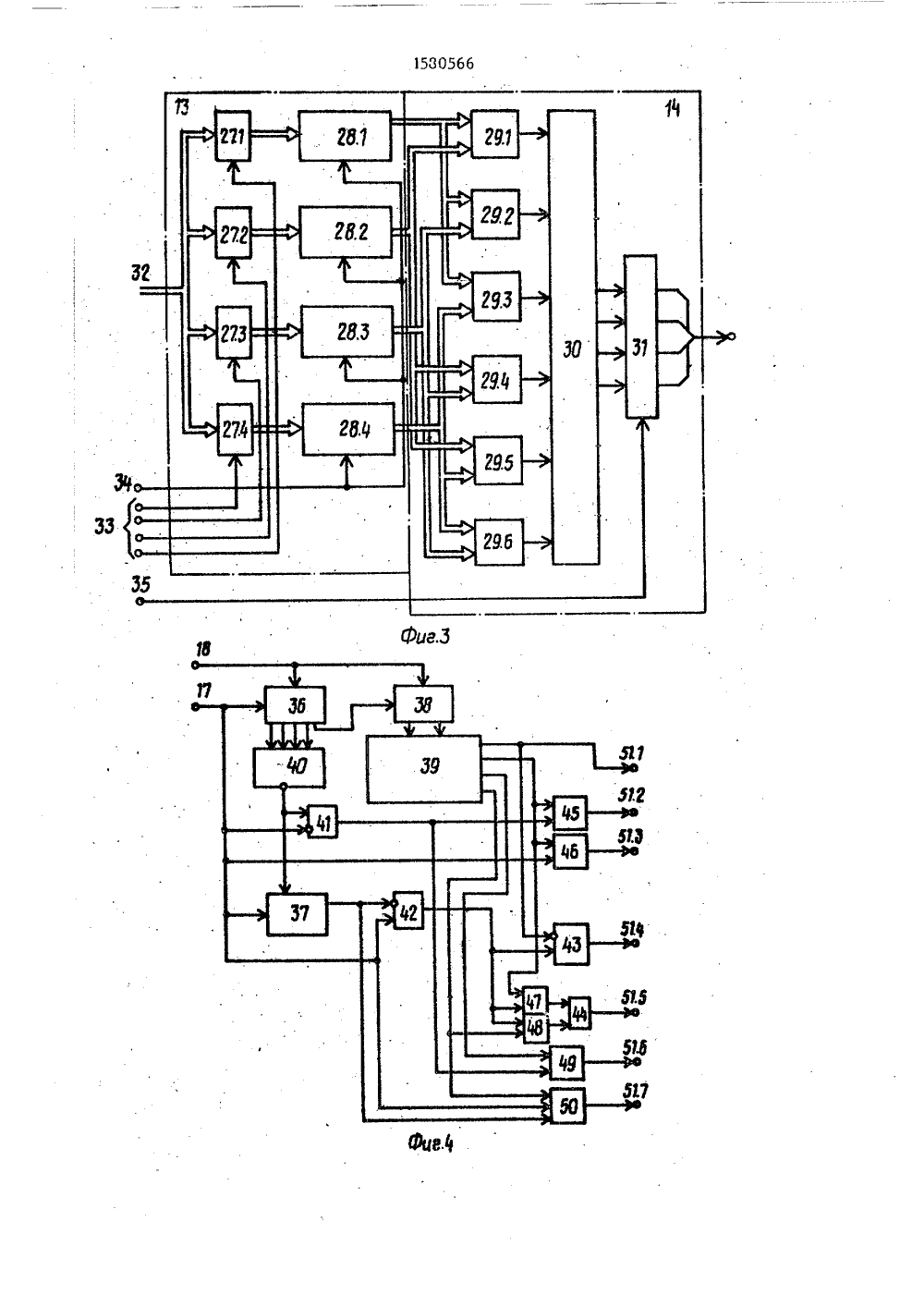

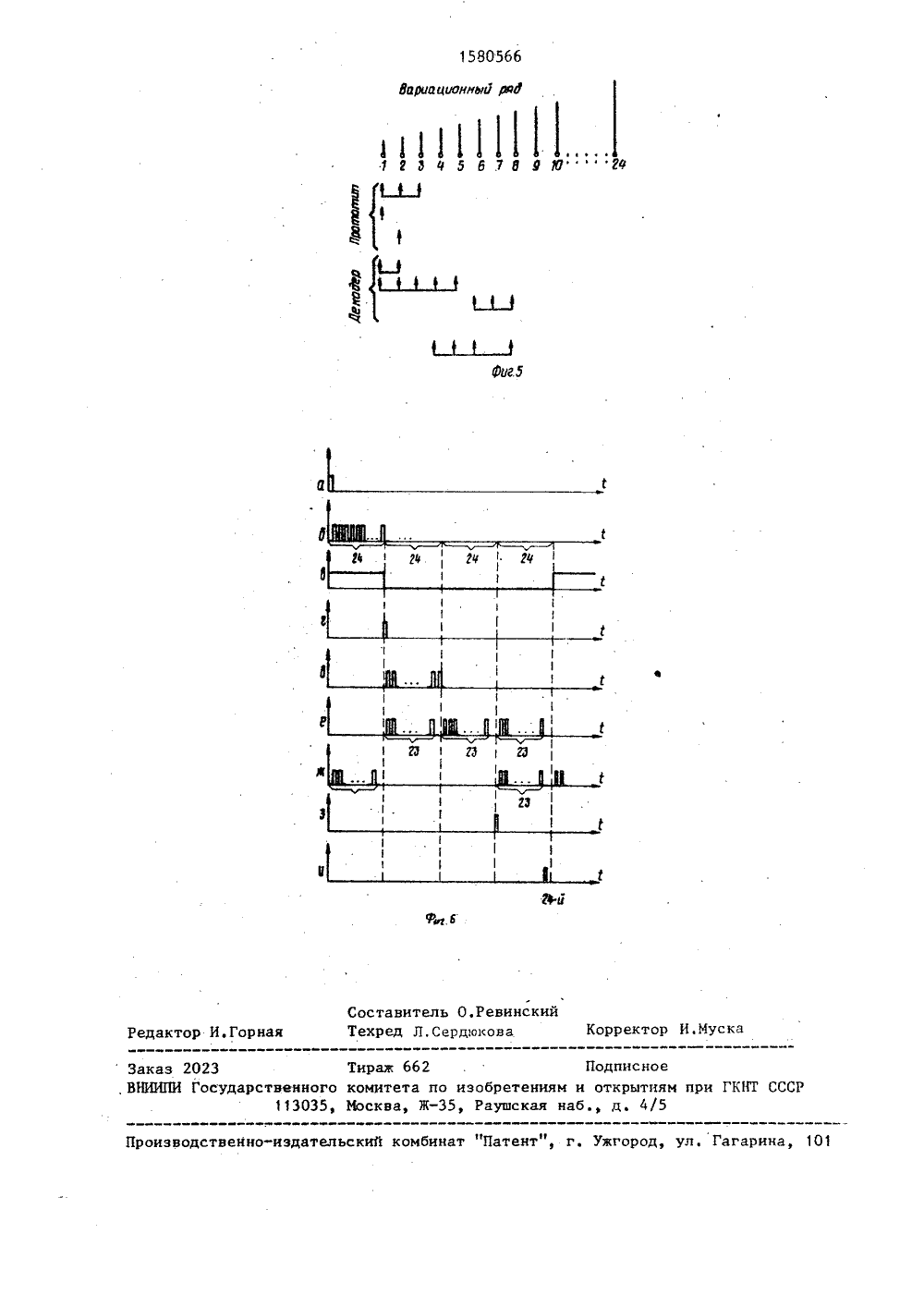

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 1 13/02 ГКНТ ССОПИСАНИЕ ИЗСБРЕТЕНИ АВТОРСКОМУ С ПЬСТВ 414087/245,04,883.07.90.енинградст связи юп. У 27ий электром. проф, М хническ.Бончург, А.А.Зах4 (088.8) асс 1 опз оп СоупУ 5, ч, СОМт,38,.Д, Мирончиков Е,Т; цик;.:;веских кодов.68, с.85-86.свидетельство СССРН 03 М 13/02, 198 ГОСУДАРСТВЕННЫЙ НОМИТЕПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЙПРИ(21) 4 С 22) 2 (46) 2 (71) Л институ Бруевича (72) В.В.Гинз и А,С,Наумов (53) 621.394, (56) 1 ЕЕЕ Тга сайопв. 1981 911.Радиотехни с,85-86.Колесник В Декодирование М.: Связь, 19Авторское В 1401614, кл НАЛОГОВЬП ДЕКОДЕР РАСИ 1 РЕННООЛЕЯ(57) Изобретение относится к вычислительной технике, Его использование в системах передачи дискретной информации позволяет повысить помехоустойчивость. Декодер содержит мультиплексоры 1,2, сдвиговые регистры 3,4 информации и надежностей, блок 5 управления, блок 6 дешиг,оа.:ии, блок 14 выделения максимума и коммутатор 16, Благодаря введению блоков 7,8 дешифрации, сумматоров 9-11 по модулю два, блока 12 дискретных декодеров, блока 13 вычисления степеней сходства иФ блока 15 регистров в декодере осуществляется исправление всех конфигураций ошибок среди символов с восемью наименьшими надежностями. 4 з.п. ф-лы, 6 ил,Изобретение относится к вычислительной технике и может быть использовано в системах передачи дискретной информации.5Цель изобретения - повышение помехоустойчивости.На фиг. 1 приведена блок-схема предлагаемого декодера; на фиг.2 - выполнение. блока дешифрации; на фиг.З - выполнение блока вычисления степеней сходства и блока выделения максимума, на фиг.4 - выполнение блока управления; на фиг,5 - принцип инвертирования символов принимаемого ко" да, на фиг.б - диаграммы управляющих сигналов.Декодер содержит первый 1 и второй 2 мультиплексоры, сдвиговые регистры информации 3 и надежности 4, блок 5 управления, первый - третий блоки 6 - 8 дешифрации, первый - третий сумматоры 9 - 11 по модулю два, блок 12 дискретных декодеров, блок 13 вычисления степеней сходства, блок 14 выделения максимума, блок 15 регистров и коммутатор 16. Декодер содержит также тактовый вход 17, вход 18 обнуления,. информационный вход 19 и вход 20 надежности.30Надежности символов расширенного кода Голея представлены в виде ш-раз. рядных двузначных чисел, поэтому сдвиговый регистр надежности имеет двадцать четыре ш-х разряда.35Блок 6 (7,8) дешифрации содержит (фиг.2) группы 21 узлов сравнения, дещифратор 22 и регистр 23 результата. На фиг.2 обозначены информационные входы 24, вход 25 разрешения записи и вход 26 сдвига. В каждой группе 21 осуществляется сравнение соответствующей надежности со всеми последующими вплоть до (24-г)-й,. гдег - число наименьших из двадцати четырех надежностей, Для блока 6 =2, для блока 7 г=5, для блока 8 г=8.Дешифратор 22 содержит двадцать четыре пары сумматор - компаратор, на выходе каждой из которых появляет 50 ся единица, если составляющая надежность (подаваемая на первые входы узлов соответствующей группы 21) входит в число г наименьших надежностей.Блок 13 вычисления степеней сход 55 ства содержит (фиг.З) первый - четвертый ключевые элементы 27 и первый - четвертый сумматоры-накопители 28. Блок 14 выделения максимума содержит первый - шестой узлы 29 сравнения, дешифратор 30 и буферный регистр 3 1.Блок 13 содержит информационные32 и управляющие 33 входы и вход 34обнуления, а блок 14 - вход 35 разрешения записи. Блок 12 дискретныхдекодеров содержит четыре декодеракода Голея, блок 15 регистров - четыре двадцатитрехраэрядных сдвиговыхрегистра для хранения результатовдекодирования на время вычислений вблоках 13 и 14.Блок 5 управления содержит (Фиг.4)делители частоты на двадцать четыре36, на двадцать три 37 и на четыре 38;дешифратор 39, элемент ИЛИ-НЕ 40, первый - третий элементы 41-43 ЗАПРЕТ, элемент ИЛИ 44 и первый - шестой элемен"ты И 45-50.На фиг,5 стрелками отмечены символы, инвертируемые в процессе работыаналогового декодера (предлагаемогои известного)Смысл инвертированийзаключается в попытке исправить заранее некоторые из ошибок, Например,во втором из векторов ошибок инвертируются два наименее надежных символа.Если в этих символах действительнопроизошли ошибки, то кратность исправляемых ошибок увеличивается допяти .(три ошибки в любом месте вариационного ряда исправляются приалгебраическом декодированифНа фиг.б обозначено: а - сигналобнуления на входе 18, б - тактовыеимпульсы на входе 17, в-и - сигналына выходах 51.1 - 51.7 блока 5 управления,Работа декодера происходит в дваэтапа,На первом этапе на выходы первого1 и второго 2 мультиплексоров поступают сигналы с входов 19 и 20 и втечение 24 тактов в регистр 4 записываются надежности принимаемого кодового слова, а в регистр 3 - результаты демодуляции символов этого слова, На втором этапе входы мультиплексоров 1 и 2 переключаются, в блоках 6-8 опредсляются номера двух, пяти и восьми наименьших надежностейи результаты вычислений в этих блоках записываются в их регистры 23.Затем в течение 24 тактов эти результаты последовательно выталкиваютсяна выходы блоков 6 - 8 и, благодарясумматорам 9 - 11 по модулюя два,1580566 510 5 20 25 30 35 40 45 50 55 происходит инвертирование двух, пяти и трех символов принятой комбинации (фиг.5), Четыре полученных набора (первый - без инвертирования) поступают на соответствующие входы четырех дискретных декодеров блока 12Затем четыре результата декодирования поступают на четыре сдвиговых регистра блока 15 и в блок 13, где производится вычисление степеней сходства этих результатов, после чего в блоке 14 осуществляется выбор результата с наибольшей степенью сходства. Влагодаря коммутатору 16 этот результат поступает на выход декодера, после чего декодирование завершено.Для достижения асимптотической помехоустойчивости оптимального аналогового декодера необходимо, чтобы при переборе учитывались возможныеконфигурации векторов ошибок, ненулевые компоненты которых имеют номера ряда не более чем восьми номеров наименьших надежностей. На фиг.5 изображен вариационный ряд надежностей, т.е. результат их расстановки . в порядке возрастания. Номер надежности в вариационном ряду называется рангом. Ниже стрелками отмечены составляющие, инвертируемые в известном декодере, еще ниже - в предлагаемом декодере, для примера отмечена конфигурация вектора ошибок веса "4", . которая не может быть учтена в известном.декодере. В результате перебора на ЭВИ всех 2 =256 различных конфигураций векторов ошибок установ лено, что в предлагаемом декодере исправляются все конфигурации ошибок среди символов с восемью наименьшими надежностями, а в известном декодере 88 из них не могут быть учтены. Вероятность появления именно таких конфигураций векторов ошибок наибольшая, так как ошибка чаще происходит в наименее надежных символах, Следовательно, помехоустойчивость предлагаемого декодера по сравнению с известным увеличивается. Формула изобретения 1. Аналоговый декодер расширенного кода Голея, содержащий первый мультиплексор, первый информационный вход которого является информационным входом декодера, выход первого мультиплексора соединен с информационным . входой сдвигового регистра информации, выход которого подключен к второму информационному входу первого мультиплексора, второй мультиплексор, первые информационные входы которого являются входами надежности декодера, выходы второго мультиплексора соедиФны с информационными входами сдвигового регистра надежностей, последовательные выходы которого подключены к вторым информационным входам второго мультиплексора, параллельные выходы сдвигового регистра надежности соединены с информационными входамипервого блока дешифрации, блок выделения максимума, коммутатор, блок управления, тактовый вход и вход обнуления которого являются соответственно входом синхронизации и входом обнуления декодера, первый выход блокауправления подключен к управляющимвходам мультиплексоров, о т л и ч аю щ и й с я тем, что, с целью повышения помехоустойчивости, в декодервведены первый и третий сумматоры по модулю два, блок вычисления степеней сходства, блок дискретных декодеров, блокрегистров и второй и третий блокидешифрации, информационные входы которых соответственно объединены иподключены к параллельным выходамсдвигового регистра надежности, второй и третий выходы блока управлениясоединены соответственно со входами разрешения записи и .входами сдвигапервого - третьего блоков дешифрации,выходы первого и третьего блоков дешифрации подключены к первым входамодноименных сумматоров по модулю два,выход второго блока дешифрации соединен с первым входом второго сумматора по модулю два и вторым входом третьего сумматора по модулю два,третий вход которого объединен с вторыми входами первого и второго сумматоРов по модулю два и первым информационным входом блока дискретныхдекодеров и подключен к выходу сдвигового регистра информации, выходыпервого - третьего сумматоров по модулю два соединены соответственнос вторым - четвертым информационнымивходами блока дискретных декодеров,выходы которого подключены к информационным входам блока регистров и управляющим входам блока вычислениястепеней сходства, информационныевходы и выходы которого подключенысоответственно к последовательным выходам сдвигового регистра надежностей и информационным входам блока выделения максимума, четвертый - седьмой выходы блока управления соединены соответственно с тактовыми входами блока дискретных декодеров и блока регистров, входом обнуления блока вычисления степеней сходства и входом разрешения записи блока выделения максимума, выходы которого и выходы лока регистров подключены соответственно к управляющим и информационным входам коммутатора, выход которого является выходом декодера.2. Декодер по п.1, о т л и ч аю щ и й с я тем, что блок дешифрации содержит первую - (24-г)-ю группы узлов сравнения .(г=2, 5, 8 - число наименьших надежностей), дешифратор и регистр результата, первые входы первого - (24-1)-го узлов сравнения (х=1,24-г) -й группы объединены со вторыми входами Е-го узла сравне ния (1=1, .-1) (х)-й группы и являются -ми информационными входами блока, вторые входы (24-г+х)-го - (24-)-го узлов сравнения всех групп соответственно объединены и являются 30 (24-г+1)-ми двадцать четвертыми ин- формационнымИ входами блока, выходы всех узлов сравнения всех групп подключены к соответствующим входам дешифратора, выходы которого соединены 35 с установочными входами соответствующих разрядов регистра результата, вход разрешения записи, вход сдвига и выход которого являются одноименными входами и выходами блока, 40 3. Декодер по п.1, о т л и ч а - ю щ и й с я тем, что блок вычисления степеней сходства содержит первый - четвертый сумматоры-накопители и первый - четвертый ключевые элементы, информационные входы которых соответственно объединены и являются соответствующими инфсФмационными входами блока, управляющие входы первого - четвертого ключевых элементов являются соответствующими управляющими входами блока, выходы ключевых элементов соединены с информационными входами одноименных сумматоров-накопителей, входы обнуления которых объединены и являются входами обнуления блока, выходы первого - четвертого сумматоров-накопителей являются соответственно первыми - четвертыми выходамиблока.4Декодер по п.1, о т л и ч а " ю щ и й с я тем, что блок выделения максимума содержит первый - шестой узлы сравнения, дешифратор и буферный регистр, первые входы первого - тре" тьего узлов сравнения соответственно объединены и являются первыми информационными входами блока, вторые входы первого и .первые входы четвертого и пятого узлов сравнения соответственно объединены и являются вторыми информационными входами блока, вторые входы второго и четвертого и нер" вые входы шестого узлов сравнения соответственно объединены и являются третьими информационными входами блока, вторые входы. четвертого - шестого узлов сравнения соответственно объединены и являются четвертыми информационными входами блока, выходы первого - шестого узлов сравнения соединены с соответствующими входами дешифратора, выходы которого подключены к установочным входам соответствующих разрядов буферного регистра, вход разрешения записи и выходы которого являются соответственно входом разрешения записи и выходами блока.5, Декодер но п.1, о т л и ч а - ю щ и й с я тем, что блок управления содержит делитель частоты на двадцать четыере, делитель частоты на двадцать три, делитель частоты на четыре, дешифратор, элемент ИЛИ-НЕ, элемент ИЛИ, первый - третий элементы ЗАПРЕТ и первый - шестой элементы И, входы обнуления делителей частоты на двадцать четыре и на четыре объединены. и являются входами обнуления блока, счетные входы делителей частоты на двадцать четыре и на двадцать три объединены с запрещающим входом первого и разрешающим входом второго элементов ЗАПРЕТ и с первыми входами второго и шестого элементов И и являются тактовым входом блока, выходы разрядов делителя частоты на двадцать четыре соединены с входами элементов ИЛИ-НЕ, выход которого подключен к входу обнуления делителя частоты на двадцать три и разрешающему входу первого элемента ЗАПРЕТ, вьиод которого подключен к первым входам первого и пятого элементов И, выход делителячастоты на двадцать три соединен с вторым входом шестого элемента И и запрещающим входом второго элемента ЗАПРЕТ, выход которого подключен к5 разрешающему входу третьего элемента ЗАПРЕТ и первым входам третьего и четвертого элементов И, выходы которых соединены с входами элемента ИЛИ, выход переполнения делителя частоты на двадцать четыре подключен к счет- номУ, входу делителя частоты на четыре, выходы которого соединены с входами Дешифратора, первый выход которого подключен к запрещающему входу третьего элемента ЗАЛРЕТ и являетсяпервым выходом блока, второй выходдешифратора соединен совторыми входами первого - третьего элементов И,третий выход дешифратора подключенк второму входу пятого элемента И,четвертый выход дешифратора соединенс вторым входом четвертого и третьимвходом шестого элементов И, выходыпервого, второго элементов И, третьего элемента ЗАПРЕТ, элемента ИЛИ, пятого и шестого элементов И являютсясоответственно вторым - седьмым выходами блока.з 111111 2 Э 9 5 616 У Ю 2 Ф Составитель О,РевинскТехред Л,Сердюкова Корректор И.Мус Редактор И.Горн В роизводственно-издательский комбинат "Патент", г, Ужгород, ул, Гагарина, 10 аз 2023 Тираж 662 НИИПИ Государственного комитета п 113035, Иосква, Ж Подписноеизобретениям и открытиям приРаушская наб., д. 4/5

СмотретьЗаявка

4414087, 25.04.1988

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

ГИНЗБУРГ ВИКТОР ВУЛЬФОВИЧ, ЗАХАРОВ АРИАН АРИАНОВИЧ, НАУМОВ АНАТОЛИЙ СЕРГЕЕВИЧ

МПК / Метки

МПК: H03M 13/02

Метки: аналоговый, голея, декодер, кода, расширенного

Опубликовано: 23.07.1990

Код ссылки

<a href="https://patents.su/7-1580566-analogovyjj-dekoder-rasshirennogo-koda-goleya.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговый декодер расширенного кода голея</a>

Предыдущий патент: Устройство для декодирования импульсно-временных кодов

Следующий патент: Кодек несистематического сверточного кода

Случайный патент: Антиадгезионный состав