Устройство для коррекции ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

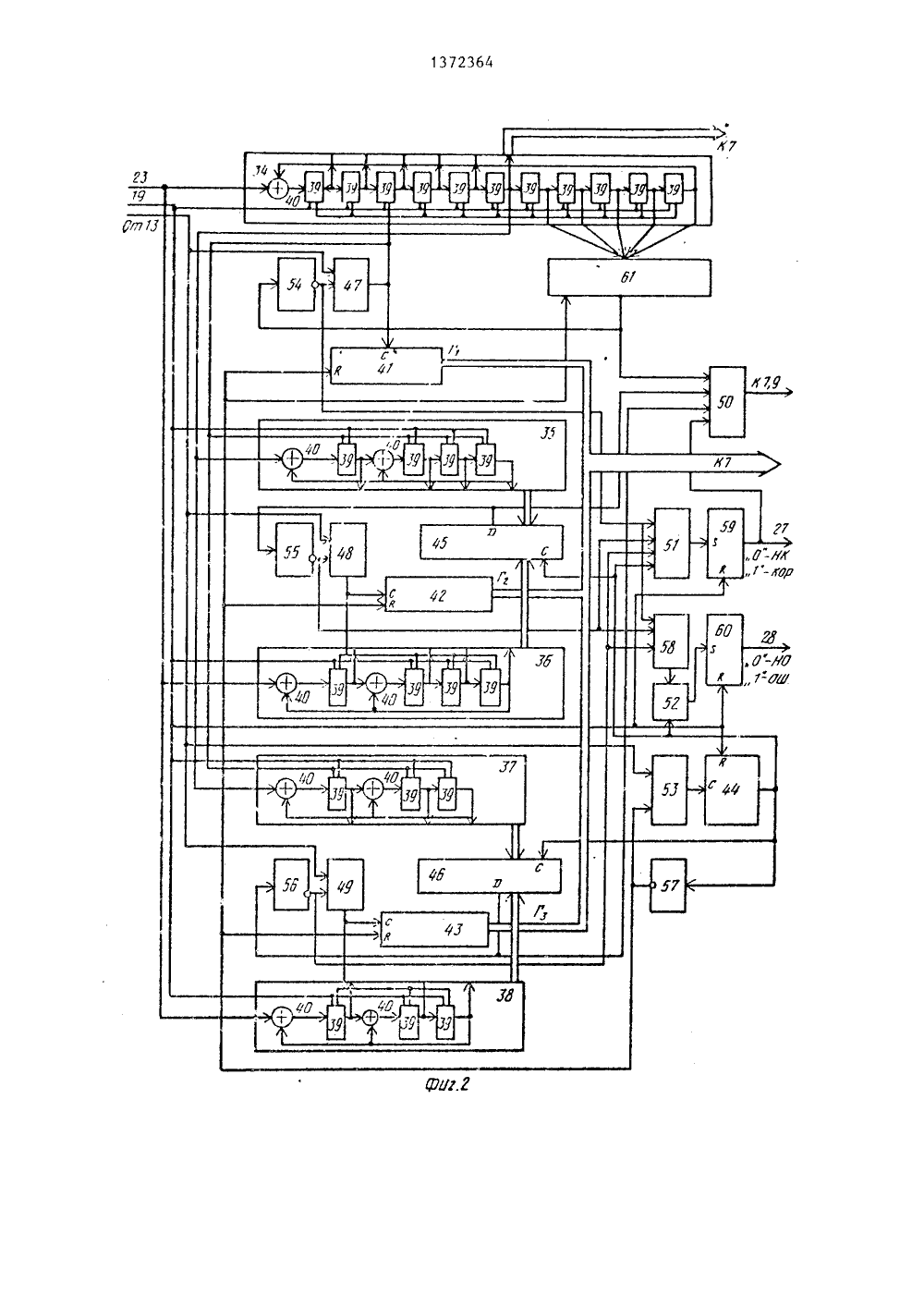

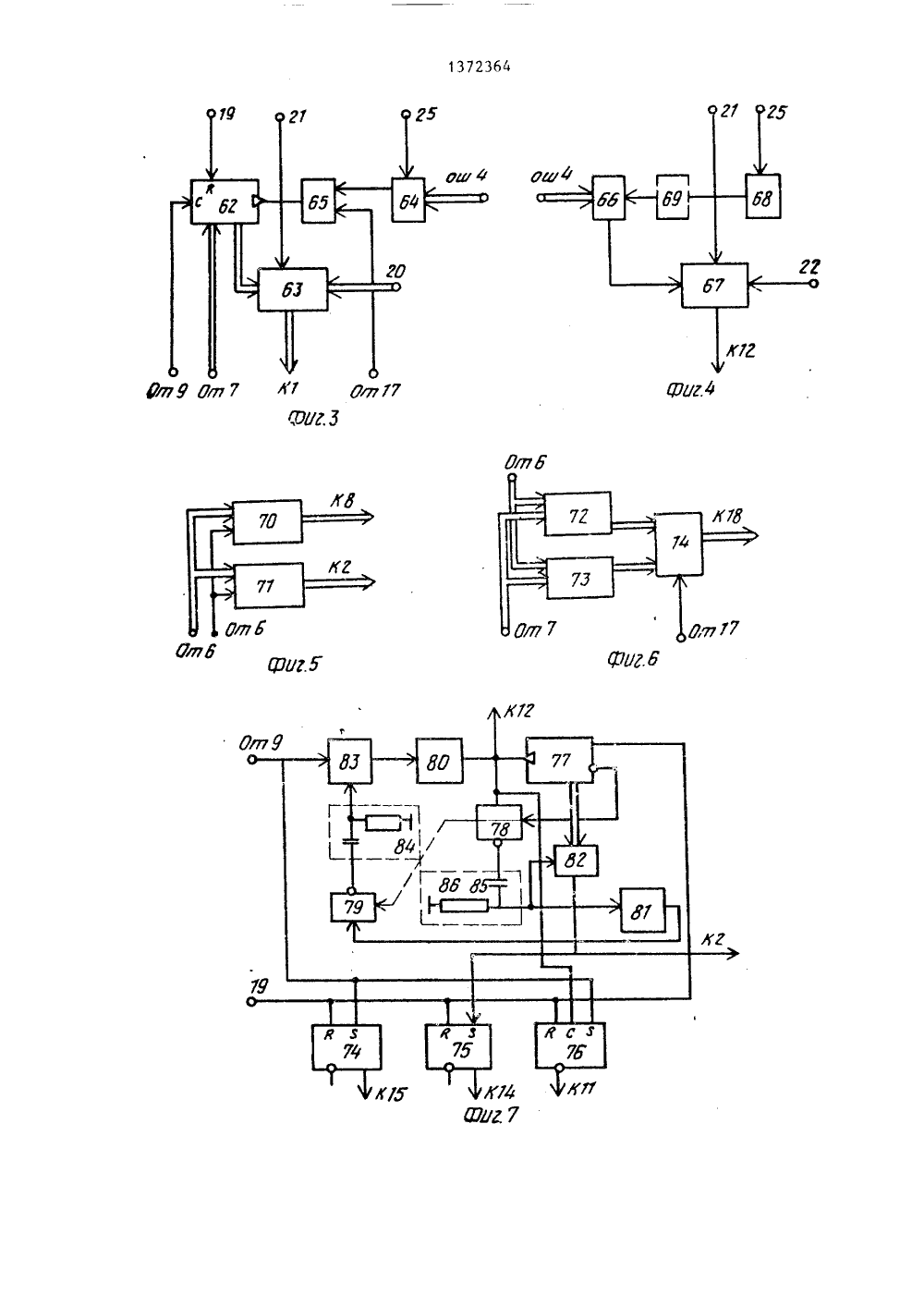

(50 4 ГОСУДАРСТВЕННЫЙ ПО ДЕЛАМ ИЗОБРЕТ ТЕТ СССРИ ОТКРЫТИЙ ОПИСАНИЕ ИЗОБРЕТЕН(21) (22) 4119423/24-2430.06,8607.02.88. Бвп. К 5Московский энергетич ий инсти И,Н.Андреев 681.327 (08 Хетагуров Я ие надежнос а и Г,А.Бо8,8)(54) УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК(57) Изобретение относится к вычислительной технике, а именно к системамкоррекции ошибок в каналах передачиблоков информации в последовательномкоде, например при считывании информации с накопителем на магнитных лентах или магнитных дисках, и можетбыть использовано, в частности, длякоррекции информации, считываемой сВУ на цилиндрических магнитных доменах. Целью изобретения является повы"шелле точности обнаружения и исправ13 ленця ошибок путем использования кода Фдйра, Устройство содержит буферный блок 1 памяти, блок 2 выбора адреса, формирователь 3 сигнала обращения, счетчик 4, преобразователь 5 последовательного кода в параллельссьссс, блок 6 обнаружения ошибок, формирователи 9, 1 О импульсов, элемент И-НЕ 11, элемент ИШ-НЕ 12, элемент ИЛИ 13, коммутаторы 14, 15, регистр 16, блок уппдвления 17, а также блок 7 пдсссстсс адресов ошибок и блок 8 памяти признаков ошибок, выполненные цз блоков постоянной памяти, Устройство обеспечивает обнаружение и коррекцию осшсбок в информации, поступакг :адей и ссоссседовдтсльцом коде ца вход 7236423 преобразователя 5, причем применение кода Файра позволяет при меньшем количестве контрольных разрядов исправлять пакеты ошибок большей длины, чем при применении кода БЧХ или кода Рида-Соломона. С выходов преобразователя 5 информация записывается в блок 1 байтами, Блок 6 позволяет выявлять признак ошибки и все необходимые данные для определения адреса ошибки с помощью блока 7. Блок 8 определяет по признаку ошибки номера ошибочных разрядов, которые поступают в формирователи 18 четности, где производится коррекция информации, считанной из блока 1 по определенному в блоке 7 адресу. 7 ил.Изобретение относится к вычислите.ссьссосс технике, а именно к системам коррекции ошибок в каналах передачи блоков ицформацлс в послдовательном ;оде, например при считывании ццфор мдцци с накопителей цд магнитных ленгдх или магнитных дисков, и может бить ссспоссьзопдссо, в састссости, для коррсксС;ссс ссссфоссс дсСисс, считываемой с ЗУ цд сСцсссссстсрсс ссссс.х ссдгцсссньсх домецх.Целью изобретения является повышение точности обссдруссепя ц исправления ошссбок путем использования кода Фйра.15На фнг. 1 представлена функциональ цдя схема предлдсдемого устройства и цдиболее ссредпочт.гс ельного варианта выполнения блока запуска; на фиг. 2- 7 - фуссс цссоссалысс,се схемы наиболее20 предпо;тцтельцых вариантов выполнессшс соответственно блока обнаружения ошибок, блока выбора адреса, формировдтг.ся сигнала обращения, блока памяти д;сресов ошибок, блока памяти призссдс.оц ошибок и блока управления,реп;сдгдемое устройство содержит (фссг,1) буферный блок 1 памяти, блок 2 выбора адреса, формирователь 3 сигнала обрдщеспся, счетчик 4, преобразователь 5 последовательного кода в пдрдл.ссельссспс, блок 6 обнаружения оасибок, блок 7 памяти адресов ошибок,блок 8 памяти признаков ошибок, первый 9 и второй 10 формирователи импульсов, элемент И-НЕ 11, элементИЛИ-НЕ 12, элемент ИЛИ 13, первый 14и второй 15 коммутаторы, регистр 16,блок 17 управления, формирователи 18четности, вход 19 начальной установки, адресные входы 20, вход 21 управления режимом, вход 22 обращения,информационный вход 23, информационные выходы 24, первый 25 и второй 26тактовые входы, выход 27 наличияошибки и выход 28 наличия корректируемой ошибки.На фиг. 1 изображен также блок 29запуска, содержащий генератор 30 импульсов, триггер 31, элемент 32 иэлем нт НЕ 33,Блок 6 обнаружения ошибок содержит (фиг,2) регистры 34"38,каждыйиз которых состоит из триггеров 39и формирователей 40 четности, счетчики 41-44, схемы 45 и 46 сравнения,элементы И 47-53, элементы НЕ 54-57,элементы ИЛИ 58, триггеры 59 и 60 иэлемент ИЛИ-НЕ 61,Блок 2 выбора адреса содержитБлок 7 памяти адресов ошибок содержит (Фиг.5) блоки 70 и 71 постоянной памяти,Блок 8 памяти признаков ошибок содержит (фиг,6) блоки 72 и 73 посто 5янной памяти.Блок 17 управления (Фиг,7) содержит на триггерах 74-76 счетчик 77,элементы И-НЕ 78 и 79, формирователи80 и 81 импульсов, дешифратор 82,,элемент ИЛИ 83, НС-цепочка 84, конденсатор 85 и резистор 86.Предлагаемое устройство работаетследующим образом, 15По входу 19 (фиг, 1) осуществляется начальная установка соответствующих блоков устроцсгва. На вход 23подают группу разрядов информации(совместно с проверО 5 ньгп рлэря(5 а 5 ц)сопровождаемую тактовыми сцгна:аипо входу 25 (дл 5 ;1, ВУ такто 5 а 5частота око.5 о ОО кГц). преобразователь 5 осуществляет цреобр;5 зова 5 п 5 споследовате,55.55 О О коц н пара,55 О 55 ьный по восемь 65 Г. На вход 21 подаютси Гнал записи ц 55 ЬОрма 55 цц, вс:еде г 55 цечего на вкоде элемата И-Е 11 пр.5 сутствует С 55 55,55 режим за 5 п.ц 55 фо 1511 1мацци в бил : 1, на 5 рцмс р 5 О.Опричем 55 а другом входе элементИ-НГ 11 в цсходног Состояни такклог. "1", О 5 Огч 5 ксбесцегы,5 сгсчет импу 55.Сз 5 с 5 зхзг 25, п 1 ц 5 че 5после вос 5 ОГО 55 ь 555 у 55.Са на в 5,хоО35счетчика 4 бус.тз 5 О 5 ас 5 отс 55 циал, обес 5 е ц 5,5 51 срабаггнч 55 н 5 еблока 2 ц 555 ор 5 Ивате 5 3. В 55 ро:ежутке между 55 о 5:5555 ц де 555 т 5; та 5;говыми Ь 5 мпульса."5 55 ро 55 сход гг стробцрование записи .в блок 1, а осле девяТОГО ПРОИСХОДЦТ 3 Ц 5 ЦСЬ НОВОГО:1 ДРЕ -са в счетчцк 62 (начальный адреснулевой). Исходное состояние 65 ока17 таково, что коммутатор 14 вкг 5 юченна пропуск информации от блока 72,коммутатор 15 включен 55 а пропускинформации от преобразователя 5, наэлемент ИЛИ-НЕ 12 поступает пулевойсигнал, на блок 2 поступает нулевойсигнал с выхода блока 17, а на элемент И-НЕ 11 поступает единичныйсигнал. Таким образом, по прошествииопределенного количества тактов, полезная информация заггисывается в блок551 в виде байтов информации, Одновременно в блоке 6 происходит обнаружение ошибки. На выходах 27 и 28появляются сигналы, свидетельствующие о наличии цлц отсутствии ошибок в считанной информации. При этом, если на выходе 27 имеется лог,"О" нет ошибки, а если лог, "1" - есть ошибка; если на выходе 28 лог,"О" некорректируемая ошибка, а если лог. 5 Ч1 - корректируемая ошибка. Дальнейшая работа устройства может быть инициирована блоком 29, который вырабатывает последовательность тактовой частоты, достаточной для срабатывания элементов блока 6, например, до 1 11 Гц.В зависимости от состояния выходов 27 ц 28 возможны следующие режи- .55 работи устройства.На ходе 27 лог. "О", Это означает, что в принятой информации ошибок нет ц Оа 5 О;сет бить цс 55 О 555 зова 5 а.На 1 кодс 27 лог, "1", а на вь 5 ходе 28 .50 Г. ООто Означает что в;5 р 5 ято Борапнц и.Ретс 5 некоррект 55 руе;5 а 5 Огнтбк кратностью От се",5,ет бнт Скорректирована, Лля этого55, вход 26 подают тактовую частоту,55 Гедствце чего через несколько такгов и входах блока 8-выходах блока 6 по.явите; призах огп 5 бкц, а информация,дос ат: ч 55 ая для Определения адресаО;п 5 б.и, - на вььодах блока 6, под 5;л 5 оченнг 5 х к блоку 7, и сигнал ошибки - на 5 гходе блока 9. Из блока 7сч 55 т 55 ется адрес первого ошибочногоб, йга (всего может быть не более двухошибочных байтов), который поступаетв блок 8 ц в блок 2, где по задержаннсму сигна 5 у с выхода Формирователя9 записывается цо параллельному входу в сч"г 5 к 62. Одновременно блок 8Осу 515 еств 5555 ет выработку номеров о 55 п 5 бочных разрядов, которые по выходам5,акоп Телей 72 и 73 поступают на соОтветствуигце входы коммутатора 14,а поскольку последний открыт дляприема информации от блока 72, топризнак ошибки первого ошибочногослова поступает на соответствующиевходы Фор,ацователей 18,В это времяблок 17 орга 5 п 5 зует работу устройства так, что последовательно по каждому из двух последовательн 5 к адресов с ошибкам 5 производится С 5 цт 55 ва 1372364ние ц злццсь информации н блоке 1.Через з.темент И-НЕ 11 устанавливается режим считывания, а через элемент ИИ-Ш, 12 обеспечивается считывание5 ицтЬормации по первому адресу с опптбкой. Считанные данные поступают в регистр 16 и там записываются посигналу с формирователя 10 спустя время, необходимое для выборки инфор мации из блока 1. Коммутатор 15 вэтом режиме и далее н процессе коррекции устанавливается на прием информации от Формирователей 18. Данные и признак ошибки и формцронателях 15 18 позволяют исправить опптбку, искорректированные данные поступают нл ходы блока 1. Элемент ИЕ 11тбеспеттттлет устлцонку ражцмл записи, л сцгцлл че 1)ез элемент И 11 ИНЕ 12 20 обеспечивает запись скорректированной ттфсрмлцци по тому же адресу, котстрт,тй затем увсличинается на едцнитгт по сцгцл.тту с блока 17, Затем вновь осуп 1 естляется считынацие иформа т;цш, ест коррекция и злпист. н блок 1. тлтсцм образом, до прихода очередног. цмп; .тел по ходу 25 происходит нс.я коррекция длттнттх ц сигнал на ттхсде 25 .стжет служить концом операттцт.Встз; жцо осращение к блоку 1, цатт 1 цтмер, ог тцтешцего процессора. Для этот о цл ттхеце 21 необ.".одтт о устацоттцтт. режттм стттггьтттлтттпт, цл тзходы 20 подать лдрес цц ересующец ячейки цлттнтц блока 1, тта нхсд 22 подать ецпьлл ттбтрлщения ц на выходах 24 можно (через время считывания) полуцттть тттттт ормлтцпо.Таким обрлзом, и предлагаемом устра тст обеспечена возможность коррекцт тт инфо 1 тмлциц с помощью кода Флйра, что позопет исправлять пан.ты ошибок большей длины при меньшем ко:цгестве проверочных разрядов, чем прц использовании кода БЧХ или кода 1 тцдл-Соломона, Блок 6 позволяет обнлръ-жттнлть опптбки в течение такта с ",итынлттця информации и исправлять цх (точнее, выявлять признак ошибки и нсс необходимые данные для вырабстттси лц,тесл опптбкц), Блок 6 предназначен для обработки пакетов информацтти длиной до 1155 бит, включая проверочные стсемнадцать бит. В конкрет цом устройсттте используется код Файра, опцсынлемьпт многочленом (х +1. т х сьх+1) (х+х+1), который позволяет исправить пакеты ошибокдо шести бит и обнаружинать пакетыошибок до двенадцати бит.Ф о р м у л а и з обретенияУстройство для коррекции ошибок, содержащее блок обнаружения ошибок, буферный блок памяти, первый коммутатор, блок памяти адресов ошибок, блок памяти признаков ошибок и формирователи четности, одни из входов которых подключены к выходам первого коммутатора, информационные входы которого соединены с выходами блока памяти признаков ошибок, одни из входов которого подключены к выходам первой групь; блока обнаружения ошибок, выходы второй группы которого соединены с адресными входами блока памяти адресов ошибок, о т л и ч а ющ е е с я тем, что, с целью повышения точности обнаружения и исправления ошибок путем использования кода Файрл, в него введены блок выбора адреса, второй коммутатор, счетчик, Формирователь сигнала обращения, регистр, блок управления, первый и второй формирователи импульсов, элемент И-НЕ, элемент ИЛИ-НЕ, элемент ИЛИ и преобразователь последовательного кода и параллельный, выходы которого подключены к одним из информационных входов второго коммутатора, другие информационные входы и выходы которого соединены соответственно с выходами формирователей четности и с информационньпи входами беферного блока памяти, причем выходы счетчика подключены к входам разрешения запуска блока выбора адреса и формирователя сигнатта обращения, входы разрешения выдачи которых и первый вход элемента И-НЕ объединены и являются входом управления режимом работы устройства, адресными входами которого являются одни из адресных входов блока выбора адреса, другие адресные входы которого подключены к выходам блока памяти адресов ошибок и другим входам блока памяти признаков ошибок, счетный вход и выходы блока выбора адреса соединены соответственно с первым ныходом блока управления и адресными входами буферного блока памяти, вход записи/гчтения и вход разрешения записи/чте- ния которого соединены соответствен 71372364но с выходом элемента И-НЕ и с выходом элемента ИЛИ-НЕ и входом второгоформирователя импульсов, выход которого подключен к управляющему входурегистра, входы и выходы которогосоединены соответственно с выходамибуферного блока памяти и с другимивходами формирователей четности,управляющий вход второго коммутатора подключен к второму выходу блокауправления, третий и четвертый выходы которого соединены соответственно с вторым входом элемента И-НЕи с первым входом элемента ИЛИ-НЕ,второй вход которого подключен к выходу формирователя сигнала обращения,вход обращения которого является входом обращения устройства, а входзапуска соединен со счетным входом 2 Осчетчика, входом запуска блока выбора адреса, входом синхронизациипреобразователя, последовательногокода в параллельньп, первым входомэлемента ИЛИ и является первым тактовым входом устройства, вторым тактовым входом которого является второй вход элемента ИЛИ, выход которогоподключен к входу запуска блока обнаружения ошибок, первый выход которого подключен к входу обращения блока памяти адресов ошибок и входупервого формирователя импульсов, выход которого соединен с входами1синхронизации блока управления и блока выбора адреса, вход установки которого подключен к входу установкисчетчика, блока управления, блокаобнаружения ошибок и является входомначальной установки устройства, информационными выходами которого являются выходы буферного блока памяти,входы данньпс преобразователя последовательного кода в параллельный и блока обнаружения ошибок объединеныи являются информационным входомустройства, пятый выход блока управления подключен к управляющему входупервого коммутатора, второй и третийвыходы блока обнаружения ошибок являются соответственно выходом наличияошибки и выходом наличия корректируемой ошибки устройства.

СмотретьЗаявка

4119423, 30.06.1986

МОСКОВСКИЙ ЭНЕРГЕТИЧЕСКИЙ ИНСТИТУТ

АНДРЕЕВА ИРИНА НИКОЛАЕВНА, БОРОДИН ГЕННАДИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G11C 29/00

Опубликовано: 07.02.1988

Код ссылки

<a href="https://patents.su/7-1372364-ustrojjstvo-dlya-korrekcii-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для коррекции ошибок</a>

Предыдущий патент: Постоянное запоминающее устройство с резервированием

Следующий патент: Устройство для коррекции ошибок в информации

Случайный патент: Роликовая червячная передача качения