Устройство для коррекции ошибок в информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

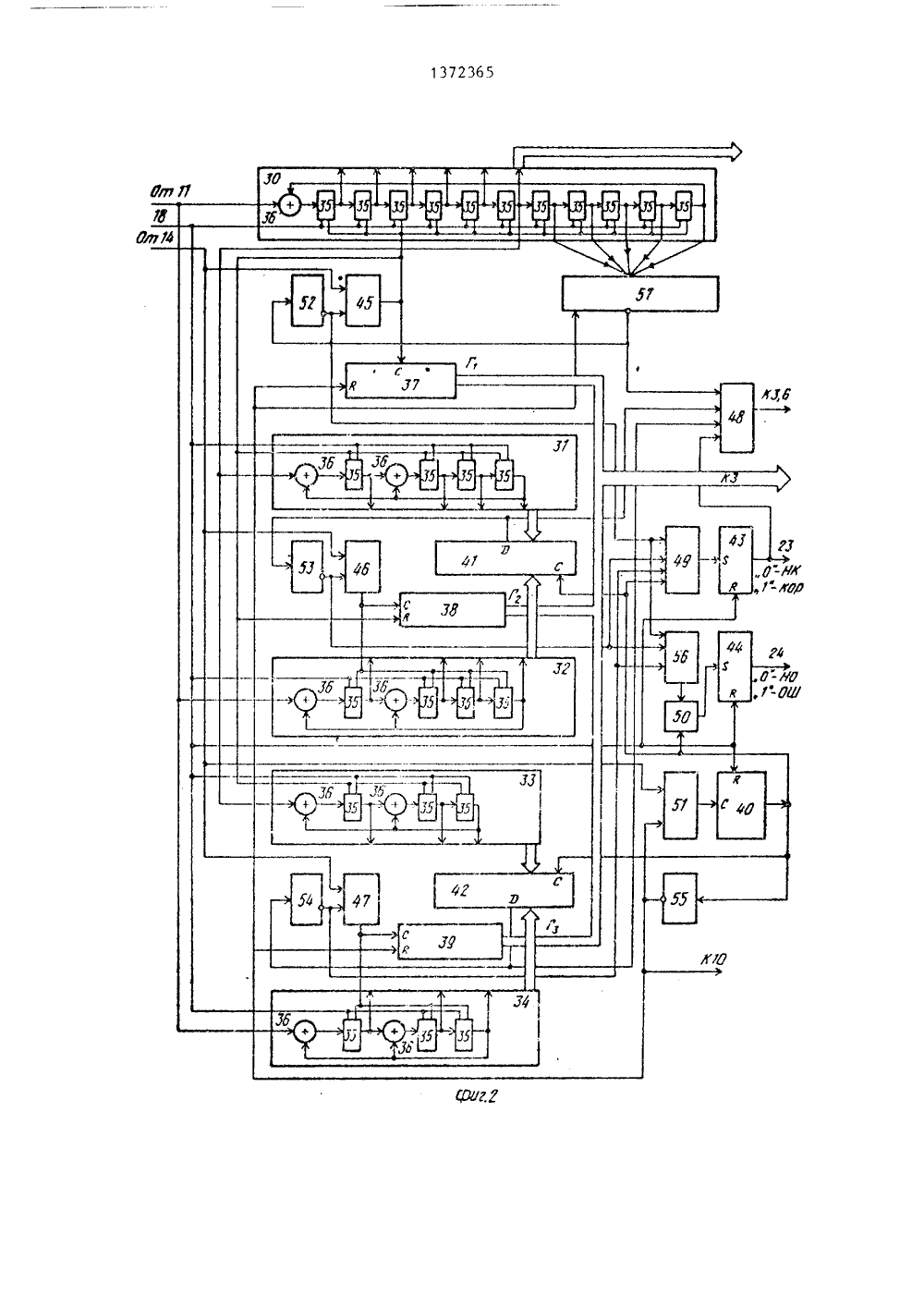

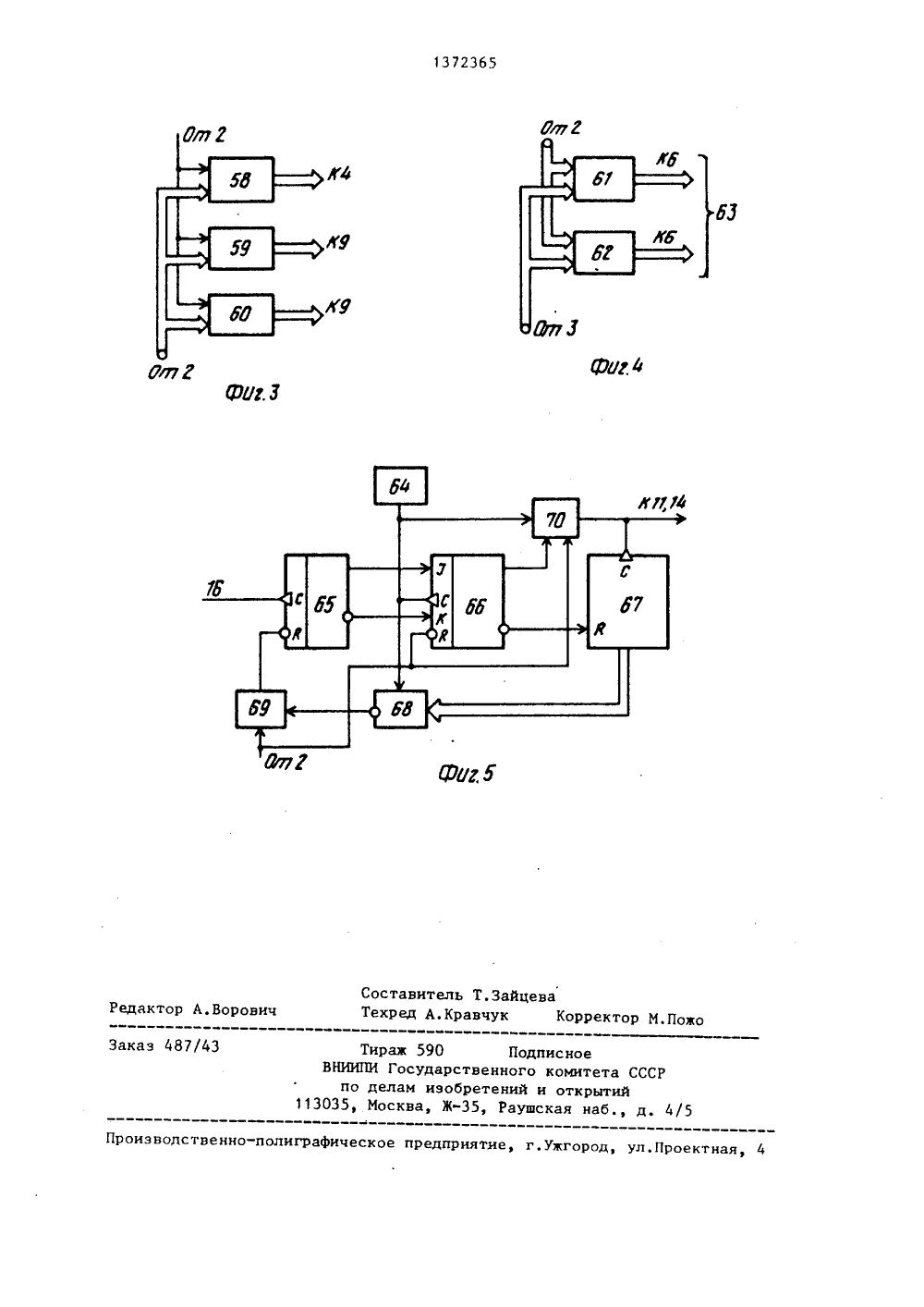

,ЯО 1372365 А 1 511 4 С 11 С 29/00 ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(71) Московский энергетический институт(56) Хетагуров Я.А., Руднев Ю.П. Повышение надежности цифровых устройств методами избыточного кодирования, М.: Энергия, 1974, с.76.Зарубежная радиоэлектроника, 1985, У 7, с.11, рис.4.(54) УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОКВ ИНФОРМАЦИИ(57) Изобретение относится к вычислительной технике,а именно к устройствам для коррекции информации,и может быть применено для исправления пакетов ошибок, возникающих при передаче блоков информации иэ внешних запоминающих устройств с параллельным считыванием, таких, как накопители на магнитных барабанах и цилиндрических магнитных доменах. Целью изобретения является повышение быстродействия устройства. Устройство содержит буферный блок 1 памяти, блок 2 обнаружения ошибок, блок 3 памяти адресов ошибок, блок 4 памяти приз(байтами) записывается через входы21 в буферный блок 1 памяти и в регистр 11 сдвига, из которого каждыйбайт данных сдвигается и поступает Изобретение относится к вычислительной технике, а именно к устройствам для коррекции информации, и может быть использовано для исправления пакетов ошибок, возникающих при передач блоков информации из внешних запоминающих устройств с параллельным считыванием, таких, как ,накопители на магнитных барабанах, цилиндрических магнитных доменах,елью изобретения является повышение быстродействия устройства информации.На Фиг. 1 представлена функционзльная схема предлагаемого устройства и наиболее предпочтительный вариант выполнения блока запуска; на фиг. 2 - 5 - наиболее предпочтительные варианты вьполнения соответственно блока обнаружения ошибок, блока памяти адресов ошибок, блока памяти признаков ошибок и блока синхронизации.Предлагаемое устройство содержит (Фиг.1) буферный блок 1 памяти, блок 2 обнаружения ошибок, блок 3 памяти адресов ошибок, блок 4 памяти признаков ошибок, формирователи 5 четности, группу коммутаторов 6, первый 7 и второй 8 коммутаторы, блок 9 сравнения, блок 10 синхронизации, регистр 11 сдвига, счетчик 12, фо 11 мирователь 13 импульсов, элемент ИЛИ 14, адресные входы 15, первый 16 и второй 17 тактовые входы, вход 18 начальной установки , вход 19 управления режимом вход 20 обращения, информационные входы 21 и выходы 22 устройв блок 2 обнаружения ошибок, которыйвырабатывает с использованием кодаФайра все данные, необходимые дляопределения адреса и характера ошибки, Коррекция информации, считаннойиз буферного блока 1 памяти по определенному адресу ошибки, выполняетсяформирователями 5 четности, Сигналына выходах 23 и 24 соответствуютналичию ошибки и наличию корректируемой ошибки в информации. 5 ил. ства, выход 23 наличия ошибки и выход 24 наличия корректируемой ошибки.Блок 25 запуска содержит (фиг,1)элемент НЕ 26, триггер 27, генера"5 тор 28 импульсов и элемент И 29.Блок 2 обнаружения ошибок (фиг,2)содержит сдвиговые регистры 30-34,состоящие из Р-триггеров 35 и формирователей 36 четности, счетчики 3740, схемы 41 и 42 сравнения, триггеры 43 и 44, элементы И 45-51, элементы НЕ 52-55, элементы ИЛИ 56 иИЛИ-НЕ 57.Блок 3 памяти адресов ошибок соцержит (фиг.3) блоки 58-60 постоянной памяти,Блок 4 памятипризнаков ошибок содержит (фиг,4) блоки 61 и 62 постоянной памяти с выходами 63.20Блок 10 синхронизации содержит(Фиг.5) генератор 64 импульсов, триггер 65 и 66, счетчик 67, дешифратор68 и элементы И 69 и 70.Предлагаемое устройство работаетследующим образом.Перед приемом каждого очередногоблока информации производится начальная установка по входу 18 (фиг. 1)Затем информация в параллельном коде,например, байтами поступает на входы21, синхронизируемая тактовыми сигналами по входу 16 (например, дляЦИД ЗУ частотой 100 кГц), На вход19 подается сигнал записи, вследствие чего коммутаторы 7 и 8 включенына передачу информации соответственно со счетчика 12 и входа 16, Посчетчик 12 увсличивает значение адреса на единицу, а в момент действия тактового импульса через коммутатор 8 обеспечивается подача сигнала обра 5 щения на блок 1,вследствие чего информация в параллельном коде записывается в блок 1. Кроме того, информация заносится по параллельным входам в регистр 11. По окончании тактового импульса блок 10 вырабатывает восемь импульсов сдвига информации(при байтовой передачеинформации),вследствие чего информация из регистра 11 в последовательном коде заносится в блок 2, который может обеспечивать исправление пакета ошибок длиной шесть бит и обнаружение пакета оши- бок длиной двенадцать бит при использовании кода Файра с многочленом 20 (х" +1) (х ф + х+1)(х +х+1) в информационной последовательности длиной до 1155 бит при восемнадцати проверочных разрядах, После приема всей последовательности информации 25 до 1155 бит блок 2 определяет наличие ошибки, что характеризуется состоянием его выходов 23 и 24.Если на выходе 23 и 24 нули,это означает, что ошибки цет и информация из блока 1 может быть считана по адресу, поступающему по входам 15, и сигналу обращения, поступающему по входу 20, при режиме считывания ца входе 19, который переводит коммутаторы 7 и 8 ца прием информации со 35 ответственно с входов 15 и 20.Если на выходе 23 единица - признак ошибки, а на гыходе 24 цель признак некорректпруемой ошибки (кра тностью семь - двенадцать бит), то в этом случае в принятой информации имеется ошибка и ее использоватьнельзя,Если на выходах 23 и 24 единицы, 445это означает, что имеется в принятойинформации корректируемая ошибка(кратностью от одного до шести бит),В этом случае работа блока 2 должнабыть продолжена еще на двадцать шесть50тактов импульсами, поступаощими,например, от блока 5 на вход 17.Частота импульсов может быть высокойнастолько, чтобы успевали срабатывать узлы блока 2. Через двадцатьшесть тактов на выходах блока 2 по"55является признак наличия ошибки, который поступает на входы блока 4,сигнал окончания поиска ошибки, по-. ступающий к блокам 3 и 6, а также информация, достаточная для определения адреса ошибки, поступающая ца входы блока 3. Блок 3 вырабатывает три группы данных: адреса первого и второго ошибочных байтов, которые поступают на блок 9, а также номер первого ошибочного разряда, который совместно с адресом первого ошибочного байта поступает на вход блока 4, из которого считываются признаки ошибки в тех разрядах, в которых они обнаружены. Признак ошибки поступает на входы коммутаторов 6 (одновременно и параллельно для первого и второго ошибочных байтов). После этого работа по приему информации заканчивается и можно перейти к считыванию информации. Она происходит описанным способом выше для всех слов, которые не имеют ошибок, Слова, содержащие ошибки (а их может быть всего два), корректируются за счет того, что из блока 3 получен адрес ошибочных слов, который в блоке 9 сравцивается с адресами, поступающими по входам 15. Когда наступает совпадение этих адресов, открывается один из коммутаторов 6,и соответствующий признак ошибки поступает ца формирователи 5, которые корректируют информацию.Таким образом, в предлагаемом устройстве обеспечено обнаружение и коррекция пакетных ошибок за счет применения кода Файра при считывации данных параллельным кодом, за счет чего расширяется область его применения для считывания информации с внешних запоминающих устройств.Использование кода Файра позволяет исправить пакеты ошибок большой длины при меньшем количестве проверочных разрядок чем при применении кода БЧХ или кода Рида-Соломона.Формула из обретенияУстройство для коррекции ошибок в информации, содержащее блок обнаружения ошибок, буферный блок памяти, блок памяти адресов ошибок, блок памяти признаков ошибок, группу коммутаторов и формирователи четности, выходы которых являются информационными выходами устройства, входом управления режимом работы которого является вход записи/чтения буферного блока памяти, выходы которого подключены к одним из входов формирователей четности, другие входы которых подключены к выходам коммута 5 торов группы, одни йз информационных входов которых подключены к выходам блока памяти признаков ошибок, одни иэ адресных входов которого соединены с выходами первой группы блока обнаружения ошибок, выходы второй группы которого подключены к адресным входам блока памяти адресов ошибок, о т л и ч а ю щ е е с я тем, что, с целью повышения быстодейст" вия устройства, в него введены счетчик, регистр сдвига, первый и второй коммутаторы, блок синхронизации, блок сравнения, формирователь импульсов обращения и элемент ИЛИ, выход кото рого подключен к входу запуска блока обнаружения ошибок, вход установки которого и вход сброса счетчика объединены и являются входом начальной установки устройства, счетный 25 вход счетчика, вход записи регистра сдвига, вход пуска блока синхронизации и первый вход данных второго коммутатора объединены и являются первым тактовым входом устройства, 3 О вторым тактовым входом которого является первый вход элемента ИЛИ, второй вход которого соединен с выходом блока синхронизации и тактовым входом регистра сдвига, входы данных которого соединены с информационными входами буферного блока памяти иявляются информационнымн входамиустройства, причем выход регистрасдвига подключен к входу данных блока обнаружения ошибок, первый и второй выходы которого соединены соответственно с входом останова блокасинхронизации с управляющими входамикоммутаторов группы и входом стробирования блока памяти адресов ошибок,выходы которого подключены к другимадресным входам блока памяти признаков ошибок и одним из входов блокасравнения, выходы которого соединеныс другими информационными входамикоммутаторов группы, выходы счетчика подключены к одним иэ информационных входов первого коммутатора, выходы которого соединены с адреснымивходами буферного блока памяти, входобращения которого подключен к выходу формирователя импульсов, входкоторого соединен с выходом второгокоммутатора, второй вход данных которого является входом обращения устройства, управляяцне входы первогои второго коммутаторов соединены свходом записи/чтения буферного блокапамяти, другие информационные входыпервого коммутатора и другие входыблока сравнения объединены и являются адресными входами устройства,третий и четвертый выходы блока обнаружения ошибок являются соответственно выходом наличия ошибки н выходомналичия корректиоуемой ошибки устройства.1372365 Составитель Т.Зайцева Техред А,Кравчук Корректор М.Пожо Редактор А.Ворович Заказ 487/43 Тирах 590 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж"35, Раушская наб., д. 4/5

СмотретьЗаявка

4119424, 30.06.1986

МОСКОВСКИЙ ЭНЕРГЕТИЧЕСКИЙ ИНСТИТУТ

АНДРЕЕВА ИРИНА НИКОЛАЕВНА, БОРОДИН ГЕННАДИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: информации, коррекции, ошибок

Опубликовано: 07.02.1988

Код ссылки

<a href="https://patents.su/6-1372365-ustrojjstvo-dlya-korrekcii-oshibok-v-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для коррекции ошибок в информации</a>

Предыдущий патент: Устройство для коррекции ошибок

Следующий патент: Устройство для обнаружения и коррекции ошибок

Случайный патент: Съемный грунтонос