Генератор псевдослучайных испытательных последовательностей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1354401

Авторы: Вилинский, Гроль, Наконечный, Равняго, Романкевич, Рубаник

Текст

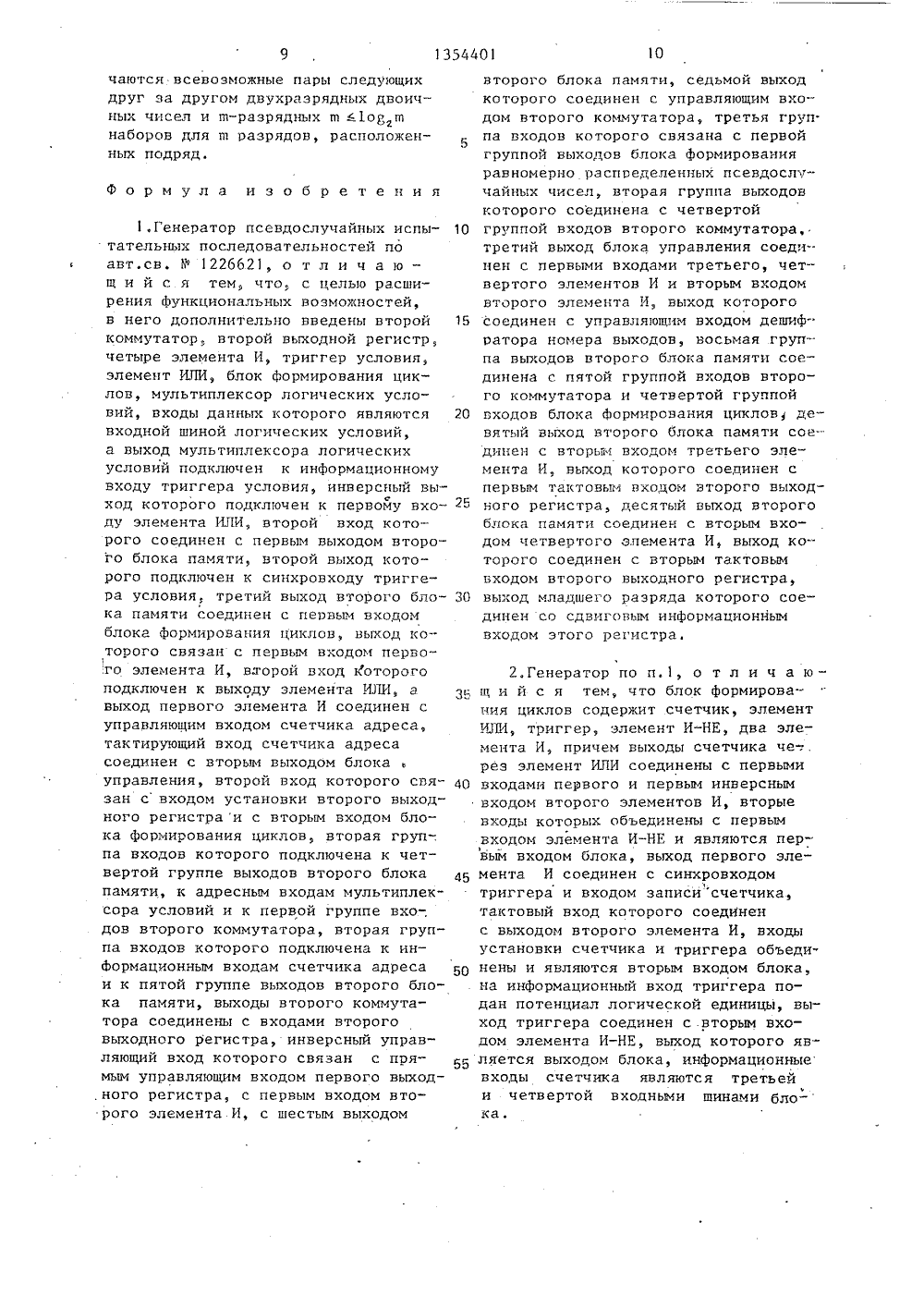

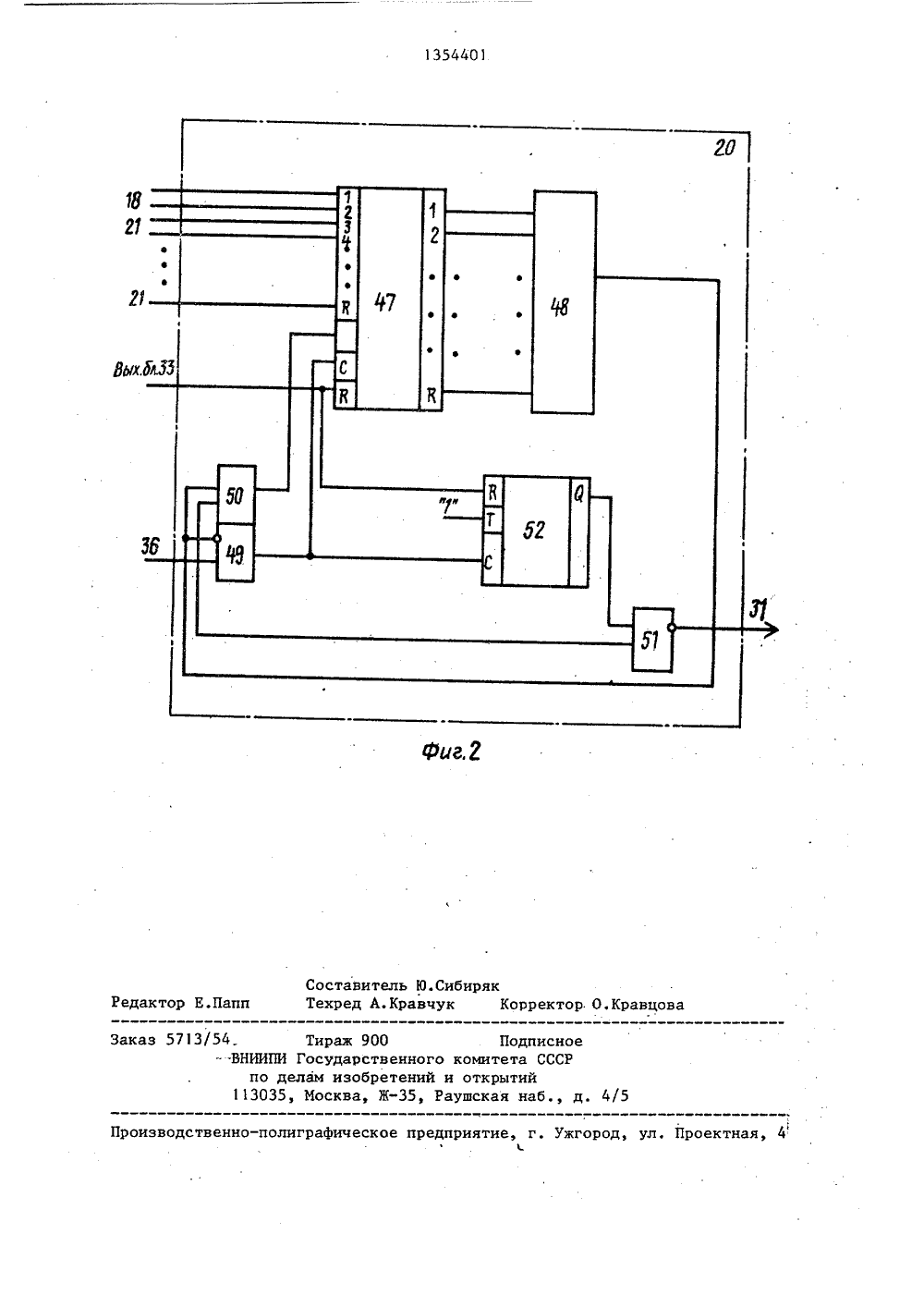

(54) ГЕНЕРАТОРТАТЕЛЬНЫХ ПОСЛЕ ЕВДОСЛУЧАЙНЫХ ИСПЫВАТЕЛЬНОСТЕЙ инсти брьсскии,ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ ОПИСАНИЕ ИЗОБР Н А ВТОРСНОМУ СВИДЕТЕЛЬСТ(71) Киевский политехническийтут им. 50-летия Великой Окткой социалистической революци(57) Изобретение может быть использовано в аппаратуре контроля и диагностики цифровых блоков для выработкииспытательных последовательностей сзаданными свойствами. Цель изобретения - расширение функциональных .возможностей устройства. Генераторсодержит блок 1 формирования равномерно распределенных псевдослучайныхчисел, блоки 3, 13 памяти, блок 5формирования выходных сигналов, ком-,1354401 25 мутатор 7, дешифратор 8 номера выходов, выходной регистр 9, счетчик 12адреса.и дешифратор 19 признаков,Кроме того, устройство включаетблок 20 формирования циклов, блок25 управления, генератор 26 тактовыхимпульсов и блок 33 начальной установки. В устройство введены мультиплексор 15 логических условий, коммутатор 7, выходной регистр 34;1 Изобретение относится к импульсной технике, может быть использовано в аппаратуре контроля и диагностики цифровых блоков для выработкииспытательных последовательностейс заданными свойствами и являетсяусовершенствованием устройства поавт.св, У 1226621,Цель изобретения - расширение 1 Офункциональных возможностей.Поставленная цель достигается засчет обеспечения циклического режимаработы и анализа логических условийполучения псевдослучайных и детерми1нированных последовательностей,сформированных в виде параллельныхи-разрядных кодов с вероятностью 1/2появления единицы в каждом разрядекода, получения такой последователь Оности и-разрядных двоичных чисел,что для последовательности щ-разрядных двоичных чисел (щ разрядов выбираются произвольно из и) имеетместо следующее свойство: в любойщ-разрядной двоичной последовательности встречаются всевозможные парыследующих друг за другом щ-разрядныхдвоичных чисел, обеспечивая параметрщ=2 и щ 1 о 8 и для любых щ разрядов, 30расположенных подряд.На фиг. представлена функциональная схема генератора псевдослучайных испытательных последовательностей; на Фиг.2 - Функциональная схема блока формирования циклов.Генератор псевдослучайных испытательных последовательностей содержитблок 1 формирования равномерно распределенных псевдослучайных чисел, аОкоторый выходами 2 подключен к адэлементы И 32, 38, 42 и 43, триггер22 условия и элемент ИЛИ 46. Благодаря этому обеспечивается циклическийрежим работы и анализ логическихусловий получения псевдослучайныхи детерминированных последовательностей, сформированных в виде параллельных и-разрядныхкодов с вероятностью1/2 появления единицы в каждом разряде кода. 1 з.п. Ф-лы, 2 ил. ресным входам блока 3 памяти, выходы 4 которого подключены к первой группе входов блока 5 Формирования выходных сигналов, а выходы 6 - к первой группе входов коммутатора 7, Выходы коммутатора 7 связаны с входами дешифратора 8 номера выходов, выходы которого соединены с синхровходами триггеров выходного регистра 9, к информационным входам которого подключен выход 10 блока 5, к второй группе входов блока 5 подсоединены выходы 11 блока 1.Выходы счетчика 12 адреса подключены к адресным входам блока 13 памяти, Содержимое счетчика 12 адреса зависит от логических условий, Группа входов 14 мультиплексора 15 логических условий является группой входов логических условий. Выходы 16 блока 13 памяти соединены с второй группой входов коммутатора 7, с первой группой информационных входов коммутатора 17 и с входами счетчика 2 адреса, а выходы 18 блока 13 памяти подключены к входам дешифратора 19 признаков, а также к второй группе инФормационных входов коммутатора 17 и первой группе входов блока 20 формирования циклов, Выходы 21 блока 13 памяти подключены к третьей группе входов коммутатора 17, к второй группе входов блока 20 формирования циклов и к адресным входам мультиплексора 15, выход которого подключен к информационному входу триггера 22 условия.Выход 23 дешифратора 19 поизнаков подключен к управляюшемч входу коммутатора 7 и к блоку 5, а выходы24 дешифратора 19 подключены ктретьей группе входов блока 5.Блок 25 управления связан с генератором 26 тактовых импульсов входами 27 и 28. Выход 29 блока 25 управления связан с тактовым входом блока1 и с тактовым входом счетчика 12 адреса, Синхровход триггера 22 условиясвязан с выходом 30 блока 13 памяти.Выход 31 блока формирования циклов20 подключен к первому входу элемента И 32, выход которого соединен суправляющим входом счетчика 2 адреса, Установочный вход счетчика2 адреса связан с выходом блока 33начальной установки, с блоком 1, сблоком 20 формирования циклов, с установочными входами выходных регист-ров 9 и 34, выходы которых являютсявыходами генератора испытательных последовательностей.Выходы 11 и выходы 2 блока 1 соединены с четвертой группой входовкоммутатора 17, выходы которого подключены к входам выходного регистра34, Управляющий вход коммутатора 17подключен к выходу 35 блока 13 памяти, выход 36 которого подключен кблоку 20 формирования циклов, а выход37 блока 13 памяти подключен к прямому управляющему входу (пРазрешениевыдачи" ) выходного регистра 9, инверсному управляющему входу ("Разрешение выдачи") выходного регистра34 и первому входу элемента И 38,Второй вход элемента И 38 связан свыходом 39 блока 25 .управления, авыход элемента И 38 связан с разрешающим входом дешифратора 8 номеравыходов,Выход 40 блока 25 управления соединен с управляющими входами блоков памяти 3 и 13, выход 41 последнего связан с элементом И 42, выход которого подключен к первому тактовому входу выходного регистра 34, а второй вход - к выходу 39 блока 25 управления и к первому входу элемента И 43, второй вход которого соединен с выходом 44 блока 13 памяти. Выход элемента И 43 подключен к второму тактовому входу выходного регистра 34, выход младшего разряда которого подключен к сдвиговому инфор. - мационному входу выходного регистра 34. Выход 45 блока 13 памяти связан с первым входом элемента ИЛИ 46, второй вход которого соединен с инверснымвыходом триггера 22 условия, а выход элемента ИЛИ 46 подключен к второму входу элемента И 32,Блок 20 формирования циклов(фиг.2) содержит счетчик 47, входыкоторого являются входами 18 и 21блока 20 формирования циклов, эле-.10 мент ИЛИ 48, входы которого подключены к выходам счетчика 47, а выходсоединен с инверсным входом элементаИ 49, и первым входом элемента И 50.Второй вход элемента И 50 и пря мой вход элемента И 49 соединены спервым входом элемента И-НЕ 51 и являются входом 36 блока 20 формирования циклов. Выход элемента И-НЕ 51является выходом 31 блока 20 форми рования циклов.Второй вход элемента И-НЕ 51 подключен к выходу Т-триггера 52, синхровход которого связан с входом записи счетчика 47 и выходом элемента 25 И 49.На Т-вход триггера 52 подается уровень логической единицы, вход установ. ки в нулевое состояние подключен квходу установки в нулевое состояниеЗ 0 счетчика 47 и связан с выходом блока 33 начальной установки. Выход элемента И 50 связан со счетным входомсчетчика 47,Генератор работает следующим об 35Блоки 3 и 13 памяти заполненыследующим образом,В каждой ячейке блока 3 памяти записано слово, состоящее из двух час-.40 тей. Младшие разряды представляют собой код вероятности появления единичного сигнала, а старшие - код номера выхода генератора псевдослучайныхпоследовательностей.45 Каждое слово блока 3 памяти определяет номер выхода для выходного регистра 9 (код номера выхода записанв старших разрядах ячейки), на котором должен появиться сигнал с заданной вероятностью (код вероятностизаписан в младших разрядах ячейки).В каждой ячейке блока 13 памяти записано слово, состоящее из трех частей и группа функционально отдельных55 разрядов. Группа таких отдельных разрядов моЖет включать, например, семьразрядов.Первый разряд слова по выходу37 предназначен для управления выда 1354401чей испытательных последовательностейи первого и второго выходных регистров 9 и 34 и, одновременно, совместно с выходом блока 25 управления раз 5 решения работы дешифратора 8 номера выходов. Второй разряд слова по выходу 35 предназначен для управления коммутатором 17. Третий разряд слова по выходу 41 предназначен для управ О .ления синхровходом второго выходного регистра 34. Четвертый разряд слова по выходу 44 используется для синхронизации сдвига выходного регистра 34. Пятый разряд слова по выходу 36 используется для формирования признака циклического режима работы генератора пьеэослучайных испытательных последовательностей. Шестой разряд слова по выходу 30 предназначен для синхронизации занесения информации в триггер 22 условия. Седьмой разряд слова по выходу 45 управляет разрешением выдачи инФормации с выхода триггера 22 условия, 25Первая часть слова (выходы 18) может задавать код вероятности сигнала для блока 5, используется как первая часть разрядов детерминированного слова при записи такого слова из ЗО блока 13 памяти на регистр 34 и используется как младшая часть разрядов слова, задающих количество циклов повторения последовательности слов блока 13 памяти для блока 20 формирования циклов.Вторая часть слова (выходы 16) блока 13 памяти может задавать код номера выхода выходного регистра 9, использоваться для формирования адреса 4 О возврата при циклическом повторении последовательности слов блока 13 памяти, или использоваться в качестве второй, части разрядов детерминированного слова. 45Третья часть слова (выходы 21) бло. ка 13 памяти используется как адрес мультиплексора 15, может задавать старшую часть разрядов слова для блока формирования циклов 20 или состав-лять третью часть разрядов детерминированного слова при выдаче его из блока 13 памяти на выходной регистр 34.Блок 33 представляет собой стандартный генератор одиночных импульсов синхронизированной с генератором 26 тактовых импульсов (связь не показана). 1 а выходах генератора псевдослучайных испытательных последовательностей можно получить сигналы следующих типов: 0 - на заданном выходе генератора появляется сигнал логического нуля; "1" - на заданном выходе генератора появляется сигнал логической единицы; разряд псевдоциклического кода - только на одном выходе генератора происходит изменение значения сигнала, причем единичное значение сигнала устанавливается с заданной вероятностью; равновероятный сигнал - "01 или 1" появляется назаданном выходе генератора с вероятностью Р = 0,5; импульсный единичный сигнал с фиксированной вероятностью; импульсный нулевой сигнал с Фиксированной вероятностью.В начальном состоянии блок 33 устанавливает счетчик 12 адреса, выходные регистры 9 и 34, блок 25 управления, блок 20 формирования циклов в нулевое состояние, а в блоке 1 устанавливается код, не равный нулевому. Возможность адаптации (настройки) генератора на различные типы последовательностей обусловлена конструктивно простой сменой микросхем блоков памяти 3 и 13 (микросхемы постоянных запоминающих устройств).Работа генератора испытательных последовательностей синхронизируется блоком 25 управления, на входы которого поступают две сдвинутые синхросерии из генератора 26 тактовых импульсов.Время появления сигнала на входе разрешения,дешифратора 8 определяется максимальной задержкой появления сигнала на одном из п входов триггеров выходного регистра 9. Этот же сигнал синхронизирует работу регистра 34.Блок 1 в каждом такте генерирует равновероятный псевдослучайный код, который поступает на адресные входы блока 3 памяти и при этом выбирается соответствующая ячейка блока 3памяти.Содержимое ячейки считывается, но код номера выхода генератора не поступает на входы дешифратора 8, так как в это время коммутатор 7 находится в режиме, при котором выходы в блоке 3 памяти отключены от входов5 1 О 15 20 25 30 35 40 45 50 55 дешифратора 8, В каждом такте изменяется состояние счетчика 12 адреса и из блока 13 памяти выбирается по адресу соответствующая ячейка. Старшие разряды (выходы 16) поступают на входы коммутатора 7, младшие разряды (выходы 18) на входы дешифратора 19 признаков. Сигнал с дешифратора 19 признаков поступает в блок 5, где формируется сигнал заданного типа, который по выходу 1 О поступает на информационные входы выходного регистра 9.Если код признака определяет, что должен быть сФормирован сигнал, то коммутатор 7 подключает выходы 6 бло. ка 3 памяти к входам дешифиатора 8 и код номера выхода поступает на входы дешифратора 8, При этом на тактовом входе соответствующего разряда выходного регистра 9 появляется сигнал логической единицы и этот разряд изменяет свое состояние в соответствии с сигналом, поступившим из блока 5.Если код признака псевдоциклического кода, то выход 23 дешифратора 19 признака отключает выходы 16 блока 13 памяти ат коммутатораи подключает к нему выход в блоке 3 памяти. Код вероятности по выходам 4 поступает в блок 5, который формирует единичный сигнал с этой вероятностью, Сигнал по выходу 10 поступает на информационные входы выходного регистра 9. Код номера выхода, считанный уже к этому времени из ячейки блока 3 памяти, дешифруется дешифратором 8, на тактовом входе выбранного разряда выходного регистра 9 появляется сигнал логической единицы и выход этого разряда выходного регистра 9 изменяет свое состояние в соответствии с сигналом, поступившим из блока 5.Если необходимо участок последовательности выполнять в циклическом режиме, то последнее слово этой последовательности содержит в соответствующем разряде (выход 36) логическую единицу, что позволяет при первом проходе участка последовательности записать в блок 20 формирования циклов с выходов 18 и 21 слово, содержащее число циклов выполнения участка последовательности, Блок 20 Формирования циклов через выход 31 ,выдает сигнал логического нуля на вход элемента И 32 и через элемент И 32 - на вход выбора режима счетчика 12 адреса, и с выходов 16 записывается адрес ячейки начала, повторяющейся определенное количество циклов последовательности. Количество отработанных циклов определяется блоком 20 формирования циклов.Так как для записи слова количества циклов в блок 20 формирования циклов используются выходы 18 и выходы 21, подключенные к адресным входам мультиплексора 15, то в это время невозможна работа мультиплексора 15 и, следовательно, выдача синхросигнала с выхода 45 блока 13 памяти. Дешифратор 8 отключается в этот момент сигналом на выходе 37 блока 13 памяти, а коммутатор 17 - сигналом на выходе 35 блока 13 памяти.При выполнении условного перехода на определенный участок последовательности сигналы на выходах 21 блока 13 памяти подключают необходимый вход из группы входов 14 к Э-входу триггера 22 условия. Выход 30 блока 13 памяти осуществляет синхронизацию записи триггера 22 условия. При выдаче генератором детерминированного слова на выходной регистр 34 выдается записанное в блоке 13 памяти слово. При этом коммутатор 17 по управляющему сигналу на выходе 35 подключает группы выходов 18, 16 и 21 к входам выходного регистра 34, а по сигналу на выходе 41 слово записывается в выходной регистр 34. При необходимости записи в выходной регистр 34 псевдослучайного слова по управ-. ляющему сигналу на выходе 35 блока 13 памяти коммутатор 17 подключает группы выходов 11 и 2 блока 1 к входам выходного регистра 34. Таким образом, можно за один такт работы полностью менять содержимое регистра 34. Сигнал на выходе 37 блока 13 памяти управляет выдачей слова с выходных регистров 9 и, 34. Выход 44 блока 13 памяти осуществляет синхронизацию сдвига информа" ции выходного регистра 34. Это позволяет формировать такую последовательность двухразрядных двоичных чисел (2 .разряда выбираются из п произвольного),в которой имеет место следующее свойство: в любой двухразрядной двоичной последовательности встре 354401чаются всевозможные пары следующих друг за другом двухразрядных двоичных чисел и в-разрядных в 1 оц щ наборов для ш разрядов, расположенных подряд.Формула изобретения1.Генератор псевдослучайных испытательных последовательностей по авт.св. Р 1226621, о т л и ч а ю - щ и й с я тем, что с целью расширения функциональных возможностей, в него дополнительно введены второй коммутатор,. второй выходной регистр, четыре элемента И, триггер условия, элемент ИЛИ, блок формирования циклов, мультиплексор логических условий, входы данных которого являются входной шиной логических условий, а выход мультиплексора логических условий подключен к информационному входу триггера условия, инверсный выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с первым выходом второго блока памяти, второй выход которого подключен к синхровходу триггера условия, третий выход второго блока памяти соединен с первым вхоцом блока формирования циклов, выход которого связан с первым входом перво;го элемента И, второй вход которого подключен к выходу элемента ИЛИ, а выход первого элемента И соединен с управляющим входом счетчика адреса, тактирующий вход счетчика адреса соединен с вторым выходом блока управления, второй вход которого связан с.входом установки второго выходного регистра и с вторым входом блока формирования циклов, вторая груп-. па входов которого подключена к четвертой группе выходов второго блока памяти, к адресным входам мультиплексора условий и к первой группе вхо-, дов второго коммутатора, вторая группа входов которого подключена к информационным входам счетчика адреса и к пятой группе выходов второго блока памяти, выходы второго коммутатора соединены с входами второго выходного регистра, инверсный управляющий вход которого связан с прямым управляющим входом первого выход,ного регистра, с первым входом второго элемента И, с шестым выходом45 50 55 ляется выходом блока, информационные 5 10 15 20 30 второго блока памяти, седьмой выходкоторого соединен с управляющим входом второго коммутатора, третья груп.па входов которого связана с первойгруппой выходов блока формированияравномерно распределенных псевдослучайных чисел, вторая группа выходовкоторого соединена с четвертойгруппой входов второго коммутатора,третий выход блока управления соединен с первыми входами третьего, четвертого элементов И и вторым входомвторого элемента И, выход которогосоединен с управляющим входом дешифратора номера выходов, восьмая группа выхоцов второго блока памяти соединена с пятой группой входов второго коммутатора и четвертой группойвходов блока формирования циклов девятый выход второго блока памяти соединен с вторым входом третьего элемента И, выход которого соецинен спервым тактовым входом второго выходного регистра, десятый выход второгоблока памяти соединен с вторым входом четвертого элемента И, выход которого соединен с вторым тактовымвходом второго выходного регистра,выход младшего разряда которого соединен со сдвиговым информационнымвходом этого регистра. 2.Генератор по п.1, о т л и ч а ю -щ и й с я тем, что блок формирования циклов содержит счетчик, элемент ИЛИ, триггер, элемент И-НЕ, два элемента И, причем выходы счетчика че- рез элемент ИЛИ соединены с первыми входами первого и первым инверснымвходом второго элементов И, вторыевходы которых объединены с первымвходом элемента И-НЕ и являются первым входом блока, выход первого элемента И соединен с синхровходомтриггера и входом записи счетчика, тактовый вход которого соединен с выходом второго элемента И, входы установки счетчика и триггера объединены и являются вторым входом блока, на информационный вход триггера подан потенциал логической единицы, выход триггера соединен с.вторым входом элемента И-НЕ, выход которого яввходы счетчика являются третьей и четвертой входными шинами бло- ка.и д. 4 а изводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 18 21 оставитель Ю.Сибирякехред А.Кравчук Корректор О.Кравцова 54 Тираж 900 П ВНИИПИ Государственного комитепо делам изобретений и откры113035, Москва, Ж, Раушская

СмотретьЗаявка

4006171, 13.01.1986

КИЕВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

РОМАНКЕВИЧ АЛЕКСЕЙ МИХАЙЛОВИЧ, ВИЛИНСКИЙ ЮРИЙ САВЕЛЬЕВИЧ, ГРОЛЬ ВЛАДИМИР ВАСИЛЬЕВИЧ, РУБАНИК СЕРГЕЙ МИХАЙЛОВИЧ, НАКОНЕЧНЫЙ АЛЕКСАНДР АНАТОЛЬЕВИЧ, РАВНЯГО СЕРГЕЙ КОНСТАНТИНОВИЧ

МПК / Метки

МПК: H03K 3/84

Метки: генератор, испытательных, последовательностей, псевдослучайных«

Опубликовано: 23.11.1987

Код ссылки

<a href="https://patents.su/7-1354401-generator-psevdosluchajjnykh-ispytatelnykh-posledovatelnostejj.html" target="_blank" rel="follow" title="База патентов СССР">Генератор псевдослучайных испытательных последовательностей</a>

Предыдущий патент: Устройство для зарядки накопительного конденсатора

Следующий патент: Генератор напряжения треугольной формы

Случайный патент: Устройство для слива и транспортировки расплава хлористого магния