Вычислительное устройство и запоминающий масштабно суммирующий блок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1043670

Авторы: Заподовников, Самокиш

Текст

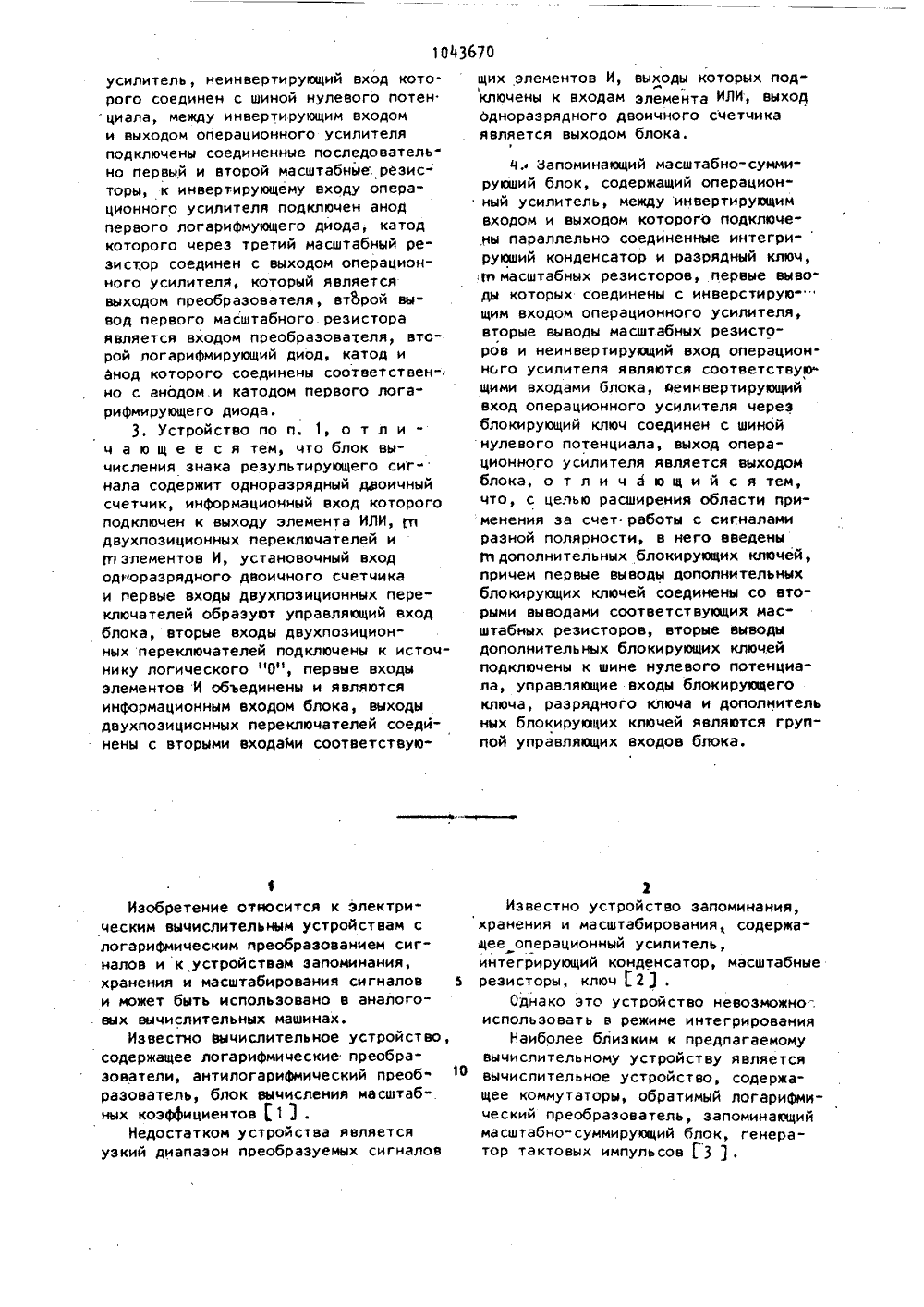

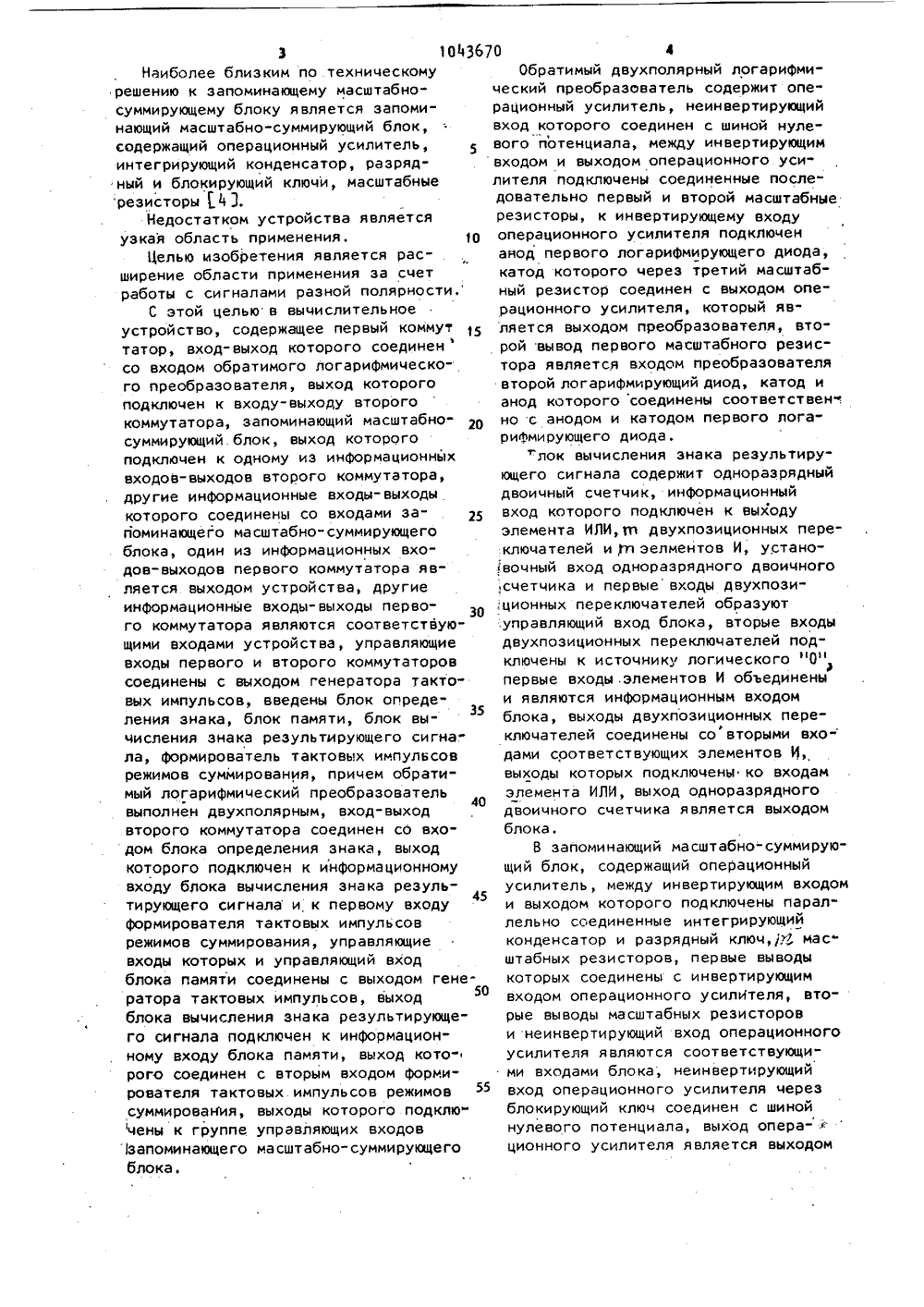

(21) 2988100 (22) 02,)0.8 (46) 23.09.8 (72) В,В. Са 18-2 Бюл. У 35иш и К,И. Заподовн в Й ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ ОПИСАНИЕ ИЗО К АВТОРСКОМУ СВИДЕТЕЛЬ(71) Томский ордена ОктябрьскойРеволюции и ордена Трудового Красного Знамени политехнический институтим. С,М. Кирова(56 ) 1. Авторское свйдетельство СССРйф 650082, кл. 6 06 6 7/24, 19772. Шило В,Л. Линейные интегральные схемы в радиоэлектронной аппара"туре. И., "Советское радио", 1979,рис, 8, 153. Авторское свидетельство СССРпо заявке й 2696346/24,кл. 6 06 6 7/24 1978 (прототип ),4. Авторское свидетельство СССРИ 387383, кл. 6 06 6 7/18, 1971(54 ) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ИЗАПОМИНАЮЩИЙ МАСШТАБНО-СУИИИРУЮЩИБЛОК( 57 ) 1. Вычислительное устройство, , содержащее первый коммутатор, вход- выход которого соединен с входом обратимого логарифмического преобразо. вателя, выход которого подключен к входу-выходу второго коммутатора, запоминающий масштабно-суммирующий блок, выход которого подключен к одному из информационных входов-выходов второго коммутатора, другие информационные входы-выходы которого соединены с входами запоминающего масштабно-суммирующего блока, один иэ информационных входов-выходов пер 43670 А вого коммутатора является выходомустройства, другие информационныевходы-выходы коммутатора являютсясоответствующими входами устройства, управляющие входы первого и второго коммутаторов соединены с выходом генератора тактовых импульсов,о т л и ч а ю щ е е с я тем, что, сцелью расширения области примененияза счет работы с сигналами разнойполярности, в него введены блок определения знака, блок памяти, блок вычисления знака результирующего сигнала, формирователь тактовых импуль-.сов режимов суммирования, причемобратимый логарифмический преобразователь выполнен двухполярным, входвыход второго коммутатора соединенс входом блока определения знака,выход которого подключен к информационному входу блока вычисления знака результирующего сигнала .и к первому входу формирователя тактовыхимпульсов режимов суммирования, управляющие йходц которых и управляющийвход блока памяти соединены с выходом генератора тактовых импульсов,.выход блока вычисления знака результируюшего сигнала подключен к информационному входу блока памяти, выходкоторого соединен с вторым входомформирователя тактовых импульсоврежимов суммирования, выходы которого подключены к группе .управляющихвходов запоминающего масштабно-суммирующего блока,2, Устройство по и. 1, о т л ич а ю щ е е с я тем, что обратимыйдвухполярный логарифмический пре.- образователь содержит операционный103670 усилитель, неинвертирующий вход кото. рого соединен с шиной нулевого потен циала, между инвертирующим входом и выходом операционного усилителя подключены соединенные последовательно первый и второй масштабнйе. резисторы к инвертирующему входу операционного усилителя подключен анод первого логарифмующего диода, катод которого через третий масштабный резистор соединен с выходом операционного усилителя, который является выходом преобразователя, второй вывод первого масштабного резистора является входом преобразователя, второй логарифмирующий диод, катод и анод которого соединены соответственно с анодом и катодом первого логарифмирующего диода.3. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок вычисления знака результирующего сиг" нала содержит одноразрядный двоичный счетчик, информационный вход которого подключен к выходу элемента ИЛИ, р двухпозиционных переключателей и 1 п элементов И, установочный вход одноразрядного двоичного счетчика и первые входы двухпозиционных пере" ключателей образуют управляющий вход блока, вторые входы двухпозиционных переключателей подключены к источнику логического "0", первые входы элементов И объединены и являются информационным входом блока, выходы двухпозиционных переключателей соединены с вторыми входаМи соответствую" 3Изобретение относится к электрическим вычислительным устройствам с логарифмическим преобразованием сигналов и к устройствам запоминания, хранения и масштабирования сигналов ь и может быть использовано в аналого. вых вычислительных машинах.Известно вычислительное устройство, содержащее логарифмические преобразователи, антилогарифмический преобразователь, блок вычисления масштаб-. ных коэффициентов Г 1 3 .Недостатком устройства является узкий диапазон преобразуемых сигналов щих элементов И, выходы которых подключены к входам элемента ИЛИ, выход Одноразрядного двоичного счетчика является выходом блока.1Ч. Запоминающий масштабно-суммирующий блок, содержащий операционный усилитель, между инвертирующим входом и выходом которого подключены параллельно соединенные интегри-рующий конденсатор и разрядный ключ, ,ю масштабных резисторов, первые выводы которых соединены с инверстирую-щим входом операционного усилителя, вторые выводы масштабных резисторов и неинвертирующий вход операционного усилителя являются соответствую щими входами блока, йеинвертирующий вход операционного усилителя через блокирующий ключ соединен с шиной нулевого потенциала, выход операционного усилителя является выходом блока, о т л и ч а ю щ и й с я тем, что, с целью расширения области применения за счет работы с сигналами разной полярности, в него введены Ф дополнительных блокирующих ключей, причем первые выводы дополнительных блокирующих ключей соединены со вторыми выводами соответствующих масштабных резисторов, вторые выводы дополнительных блокирующих ключей подключены к шине нулевого потенциала, управляющие входы блокирующего ключа, разрядного ключа и дополнитель ных блокирующих ключей являются группой управляющих входов блока. 2Известно устройство запоминания,хранения и масштабирования, содержащее операционный усилитель,интегрирующий конденсатор, масштабныерезисторы, ключ2.Однако это устройство невоэможно-.использовать в режиме интегрированияНаиболее близким к предлагаемомувычислительному устройству являетсявычислительное устройство, содержащее коммутаторы, обратимый логарифмический преобразователь запоминающиймасштабно-суммирующий блок, генератор тактовых импульсов Г 33 10436Наиболее близким по техническому решению к запоминающему масштабно- суммирующему блоку является запоминающий масштабно-суммирующий блок, содержащий операционный усилитель, интегрирующий конденсатор, разрядный и блокирующий ключи, масштабные резисторы 4 3.Недостатком устройства является узкая область применения. 1 оЦелью изобретения является рас- . ширение области применения за счет работы с сигналами разной полярности.С этой целью в вычислительное устройство, содержащее первый коммут татор, вход-выход которого соединенсо входом обратимого логарифмического преобразователя, выход которого подключен к входу-выходу второго коммутатора, запоминающий масштабно- суммирующий. блок, выход которого подключен к одному из информационных входов-выходов второго коммутатора, другие информационные входы- выходы которого соединены со входами запоминающего масштабно-суммирующего блока, один из информационных входов-выходов первого коммутатора является выходом устройства, другие информационные входы-выходы перво 30 го коммутатора являются соответствующими входами устройства, управляющие входы первого и второго коммутаторов соединены с выходом генератора тактовых импульсов, введены блок определения знака, блок памяти, блок вычисления знака результирующего сигна.- ла, формирователь тактовых импульсов режимов суммирования, причем обратимый логарифмический преобразователь4 О выполнен двухполярным, вход-выход второго коммутатора соединен со входом блока определения знака, выход которого подключен к информационному входу блока вычисления знака результирующего сигнала и к первому входу45 формирователя та кто вых и мпул ь сов режимов суммирования, управляющие входы которых и управляющий вход блока памяти соединены с выходом генератора тактовых импульсов, выход блока вычисления знака результирующего сигнала подключен к информационному входу блока памяти, выход которого соединен с вторым входом формирователя тактовых. импульсов режимов суммирования, выходы которого подклю" чены к группе управляющих входов запоминающего масштабно-суммирующего блока. 70 4Обратимый двухполярный логарифмический преобразователь содержит операционный усилитель, неинвертирующий вход которого соединен с шиной нулевого потенциала, между инвертирующим входом и выходом операционного усилителя подключены соединенные последовательно первый и второй масштабныерезисторы, к инвертирующему входуоперационного усилителя подключенанод первого логарифмирующего диода,катод которого через третий масштабный резистор соединен с выходом операционного усилителя, который является выходом преобразователя, второй вывод первого масштабного резистора является входом преобразователявторой логарифмирующий диод, катод ианод которого соединены соответствен":но с анодом и катодом первого логарифмирующего диода,лок вычисления знака результирующего сигнала содержит одноразрядныйдвоичный счетчик, информационныйвход которого подключен к выходуэлемента ИЛИ, р двухпозиционных пере.ключателей и,Гп эелментов И, установочный вход одноразрядного двоичногосчетчика и первые входы двухпози;ционных переключателей образуют,управляющий вход блока, вторые входыдвухпозиционных переключателей подключены к источнику логического "0"первые входы .элементов И объединеныи являются информационным входомблока, выходы двухпозиционных переключателей соединены со вторыми вхо-дами соответствующих элементов И,выходы которых подключены ко входамэлемента ИЛИ, выход одноразрядногодвоичного счетчика является выходомблока.8 запоминающий масштабно-суммирующий блок, содержащий операционныйусилитель, между инвертирующим входоми выходом которого подключены параллельно соединенные интегрирующийконденсатор и разрядный ключ,/Я мас"штабных резисторов, первые выводыкоторых соединены с инвертирующимвходом операционного усилйтеля, вторые выводы масштабных резисторови неинвертирующий вход операционногоусилителя являются соответствующими входами блока, неинвертирующийвход операционного усилителя черезблокирующий ключ соединен с шинойнулевого потенциала, выход опера- .ционного усилителя является выходом10435блока, введены М дополнительных блокирующих ключей, причем первые выводы дополнительных блокирующих ключей соединены со вторыми выводами соответствующих масштабных резисторов, вторые выводы дополнитель- . нык блокирующих ключей подключены к шине нулевого потенциала, управляющие входы блокирующего ключа, разряд" ного ключа и дополнительных блокирую О щих ключей являются группой управляющих входов блока.ОНа фиг. 1 изображена функциональная схема логарифмического вычисли тельного устройства 1 на фиг. 2- функциональная схема запоминающего масштабно-суммирующего блокаф, на фиг. 3 - функциональная схема блока вычисления знака результирующего сигнала, на фиг. 4 - функциональная схема обратимого двухполярного лога", рифмического преобразователяф на фиг. 5 - схема формирователя тактовых импульсов режимов суммирования. 25Устройство содержит первый ком,мутатор 1, логарифмический преобразователь 2, второй коммутатор 3,:эапоминаоций масштабно-суммирующийблок 4, блок 5 определения знака,ЗОблок 6 вычисления знака результирующего сигнала, формирователь 7 тактовых импульсов режимов суммирования,блок 8 памяти, генератор 9 тактовыхимпульсов входы 10 , , 1 О 3510 и выход 11 устройства, интегрирую%щий конденсатор 12, разрядный ключ13, операционный усилитель 14,масштабные резисторы 15 151 п,блокирующий ключ 16, дойолнительные 4 Облокирующие ключи 17 , . 17шину 18 нулевого потенциала, входы19.1 19, 19 п 1+1, управляющиевходы 20 и выход 21 запоминающегомасштабно-суммирующего блока, элемент 45ИЛИ 22, одноразрядный двоичный счетчик 23, двухпозиционные переключатели24 , 24 .24, элементы И1ф26 сигнала логического "0", первый 5027 и второй 28 входы блока 29 вычисления знака результирующего сигнала,операционный усилитель 30, первый,второй и третий масштабные резисторы31 - 33, логарифмирующий диод 34 55дополнительный логарифмический диод35, вход 36 и выход 37 обратимогодвухполярного логарифмического пре 670 бобраэователя, шину 38 нулевого потенциала.,Формирователь 7 тактовых импульсоврежимов суммирования сожержит первый,второй и третий входы 39 40 и 41,многовходовой элемент И-НЕ 42, двухпозиционные переключатели 4343 инверторы 44-47, элементы И 48.56, выходы 57 57,+.Вычислительное устройство работаетпо логарифмическому алгоритму6М:сп 11 Ро.п; 6 о х, (1 );агде Х; - входные сигналы;й- показатель степени.При работе устройство моделируетвыражение видайз=П к , 12):1Входные сигналы через первый коммутатор 1 поочередно, по тактам; задаваемым генератором 9 тактовых импульсов, поступают на логарифмическийпреобразователь 2. Логарифмы входныхсигналов через второй коммутатор3 поступают на запоминающий масштабно-суммирующий блок 4. Блок 5 определения знака в каждый такт логарифмирования входных сигналов определяетих полярность. Блок 6 вычислениязнака результирующего сигналапо выходным сигналам блока 5 определения знака, а также в соответствиис видом реализуемого выражения (.2 )с учетом знака показателя степениэтого сигнала, к концу каждого циклаработы определяет знак результирующего сигнала, информацию о которомзапоминает на время следующего цикла блок 8 памяти.формирователь 7 тактовых импульсоврежимов суммирования в каждый тактлогарифмирования какого-либо из входных сигналов в соответствии со знаком показателя степени, с каким этотсигнал входит в выражение2 ), сполярностью этого сигнала и знакомрезультирующего сигнала, определеннымв предшествующий цикл работы, определяет режим суммирования логарифмавходного сигнала в запоминающеммасштабно-суммирующем блоке 4, т.е.полярность, с которой он вводится влинейную комбинацию логарифмов входных сигналов.В п 1 + 1 такт цикла работы производится операция потенцирования сум7 1043610 8мы логарифмов входных сигналов, знак формирователь тактовых. импульсов которой сооответствует знаку результа режимов суммирования является логитае ческим автоматом, работа которогоВыходной сигнал запоминающего мас- сведена в таблицу.штабно-суммирующего блока 4 через :По сравнению с известным предлагавторой коммутатор 3 поступает.на ло" емое логарифмическое вычислительное гврифмический преобразователь 2, ра" устройство обладает новым качеством ботающий в этом режиме на потенциро- так как оно работает с сигналами ванне, любой полярности, причем достижениюПЬи этом на выходе первого коммута 1 О этого эффекта способствует и технитораформируется результат преобра ,ческое решение запоминающего масштабэования. носуммирующего блока. Знак Режим работы мас- штабно- суммирующего блока Знаквходногосигнала Знакпоказателястеперезультата ни 1 О 1 О О 1 0 1 ФИИПИ пиен филиал ППП "Патент", г. Ужгород, ул, Проектная,

СмотретьЗаявка

2988100, 02.10.1980

ТОМСКИЙ ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ И ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. С. М. КИРОВА

САМОКИШ ВЯЧЕСЛАВ ВАСИЛЬЕВИЧ, ЗАПОДОВНИКОВ КОНСТАНТИН ИВАНОВИЧ

МПК / Метки

МПК: G06G 7/12

Метки: блок, вычислительное, запоминающий, масштабно, суммирующий

Опубликовано: 23.09.1983

Код ссылки

<a href="https://patents.su/7-1043670-vychislitelnoe-ustrojjstvo-i-zapominayushhijj-masshtabno-summiruyushhijj-blok.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительное устройство и запоминающий масштабно суммирующий блок</a>

Предыдущий патент: Пневматический аналого-цифровой преобразователь

Следующий патент: Устройство для масштабного преобразования дифференциальных сигналов

Случайный патент: Способ получения элементарной серы