Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1008742

Авторы: Кондратьев, Тимонькин, Ткачев, Ткаченко, Харченко

Текст

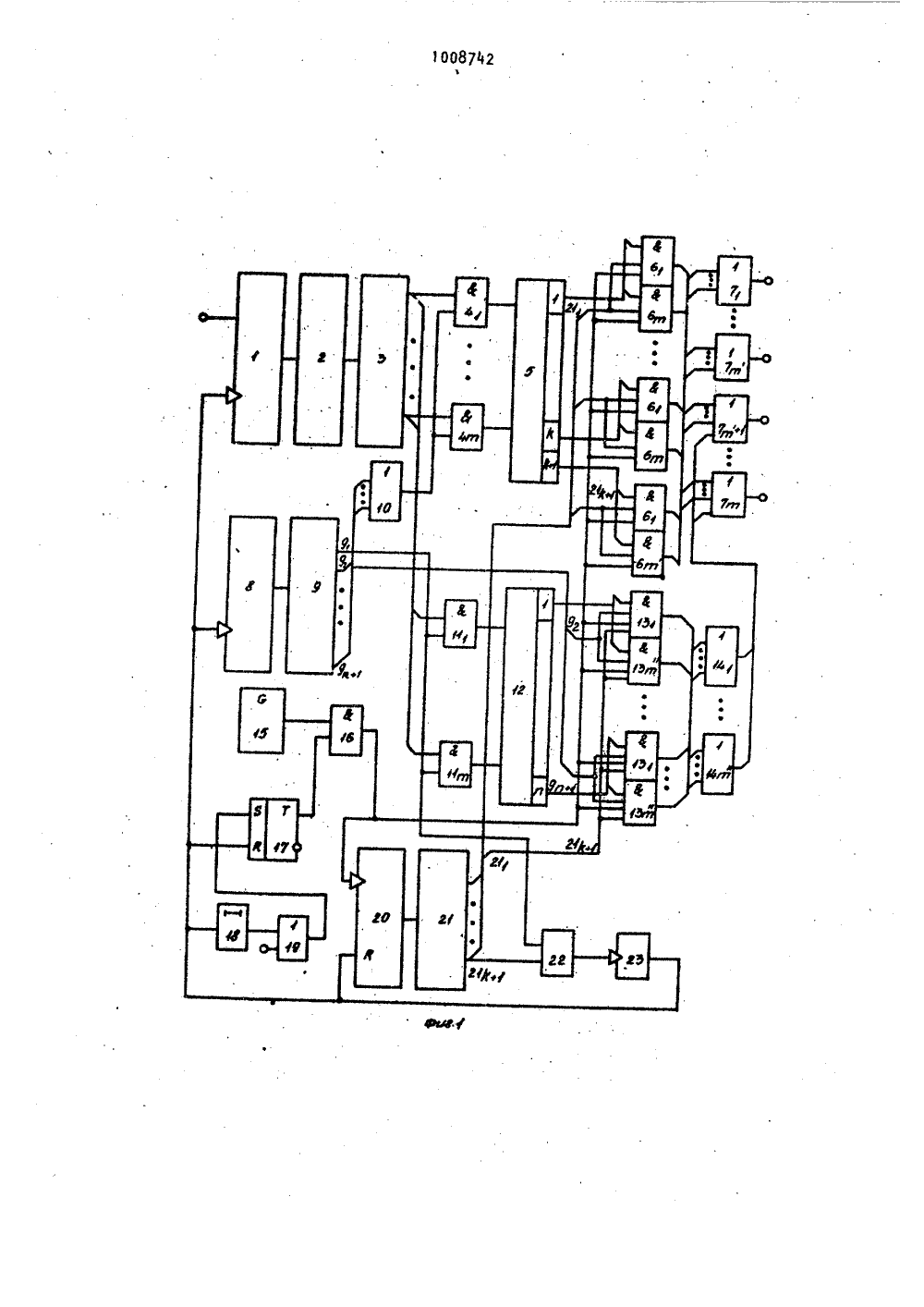

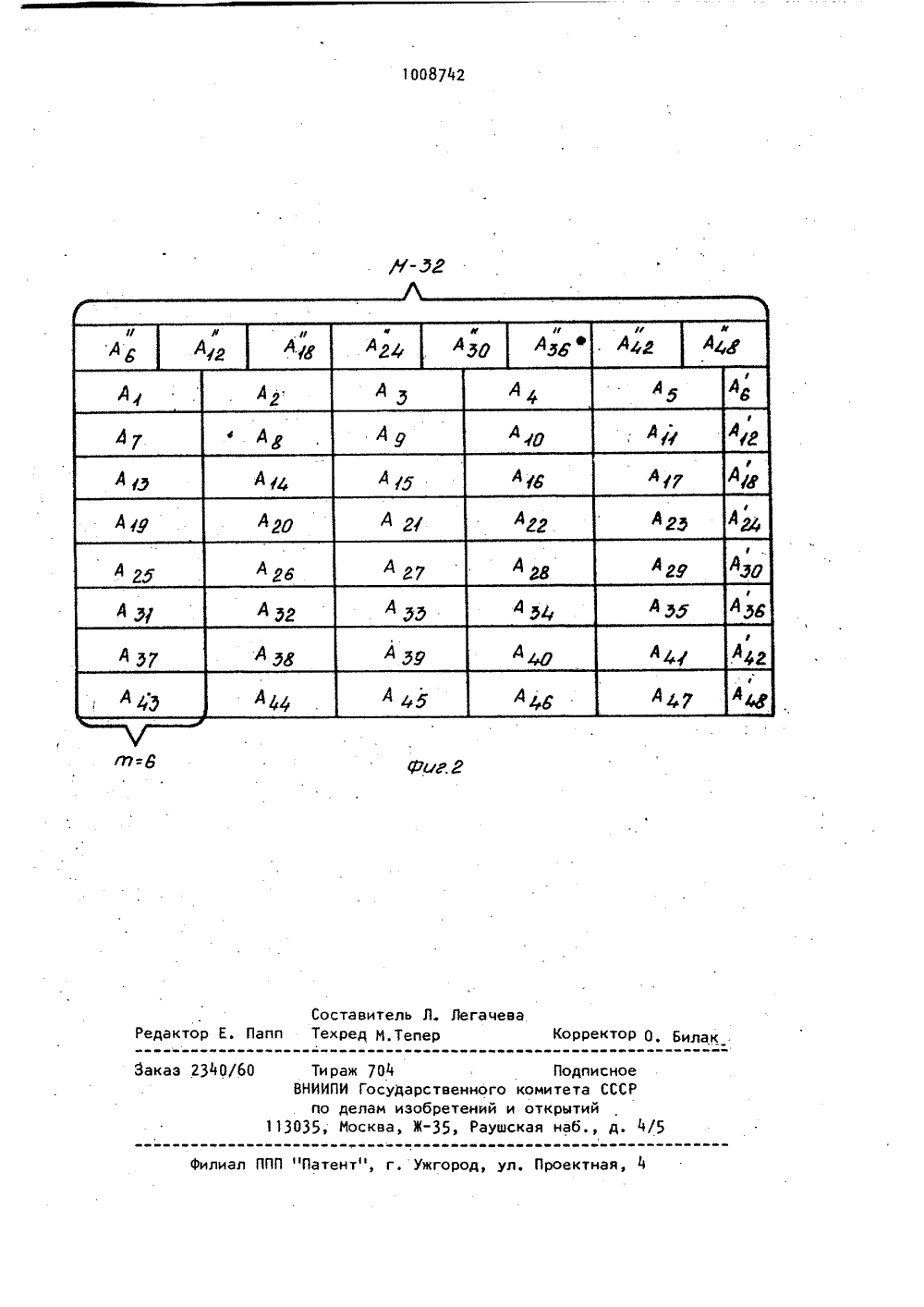

,5 с 0 ИЗ ЕТЕНИЯ ПИ ВИДЕТЕЛЬСТВ АВТОРСН г енко,лем и с ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОЧЯРЫТИЙ"Статистика", 1979, с. 13.2. Авторское свидетельство СССРпо заявке. У 2961311/18-21,(54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВОУПРАВЛЕНИЯ, содержащее буферный регистр, первый счетчик, установочныйвход которого подключен к адресномувходу устройства, и выход соединенс входом первого дешифратора, выходкоторого соединен с адресным входомблока памяти, выходы которого соеди нены с первыми входами элементов Ипервой группы, выходы которых соединены с входами регистра микрокоманд,каждая группа выходов которого соединена соответственно с первыми входами элементов И 2 - (1+2)-й групп(К - число целых микрокоманд), вторые входы которых соединены с соответствующим выходом второго дешифратора, выходы соединены через первуюгруппу элементов ИЛИ с выходами устройства, а третьи входы с выходомэлемента И и через счетный вход второго счетчика с входом второго дешифратора, первый вход элемента Исоединен с выходом генератора тактовых импульсов, а второй вход с единичным выходом триггера, нулевой вход инен с выходом перво опервый вход которогоправляющему входу уст"орой вход соединен снта задержки, выход втоИЛИ соединен с входомвыход которого соедими входами первого ичиков, выход третьегодинен с входом третьегокаждая группа выходовистра соединена соотпервыми входами элемен+и+2)-й групп ( исодержащих целое число(К+и+3)-ю группу элерую группу элементовч а ю щ е е с я тем,сокращения оборудованиясодержит третий элеод которого соединен сми элементов И первойды соединены с 2 -ами третьего дешифратоход которого соединенвходы элементов Иппы с входами буферногорые входы этих элеменс выходами блока памятиретьего дешифраторарвым входом второго алерой вход которого соем выходом второго деорыми входами элементов+1)-ми входами 5 м+1)ИЛИ первой группы,ентов И %+3)оединены с выходом котооого соедэлемента ИЛИ,подключен к уройства, а втвыходом элемерого элементаодновибратора,нен со счетнытретьего счетсчетчика соедешифратора,буферного регветственно стов И +3)число линеек,микрокоманд),ментов И, втоИЛИ, о т л ичтб, с цельюдополнительномент ИЛИ, выхвторыми входагруппы, а вхо(й+1) -м выходра, первый вычерез первые(+и+3)-й грурегистра, втотов соединеныпервый выход тсоединен с пемента ИЛИ, втодинен с (1+1)шифратора и втИ +3) - (К+иторых соединенгруппы элементсоединены с (41 Гми элементовтретьи входы ээлемента И, а четвертые входы - с2 - (и+1)-м выходами третьего дешифратора, выход одновибратора соединен 1008742с входами установки в нуль второгосчетчика и триггера и .входом элементазадержки.1Изобретение относится к вычислительной технике и может быть использовано при синтезе устройств управле ния микропрограммных ЭВИ и других систем. 5Известно микропрограммное устройство управления, содержащее запоминают щий блок, два счетчика, два Яешифратора, регистр микрокоманд, генератор импульсов, элементы И и ИЛИ 1. .10 15 Недостатком данного устройства является низкая экономичность запоминающего блока, обусловленная тем, что в линейке запоминающего блока может храниться только целое число микрокоманд.Наиболее близким по техницеской сущности и достигаемому положительному эффекту к предлагаемому является 2 о устройство, содержащее буферный регистр, первый счетчик, первый вход которого является первым входом уст ройства, а выход соединен с входом первого дешифратора, выход. которого 25 соединен с входом блока памяти, выходы которого соединены с первыми входами первой группы элементов И, выходы которой соединеНы с входами регистра микрокоманд, каждая группа Зо выходов которого соединена с первыми входами элементов И соответствующей группы 2 - 5+2)-й групп элементов И, вторые входы элементов И ,которых соединены с одним из выходов второго дешифратора, выходы соединены через первую группу элементов ИЛИ с выходами устройства, а третьи входы - с выходом элемента И, а через счетный вход второго счетчика с входом второго дешифратора, первый вход элемента И соединен с выходом генератора, а второй вход с единичным выходом триггера, нулевой вход которого соединен с выходом пер. вого элемента ИЛИ, первый вход которого является вторым входом устройства, а второй вход соединен с выходом элемента задержки, выход второго элемента ИЛИ соединен с входом одно" 2вибратора, выход которого соединен с счетными входами первого и третьего счетчиков, выход третьего счетчика соединен с входом третьего дешифратора, каждая группа выходов буферного регистра соединена с первым входом элемента И соответствующей группы (1+3) - (К+й+2)-й групп элементов И, (1+и+3) "ю группу элементов И, вторую группу элементов ИЛИ 12 1,Недостатками данного устройства являются низкая экономичность и низкая универсальность. Низкая экономичность. обусловлена тем, что используются не все свободные ячейки памяти в линейке блока памяти. В зависимости от разрядности микрокоманды и разрядности линейки блока памяти может возникнуть три варианта упаковки информации в блоке памяти.1-й вариант. Если разрядность линейки блока памяти равна целому числу Форматов. микрокоманд, то все яцейки блока памяти заполнены информацией.2-й вариант. Если разрядность линейки блока памяти равна не целому числу форматов микрокоманд и число свободных ячеек меньше, чем половина формата микрокоманды, то устройство позволяет полностью заполнить все ячейки блока памяти информацией.3-й вариант. Часто встречается случай, когда формат линейки блока памяти равен нецелому числу Форматов микрокоманд и число свободных ячеек больше половины длины микрокомандыТогда в данном устройстве информация записывается в те ячейки, в которые помещвется целое число микрокоманд и часть микрокоманд, меньшая, чем половина ее длины. Остальные ячейки блока памяти остаются свободными, незаполненными информацией и используются неэффективно.Цель изобретения - сокращение оборудования.Поставленная цель достигается .тем, что устройство, содержащее буферный регистр, первый счетчик, установоч3 10 ный вход которого подключен к адресному входу устройства, а выход соединен с входом первого дешифратора, выход которого соединен с адресным входом блока памяти, выходы которого соединены с первыми входами элементов И первой группы, выходы которых соединены с входами регистра микро- команд, каждая группа выходов которого соединена соответственно с первыми входами элемента И 2 - (1+2)-й группы ( - число целых микрокоманд) вторые входы которых соединены с соответствующим выходом второго дешифратора, выходы соединены через первую группу элементов ИЛИ с выходами устройства, а третьи входы с выходом элемента И и через счетный вход второго счетчика. с входом второго дешифратора, первый вход элемента И соединен с выходом генератора тактовых импульсов, а второй вход с единичным выходом триггера, нулевой вход которого соединен с выходом первого элемента ИЛИ, первый вход которого подключен к управляющему входу устройства, а второй вход соединен с выхо дом элемента задержки, выхоД второго элемента ИЛИ соединен с входом одновибратора, выход которого соединен со счетными входами первого и третьего счетчиков, выход третьего счетчика соединен с входом третьего дешифратора, каждая группа выходов буферного регистра соединена соответственно с первыми входами элементов И (1+3) -(К+И+2)-й групп ( очисло. линеек, содержащих целое числомикрокоманд), (К+и+3)-ю группу эле-.ментов, И, вторую группу элементов ИЛИ, дополнительно содержит третий элемент МЯИ, выход которого соединен с вторыми входами элементов И первой группы, а входы соединены с 2 - (й+1)-м выходами третьего дешифратора, первый выход которого соединен через первые входы элементов И (+й+3)-й группы с входами буферного регистра, вторые входы этих элементов соединены с выходами блока памяти, первый выход третьего дешифратора соединен с первым входом .второго элемента ИЛИ, второй вход которого соединен с ф+1)-м выходом второго .дешифратора и вторыми входами эле" ментов И (Х+3) - +8+2)-й групп, выходы которых соединены с входами второй группы элементов ИЛИ, выходы которых соединены с (1(+1)-ми входами(и+1) -щ-ми элементов ИЛИпервой группы, третьи входы элементов И .(1+3) - (%+и+2)-й групп соединены свыходом элемента И, а четвертые входы - с 2 - (8+1)-ми выходами третьего дешифратора, выход одновибратора сов" динен с входами установки в нуль второго счетчика и триггера и входом элемента- задержки.Сущность изобретения состоит в по-: вышении экономичности и универСальности путем записи частей микрокоманд, не поместившихся в линейку блока памяти, в отдельн.ю линейку - линейку остатков.%10115 бираются элементом ИЛИ 10, разрешает передачу микрокоманд из блока 3 памя. ти в регистр 5.В регистре 5 хранятся считываемые микрокоманды. Группы элементов И 6 служат для поочередного считывания микрокоманд из регистра 5, а группа элементов ИЛИ 7 - для вывода микро- команд на выходы устройства, Счетчик 8 и дешифратор 9. управляют заНа фиг. 1 изображена функциональ"ная схема предлагаемого микропрограммного устройства; на фиг. 2 - вариантупаковки информации в блоке памятипредлагаемого микропрограммного устройства при Ма 32, щ = б.Предлагаемое устройство (фиг. 1). - содержит первый счетчик 1; первый дешифратор 2, блок 3 памяти, первуюгруппу элементов И 4, регистр 5 микрокоманд, 2 - (+2)-ю группы элементов И 6, первую группу элементовИЛИ 7, третий счетчик 8, третий дешифратор 9, третий элемент ИЛИ 10,(В+и+3)-ю группу элементов И 11буферный регистр 12 (+3) - (2+8+2)- группу элементов И 13, вторую группуэлементов ИЛИ 1 М, генератор 15 такто- вых импульсов, элемент И 1 б, триггер17, элемент 18 задержки, первый элемент ИЛИ 19, второй счетчик 20, вто" .рой дешифратор 21, второйэлементИЛИ 22, одновибратор 23.На Фиг. 2 приняты следующие обо-.- 40значения: А; -. -я микрокоманда;ВА, А - части -й микрокоманды.Счетчик 1 и дешифратор 2 формируютадрес, по которому в блоке памяти выбирается нужная линейка с иикроко 4 ф мандами.8 блоке памяти 3 хранятся всемик"5 1008писью информации с блока 3 памяти врегистры 5 и 12.Группа элементов И 11 разрешаетзапись частей микрокоманд из блока 3памяти в регистр 12 по сигналу де- йшиФратора 9. Группа элементов И 13служит для поочередного считываниячастей микрокоманд из регистра 12,а группа элементов ИЛИ 14 - для пе-,редачи частей микрокоманд на выходы 0устройства, Генератор 15 формируеттактовые импульсы, которые йри ус 1тановке триггера 17 в "единицу" прс.,ходят через элемент И 16, Счетчик 20и дешифратор 21 управляют поочереднымсчитыванием микрокоманд с регистров5 и 12,Элемент ИЛИ 22 и одновибратор 23формирует импульс, который устанавливает триггер 17 и счетчик 20 в ннулй"Л/увеличивает содержимое счетчиков 1и 8 на единицу и поступает на входэлемента задержки, Элемент 18 задержки задерживает импульс одновибратора23 на время, необходимое для выбора, линейки в блоке 3 памяти и передачуее в регистр 5.Устройство работает следующим об"разом,30Начальный адрес поступает на входустройства. По содержимому счетчика 1дешифратор 2 в блоке 3 памяти выбирает линейку с частями микрокоманд,По содержимому счетчика 8 дешифратор 9 на первом выходе вырабатывает сигнал, который поступает на вторые входы группы элементов И 11. Линейка с частями микрокоманд переписывается из блока 3 памяти черезгруппу элементов И 11 в регистр 12,40Сигнал с первого выхода дешифратора 9поступает на первый вход элементаИЛИ 22. По сигналу с выхода элементаИЛИ 22 одновибратор 23 вырабатываетимпульс, который,увеличивает содержимое счетчиков 1 и 8, а также поступает на вход элемента 18 задержки. По содержимому счетчика 1 дешифратор 2 выбирает следующую линейкус микрокомандами. По содержимому счетфцика 8 дешифратор вырабатывает на одном из выходов (кроме первого) сигнал, который через элемент ИЛИ 10поступает на вторые входы группы элементов И 4. Выбранные микрокомандыпереписываются через группу элементов И 4 с блока 3 памяти в регистр 5.Задержанный импульс с одновибратора 742 6через элемент ИЛИ 19 поступает на единичный вход триггера 17. Триггер 17 переходит в единичное состояние и разрешает прохождение тактовых импульсов с генератора 15 через элемент И 16, Тактовые импульсы поступают на счетный вход счетчика 20 и на третьи входы групп элементов И 6 и 13 По содержимому счетчика 20 дешифратор 21 выбирает поочередно одну из групп элементов И 6. Через элементы И 6 и ИЛИ 7 микрокоманды сцитываются на выходы устройства. По сигналу с (1+1)-го выхода дешифратора 21 через (3+2)-ю гоуппу элементов И 6 и через выбоанную дешифратором 9 группу элементов И 13 и группу элементов ИЛИ 14 части (ф+1)-й микро- команды с регистров 5 и 12 поступают через группу элементов ИЛИ 7 на выходы устройства. Сигнал с (+1)-го выхода дешифратора 21 поступает на второй вход элемента ИЛИ 22. По сигналу с выхода элемента ИЛИ 22 одновибратор 23 вырабатывает импульс, который устанавливает счетчик 20 и триггер 17 в "нуль", увеличивает содержимое счетчиков 1 и 8 на "единицу" и поступает на вход элемента задержки 18. Так как триггер 17 находится в нулевом состоянйи и на его прямом выходе отсутствует сигнал, то тактовые импульсы с генератора 5 не проходят через элемент И 16. По содержимому счетчика 1 дешифратор 2 в блоке 3 памяти выбирает следующую линейку с микро- командами и устройство начинает выдавать микрокоманды на выходе как было описано выше. Так устройство работаег до тех пор, пока не будет считана последняя часть микрокоманды из регистра 12.1Найдем проигрыш в объеме полезной информации, хранимой в блоке памяти прототипа по сравнению с предлагаемым устройством йЬМ= 1- И =Еп,(0Универсальность предлагаемого.микропрограммного устройства определяется ФормулойО: 0+ Рх.При увеличении формата микрокоманды на один разряд (при том же числе микрокоманд в линейке) количество вводимых элементов равнос= 1(+ 1,7 1008 а количество перекоммутируемых элементов определяется формулой5=. ч + (и+ 1) (2 К + 1)Найдем на сколько элементов больше необходимо вводить в прототипе .при з изменении Формата микрокоманды на единицу при неизменном числе микро- командЬд = В,1-с = М + К .+, 2 -- 1= И+ 1 0 так как М;7 О, то ЬоС ОНайдем, на сколько .элементов боль.ше необходимо перекоммутировать впрототипе при тех же условияхЬ = Ь -р,.= (и 1) (И+К+1) + (в+1) (2 Ь.1) - 1 = (им.1) (М-М) 712 8так как М ъК, то ЬМ Ос При М = 32, ич = б, К 5 ЬО Ы.+ ЬЪЯ ) 222 элементов.Сложность логической части предлагаемого устройства по критерию Квайна определяется Формулой5С + ЬМ + И + 1С +,5 М + 1,Найдем выигрыш в затратахоборудования предлагаемого устройства по сравнению с прототипом.Ь 5 = 5 - 5, = С+3 вМ+1 од (1 с+1)фи+ Щ + из,ьфьРо км1008742 ректор ак аэ 2340/60 оППП "Патент Фи С оста в и тель Л. Лега чеведактор Е, Папп Техред И.Тепер Тираж 704НИИПИ Государственного по делам изобретений35, Москва, Ж, Раув Подписнотета СССрытийнаб., д.

СмотретьЗаявка

3292810, 02.06.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, КОНДРАТЬЕВ ИГОРЬ ЕВГЕНЬЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ТКАЧЕВ МИХАИЛ ПАВЛОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.03.1983

Код ссылки

<a href="https://patents.su/7-1008742-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное вычислительное устройство

Следующий патент: Устройство для обслуживания запросов в порядке поступления

Случайный патент: Бурильная установка