Микропрограммное вычислительное устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

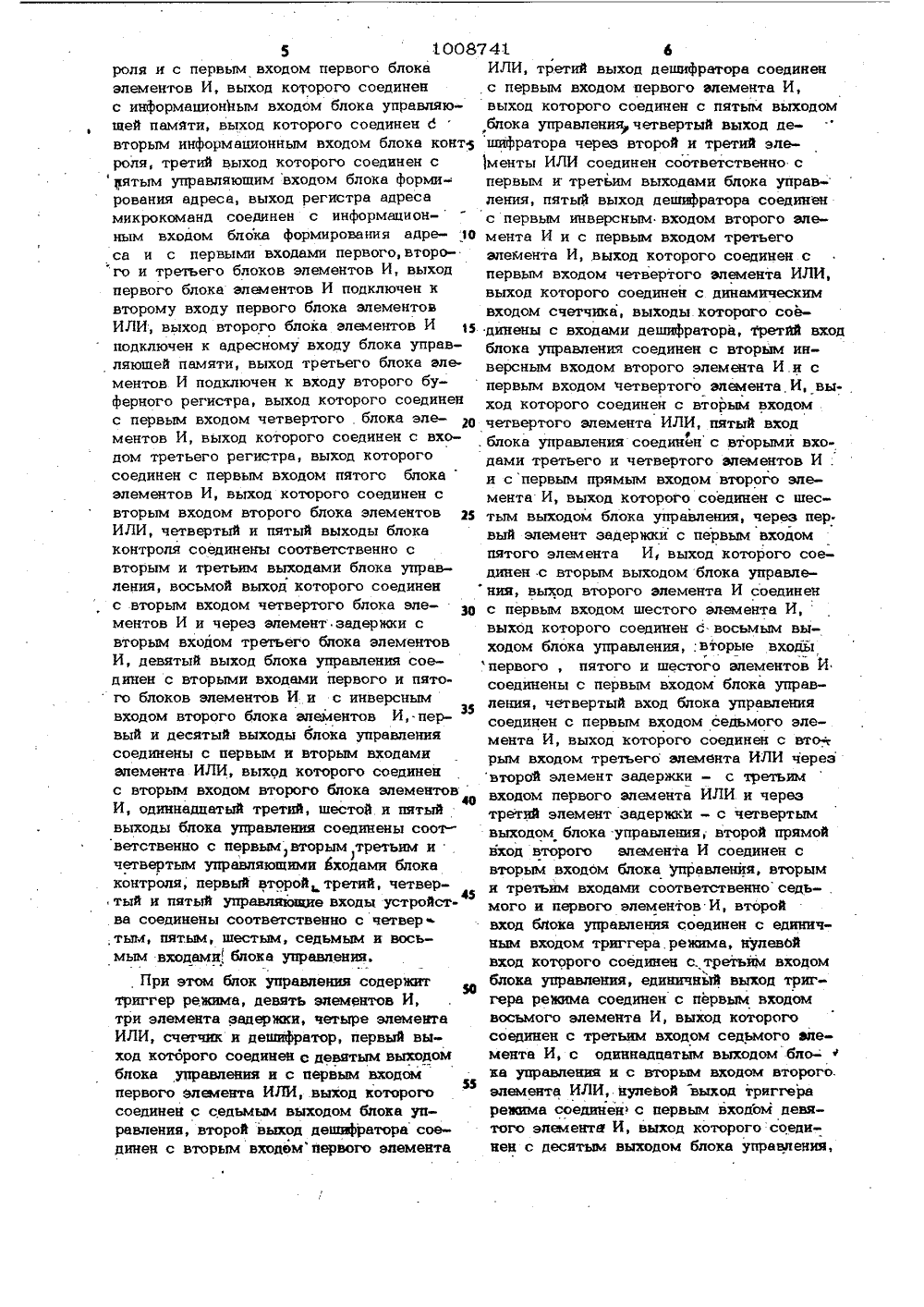

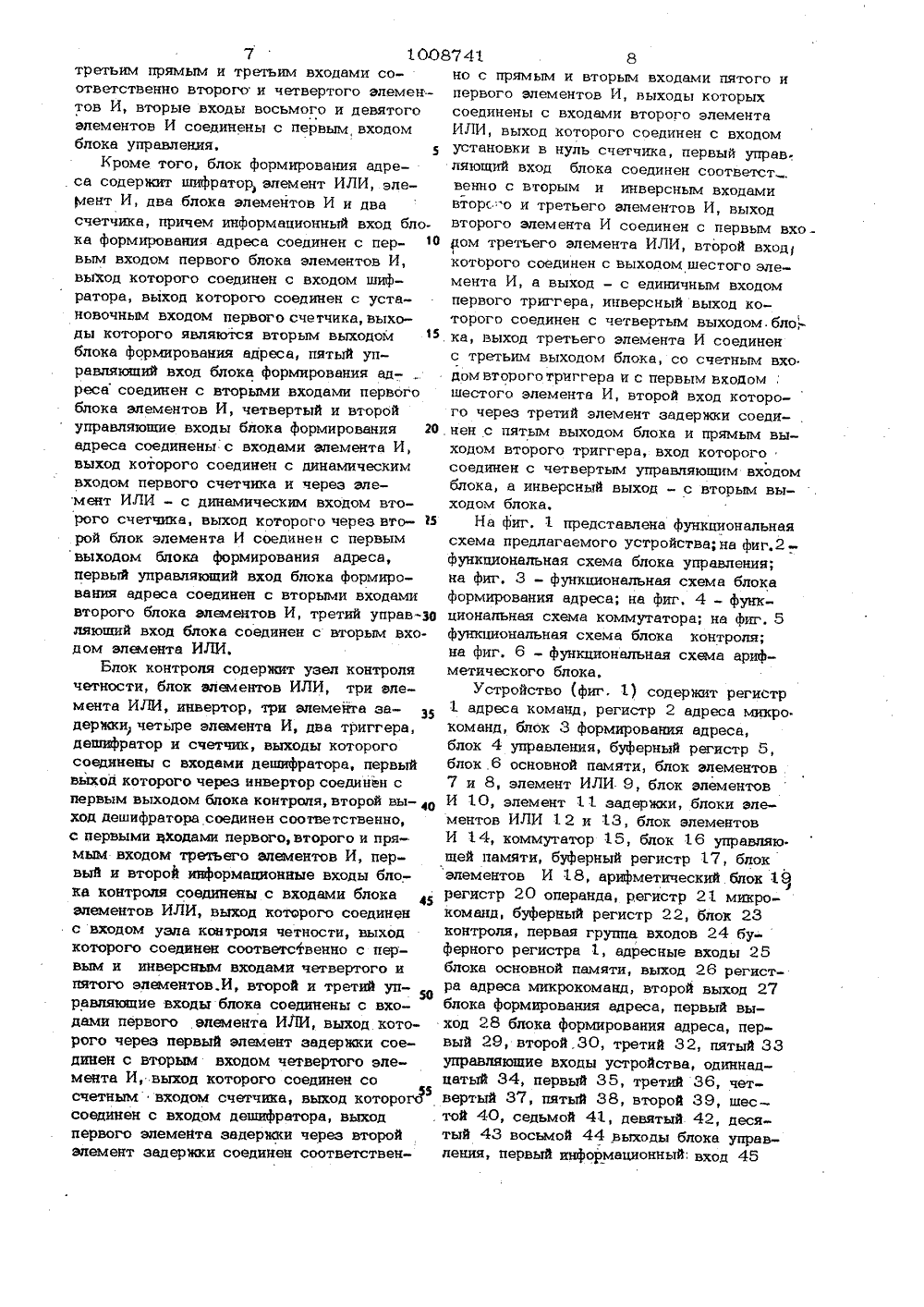

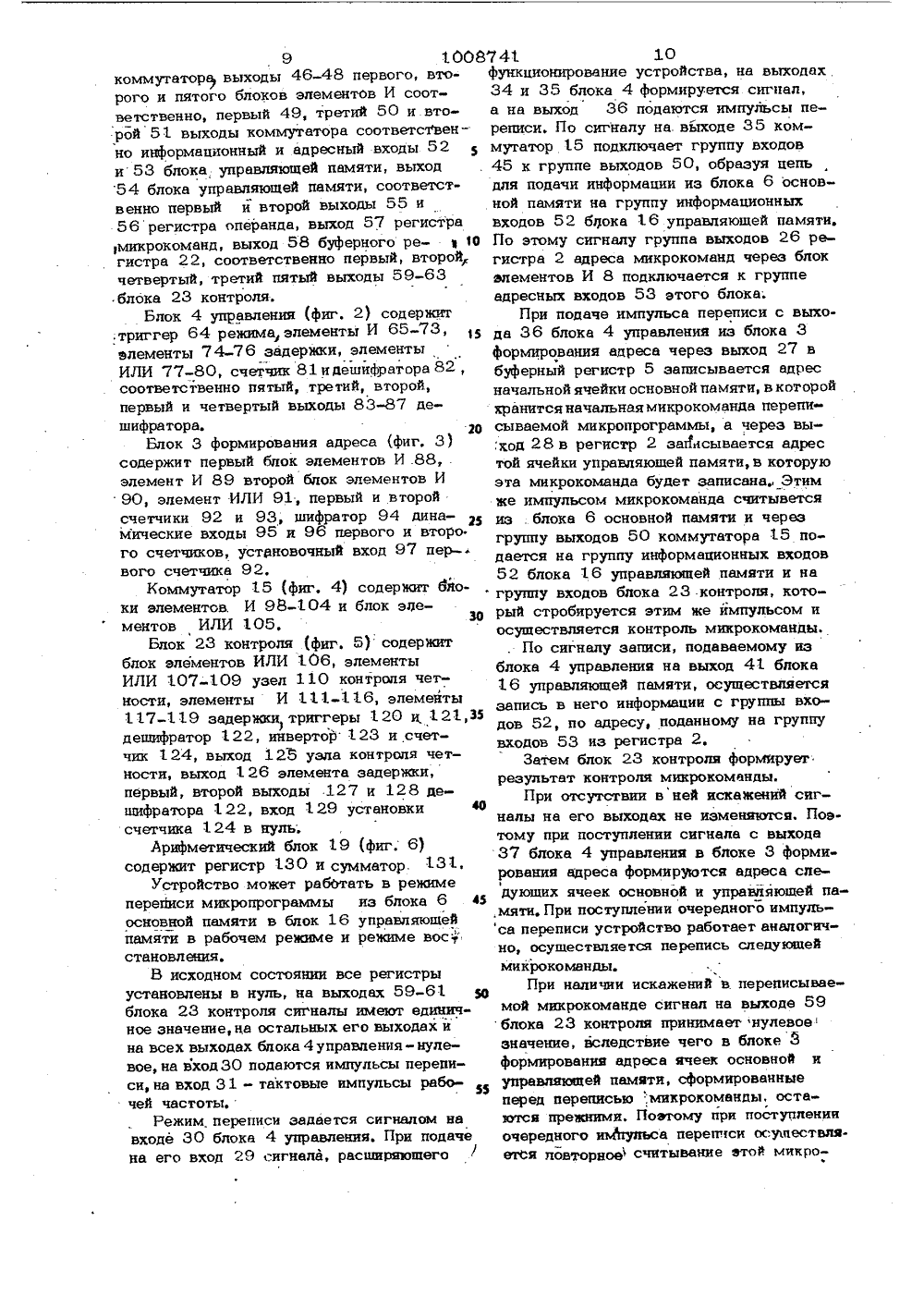

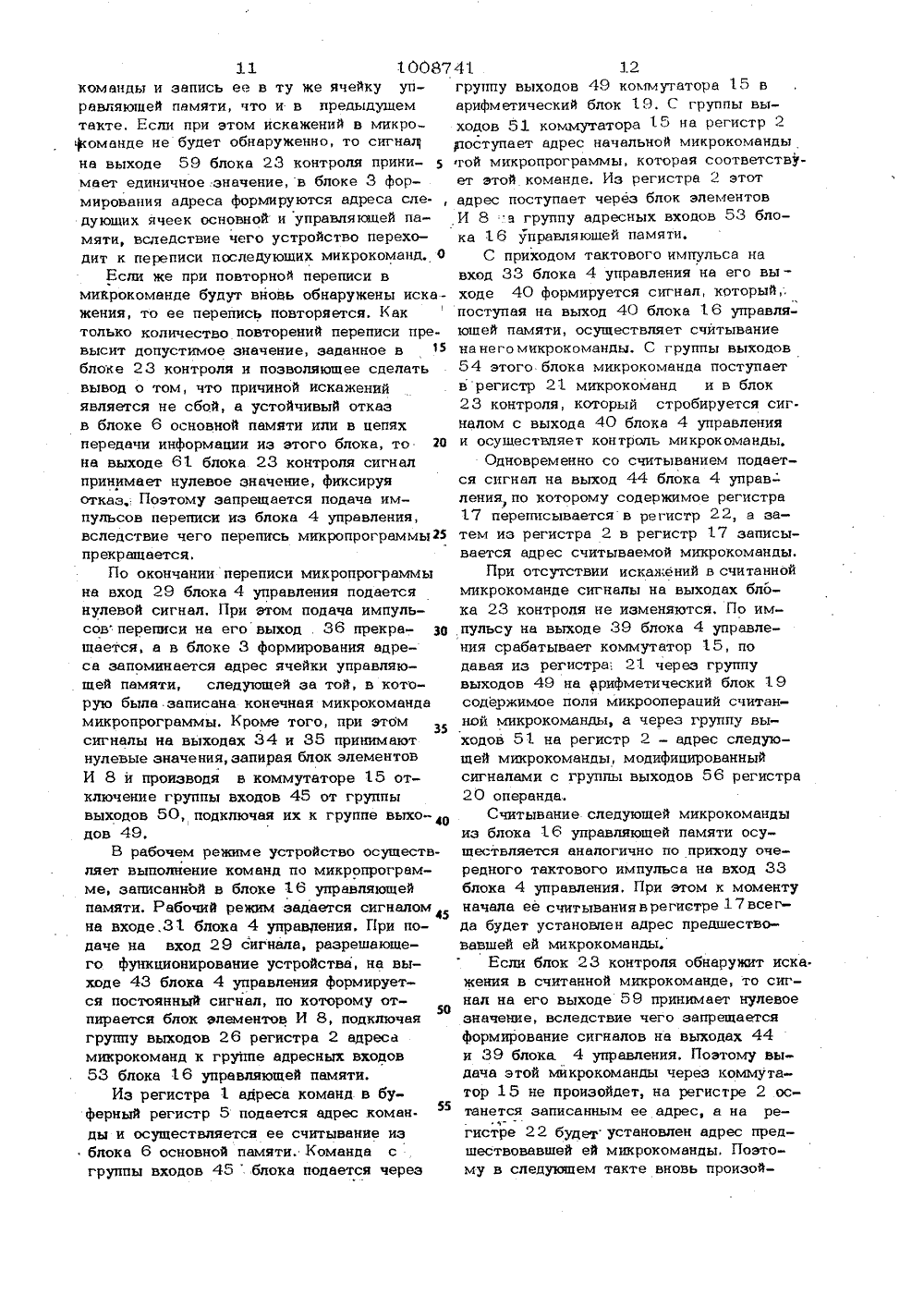

/с бОПИСАНИЕ ИЗОБРЕТЕ ЛЬ Т ОРСНОМУ СЕИД К Барбаш, Г. Н. Ти С, Харченко,ило и В. И. Си ельство СССР15/00, 1979ство СССР06 Р 15/00,и ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ% 656066, кл. С 062. Авторское свидетельо заявке М 2503575, кл,41978, (прототип) .(54) (57) 1.МИКРОПРОГРАММНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее блок формирования адреса, блок управления, блок основной памяти, блок управляющей памяти, арифметический блок, коммутатор, регистр операнда, буферный регистр, регистр адреса микрокоманд и регистр адреса команд, выходы которогосоединены с первой группой входов буферного регистра, выходы которого соединены с адресными входами блока основнойпамяти, выход которого соединен с первым информационным входом коммутатора, первый выход которого соединен спервым входом арифметического блока,выход которого соединен с входом регистра операнда, первый выход которого соединен с вторым входом арифметическогоблока, второй выход регистра операндасоединен с первым управляющим входомкоммутатора, второй выход которого соединен с первым информационным входом регистра адреса микрокоманд, второй информационный вход которого соединен с первымвыходом блока формирова ния адреса, второйвыход которого соединен с второй группойвходов буферного регистра, первый и второй,80100841 А выходы блока управления соединены соответственно с вторым и третьим управляющими входами комму.атора, третий выход блока управления соединен с управляющими входами буферного регистра и блока основной памяти и с первым управляющим входом блока формирования адреса, второй и третий управлякяпие входы которого соединены соответственно с четвертым и пятымвыходами блока управления, шестой и седьмой выходы которого соединены соответственно с первым и вторым управляющими входами блока управляющей памяти, выход которого соединен с входом регистра микрокоманд, выход которого соединен с вторым информацион- ФЮ . ным входом коммутатора, о т л и ч а ю - ш е е с я тем, что, с целью повышенияотказоустойчивости и быстродействия, оно :дополнительно содержит два буферныхрегистра, элемент ИЛИ, два блока эле-. ;ментов ИЛИ, пять блоков элементов И,элемент задержки и блок контроля, первый выход которого соединен с первым входом блока управления и четвертым управляю- фв 4 щим входом блока формирования адреса, второй выход блока контроля соединен с кафф четвертым управляющим входом коммута- фр тора третий выход которого соединен с первым информационным входом блока контроля и с первымвходомпервого блока эль. ментов И, выход которого соединен с информационным входом блока управляющей памяти, выход которого соединен с ф вторым информационным входом блока конт ффф роля третий выход которого соединен с пятым управляющим входом блока формирования адреса, выход регистра адреса. микро команд соединен с информационным входом Йвка формировании адреса ис первыми входами первого второго и третьего блоков элетаются неизменными. При поступленииследующего тактового импульса на блок4 управления на его выход 38 подаетсясигнал, по которому в блоке 3 формирования адреса формируется адрес той ячейки блоха 16 управляющей памяти, которая следует за последней занятой ячейкой и является свободной Кроме того,по этому сигналу осуществляется сбросблока 23 контроля, на выходах которого 1 Оустанавливаются значения сигналов, соответствующие исходному состоянию уст-.ройства в рабочем режиме, вследствиечего в коммутаторе 15 осуществляетсяподключение группы входов 45 к группе 15выхоцов 49 и разрешается подача черезнего информации из регистра 21 микрохоманд на арифметический блок 19 и нарегистр 2 адреса микрокоманд,При поступлении следующего тактового щ 0импульса в блоке 4 управления разрешается формирование в следующих тактахсигналов на его выходах 39, 40 и 44.Таким образом, устройство переводитсявновь в рабочий режим, В следующем так-дте иэ блока 16 управляющей памяти считывается переписанная микрокоманда. Ееадрес был установлен в регистре 2 припереписи, Считывание последующих микрокоманд осушествляется аналогично описанному выше.Если при переписи в микрокомандебудут обнаружены искажения, то сигнал на,выходе 59 блока 23 контроля принимаетйулевое значение и запрещает формирование сигнала на выходе 38 блока 4 управ 35ления. Поэтому адреса ячеек блоков 6 и16 основной и управляющей памяти, сформированные в блоке 3 формирования адреса перед началом переписи микроманды,40остаются без изменений. Сброс блока 23хонтроля не производится, поэтому хоммутатор 15 остается в прежнем состоянии,подключая группу входов 45 к группе выходов 50. Кроме того, при поступлении45следующего тактового импульса в блоке 4управления сохраняется запрет на формирование сигналов на выходах 39, 40 и44. Вследствие этого, начиная со спедующего такта, повторяется процесс переписизабракованной микрокоманды в ту же са 50мую ячейку блока 16 управляющей памяти. Как только количество; повторенийпревысит допустимое значение, сигналы,на выходах 61 и 63 блока 23 контроля принимают нулевое значение, запрещая формирование сигналов блоком 4 управления итем самым прекращая работу устройства15 1008741 16Блок 4 управления (фиг. 2) работаетследующим образом.Пои подаче на вход 30 сигнала, задающего режима переписи,Я = триггер64 устанавливается в единичное состояне. Сигналом на входе 29, разрешающимфункционирование устройства, отпираетсяэлемс: т И 65,выходной сигнал которого."поступает на выход 34 и через элемент ИЛИ 78 - на выход 35, задавая режим переписи в блоке 23 контроля икоммутаторе 15 соответственно. Таккак на выход 6 1 в исходном для режима переписи состоянии подан постоянный единичный сигнал, то импульс переписи свхода 3 2 поступает через элемент И 70и элемент ИЛИ 79 на выход 36, осуществляя считывание михрокоманд изблока основной памяти 6 и стробируя блок23 контроля и блок 3 формирования ад-реса, Элемент 75 задержйвает этот импульс на время, необходимое для считывания информации из блока 6 основнойпамяти, и через элемент ИЛИ 80 формирует на выходе 41 сигнал записи. Элемент 76 задержки через время, необходимое для срабатывания блока 23 контроля, подает на выход 37 сигнал на формирование адресов следующих ячеек основной и управляющей памяти в блоке 3формирования адреса, При поступлении следующего импульса переписи блок работаетаналогично, При сбоях алгоритм его ра боты не изменяется.лЕсли будет эафихсирован отказ блока 6 основной памяти, то нулевым значеницм сигнала на входе 3 запрещаетсяформирование импульсов на выходах 36,37 и 41.При подаче на вход 31 сигнала, задающего рабочий режим, триггер 64устанавливается в нуль, и с подачей разрешающего сигнала на вход 29 отпирается элемент И 66, формируя на выходе43 постоянный сигнал, по которому выходы регистра 2 адреса микрокомандподключаются к адресным входам блока16 управляющей памяти. При этом также. отпирается элемент И 67. Через неготактовый импульс с входа ЗЗ поступаетна выход 40, осуществляя считываниемикрохоманды из блока 16 управляющейпамяти. Через открытый элемент И 71импульс поступает также на выход 44 дляосуществления переписи адресов в буферные регистры 17 и 22. цемент 74задержки через время, необходимое длясрабатывания блока 23 контроля, черезоткрытый элемент И 72 формирует им17 1008пульс на выходе 39, разрешая в коммутаторе 15 выдачу информации из регистра21 микрокоманд на регистр.2 адресамикрокоманд и на арифметический блбк19. С приходом следующего тактовогоимпульса цикл работы блока управленияповторяется.Если при считывании микрокоманды нзблока 16 управляющей памяти будет зафиксирован сбой, то нулевым значением сиг- Енала на выходе 59 запираются элементыИ 71 и 72, запрещая формирование навыходах 44 и 39 и обеспечивая тем самымповторение микрокоменды, Если же будетзафиксирован отказ, то единичным значением сигнала на выходе. 63 запираетсяэлемент И 67 и отпирается элемент И 69,разрешая запись тактовых импульсов всчетчик 81. Тем самым в блоке задается режимвосстановления.30В этом режиме с приходом первого тактового импульса на выходе 87 дешифрато. ра 82 фиксируется сигнал, который поступает через элементы ИЛИ 78 и 79 невыходы 35 и 36, в результате чего наблок 16 управляющей памяти подаетсяадрес свободной ячейки и восстанавливаемая микрокоманда, которая такжепоступает на блок 23 контроля,Кроме того, на выход 83 дешифратора 82 подается постоянный сигнал, который сохраняется до тех пор, пока счетчик 81 установится в нуль. Этим сигналом отпирается элемент И 68, которыйтеперь независимо от сигналов на входахблока управления обеспечивает подачу импульсов на счетчик 81 до тех пор, покаон установится в нуль, Этим же сигналом.запирается элемент И 67, запрещая переход в рабочий режим.С приходом второго тактового импульсана выходе 85 дешифратора 82 формируется -сигнал, который через элемент ИЛИ 80 поступает на выход 41 и осуществляетсязапись восстанавливаемой микрокомандыв блок 16 управляющей памяти,. 45С цриходом третьего тактового импульса на выходе 86 дешифретора 82формируется сигнал, который поступаетна выход 42, осуществляя перекоммута-цию информационных и адресных входовфблока 16 управляющей памяти, а такжена выход 41, осуществляя запись новогоадреса в адресную часть микрокоманды,предшествовавшей забракованной.И При поступлении четвертого тактовогоимпульса формйруется сигнал на выходе84 дешифратора 82 741, 18 Если результат контроля переписываемой микрокоманды окажется положительным то этот сигнал через открытый элемент И 73 поступает на выход 38,осуществляя сброс блока 23 контроля иформирование адреса следующей свободнойячейки Управляющей памяти.С приходом тактового импульса счетчик81 устанавливается в нуль в результатечего сигнал на выходе 83 дешифратора при.нимает нулевое значение, запирая элементИ 68 и отпирая элемент И 67, разрешая.тем самым формирование в последующихтактах сигналов на выходах 40, 39 .44,управляющих режимов.Если же будет зафиксирован сбой в переписываемой микрокоманде, то с приходомчетвертого импульса сигнал на выходе 38сформирован не будет так как элементЯ 73 будет заперт нулевым сигналом навыходе 59. Поэтому режим восстановлениябудет. сохранен, и с поступлением шестого,тахтового импульса повторится цикл перезаписи той же самой микрокоменды.Если же при переписи будет зафиксирован отказ, то нулевыми значениями сигналов на выходах 63 и 61 будут запертыэлементы И 69 н 67 соответственно,вследствие чего выдача управляющих сигналов по окончании последнего цикле переписи будет прекращена.Блок 3 формирования адреса фиг. 3)работает следующим образом.При переходе в режим переписи в счетчик 92 записывается адрес начальной ячейки основной памяти, а в.счетчик 93 адрес начальной ячейки управляющей памяти. По сигналу на выходе 36 блока 4управления содержимое счетчике93 через блок элементов И 90 подается нагруппу выходов 28, а содержимое счетчика 92 через группу выходов 27 записывается в буферный регистр 5. При отсутствии сбоев в переписываемой микрокоманде элемент И 89 остается открытымединичным сигналом на выходе 59, поэтому импульс с входа 37 поступает на:динамические входы счетчиков 92 и 93и устанавливает на них адреса следующихячеек основной и управляющей памяти соответственно.3Боди при переписи микрокоманды будет зафиксирован сбой то поступлениесигнала на динамические входы счетчика.запрещается нулевым синадом на выходе 59, запрещающим элементом И 89. Приотказах сигнал на выходе 37 не формируется, 19 100874120По окончании режима переписи, таким пирает элемент И 111, Переписываемаяобразом, на счетчике 93 будет установлен микрокоманда с группы выходов 50 чеадрес очередной свободной ячейки управля- рез блок элементов ИЛИ 106 подаетсяющей памяти. на узел 110 контроля четности, которыйВ режиме восстановления по сигналу 5 при отсутствии искажений формируетна выходе 62 отпирается блох элементов на выходе нулевой сигнал, а при наличии4 88, подавая с группы выходов 26 на искажений - единичный. Одновременно сшифратор 94 адрес управляющей памяти, в подач й переписываемой микрокоманды покоторой записана забракованная микроко- дается импульс опроса на выход 36, Онмвнда. По этому адресу шифратор 94 фор,задерживается элементом 117 задержкимирует адрес соответствующей ячейки ос- нв время, равное времени срабатыванияновной памяти и устанавливает его на узла 110 контроля четности и постусчетчике 92 через группу входов. Затем пает на вход элемента И 113, При полопо сигналу на выходе 36 из счетчика 93 жительном результате контроля элементна группу выходов 28 подается адрес свобудет заперт, счетчик 124 останется вбодной ячейки управляющей памяти. Затем нулевом состоянии, вследствие чего си- по сигналу на выходе 38 содержимое нал на выходах дешифратора 122 сохрасчетчика увеличивается на единицу, зада- няет нулевое значение, а сигнал на вывая адрес очередной свободной ячейки уп- ходе блока контроля - единичное, Затемравляющей памяти. 0 импульс опроса, пройдя через элементКоммутатор 15 (фиг, 4) работает сле задержки через время, необходимое длядующим образом. срабатывания счетчика 124 и дешифраторВ режиме переписи на его выходы 35 122 через открытый элемент И 114 ии 60 подаются единичные сигналы, вслед- ИЛИ 108 поступит на вход счетчика 124ствие чего блоки элементов И 98, 100 5 для установки его в нуль,и 103 запираются, а блоки элементов При отрицателььом результате контИ 99 и 101 отпираются, подключая груп- роля элемент И 113 будет открыт сигпу выходов 44 к группе выходов 50, налом на входе со схемы контроля четносВ рабочем режиме сигнал на выходе 35,ти импульса опроса, счетчик 124 устапринимает нулевое значение, вследствие 50 новится в единицу, Сигнал на выходе дечего блоки И 99 и 101 запираются, а шифратора 122 станет единичным, а наблоки элементов И 98 и 100 отпираются,:выходе 59 блока контроля - нулевым.образуя цепи для подачи информации с Так как элемент И 114 будет заперт. погруппы входов 45 на группу выходов инверсному входу единичным сигналом с49. При этом адрес начмьной микроко- выхода узла 110 контроля четности,55манды подается через блок элементов ИЛИ то сброс счетчика 124 не произойдет,105 также и на группу выходов 51. Если же при повторной переписи реПри подаче разрешающего сигнала на зультат контроля окажется положительвыход 39 отпираются блоки элементов ным, то элемент И 114 откроется, вследИ 102 и 103, подавая с группы вы 40ствие чего счетчик 124 будет установленходов 57 сигналы микроопераций на груп. в нуль, сигнал на выходе дешифраторапу выходов 49, а код адреса следующей станет нулевым, а на выходе 59 блокамикрокоманды - через блоки элементов контроля - единичным.И 104 н ИЛИ 105 - на группу выходов Если же при повторно переписи51, При этом осуществляется модифика- результат контроля вновь окажется от 45ция адреса сигнвламн на группе выхо- рицательным, то число, установленное надов 56, счетчике 124, станет равно двум и т. д.При переходе в режим восстановления Как только это число станет большесигнал на выходе 60 становится рав- допустимого, в блоке контроли фиксируетным нулю и запирает, блоки элементов ся отказ. Сигнал на выходе дешифратораИ 98, 100, 102" и 103, По подаче сиг. становится равным единице, отпирая эле 50нала на выход 35 отпираются блоки эле- менты И 115 и 111, Через элементыментов И 99 и 101, обеспечивая подачу И 111 и ИЛИ 109 триггер 121 устаинформации с группы входов 45 на груп- навпивается в единицу, н сигнал на выну выходов 50, ходе 61 становится нулевым, блокируяБлок контроля (фиг, 5) работает сле работу устройства, Импульс опроса черездующим образом, элемент И 115 установит счетчик 124В режиме переписи на его выход 34 в нуль, вследствие чего сигналы наподается постоянный сигнал, который от- выходах дешифратора 120 станут нуле21 1008741 22 выми. Лля разрешения дальнейшего функпи обеспечивая восстановление в блоке контонирования устройства триггер 121 роля состояния, являющееся исходным должен быть установлен в нуль. для рабочего режима. Если же при восВ рабочем режиме и режиме восстанов- становлении количество повторных,пик- ления на выход 34 блока 23 контролялов переписи станет больше допустимого, подается нулевой сигнал, запйраюший то сигнал с выхода дешифратора 122 пос- элемент И 111 и отпирающий элемент ,тупит через элементы И 112, 116 и И 112, Контроль микрокоманды, поступа- ИЛИ 109 на триггер 121 и установит его ющей на группу выходов 54, и подсчет в единицу. Сигнал на выходе 61 становит количества ее повторных. считываний осу ся нулевыму блокируя функционирование ществляется аналогично вышеописанному устрйстпо импульсам опроса, подаваемым на вы-. Таким образом, в устройстве осущестход 40, Как только это количество ста- вляется коытроль микрокоманды при перенет больше допустимого в блоке контро- писи их в блок управляющей памяти и ля фиксируется отказ. При этом по сиг- % считывании из него. Юри этом обеспечиналу с выхода дешифратора 122 разре- вается восстановление микрокоманд: при шается установка счетчика 124 в нуль сбоях путем их повторения, а при отка на выходе 62 формируется единичный сиг- зах ячеек блока управляющей памяти - нал, триггер 120 устанавливается в еди- путем переписи неискаженного значения нипу, в результате чего сигнал на вы- о микрокоманды из блока основной памяти ходе 63 становится единичным, а на вы- в свободную ячейку бло 1.а управляющей ходе 60 нулевым. Тем самым в уст- памяти с обеспечением обхода отказавших ройстве задается режим восстановления, ячеек и внесения соответствующих измеЕсли при восстановлении результат некий в адресной части предшествовавшей контроля переписываемой микрокомандй 2 З ей микрокоманды после чего и родолокажется положительным, то на выход 38 жается нормальное выполнение следукйпих поступает импульс сброса, по которому . микрокоманд. За счет этого достигается триггер 120 устанавливается в нуль, повышение отказоустойчивости устройства.8741 100 ментов И, выход первого блока элементов И подключен к второму входу первого блока элементов ИЛИ, выход второго блока элементов, И подключен к адресному входу блока управляющей памяти, выход третьего блока элементов И подключен к входу второго буферного регистра, выход кото-, рого соединен с первым входом четверто- го блока элементов И, выход которого соединен с входом третьего буферного регистра, выход которого соединен с первым входом пятого блока элсментов И, выход которого соединен с вторым выходом второго блока элементов ИЛИ, четвертый и пятый выходы блока контроля соединены соответственно с вторым и третьим входами блока управления, восьмой вы 3 сод которого соединен с вторым входом четвертого блока элементов И и через элемент задержки - с вторым входом третьего блока элементов И, девятый выход блока управления соединен с вторыми входами первого и пятого блоков элементов И и с инверсным входом второго блока элементов И, первый и десятый выходы блока управления соединены с первым и вторым входами элемента ИЛИ, выход которого соединен с вторым входом Гвторого блока элементов И, одиннадцатый, третий, шестой и пятый выходы блока управления соединены с первым, вторым, третьим и четвертым управляющими входами блока контроля,. первый, второй, третий, четвертый и пятый управляющие входы устройства соединены соответственно с четвертым, пятым, шестым, седьмым и восьмым входами блока управления.2; Устройство по и. 1, о т л и ч а ющ е е с я тем, что блок управления со-, держит триггер режима, девять элементов И, три элемента задержки, четыре элемента ИЛИ, счетчик и дешифратор, первый выход которого соединен с девятым выходом блока управления и с первым входом первого элемента ИЛИ, выход которо го соединен с седьмым выходом блока управления, второй выход дешифратора соединен с вторым входом первого элемента ИЛИ, третий выход дешифратора соединен с первым входом первого элемента И, выход которого соединен с пятым выходом блока управления, четвертый выход дешв 5 ратора через второй и третий элементы ИЛИ соединен соответственно с первым и третьим выходами блока управления, пятый выход дешифратора соединен с пер вым инверсным входом второго элемента И и с первым входом третьего элемента 1И, выход которого соединен с первым входом четвертого элемента ИЛИ, выходкоторого соединен с динамическим входом счетчика, выходы которого соединеныс входами дешифратора, третий вход блока управления соединен с вторым инверсным входом второго элемента И и с первым входом четвертого элемента И, выхоГ. которого соединен с вторым входом четвертого элемента ИЛИ, пятый вход блока управления соединен с вторымивходами третьего и четвертого элементовИ и с первым прямым входом второгоэлемента И, выход которого соединен сшестым выходом блока управления, черезпервый элемент задержки с первым входом пятого элемента И, выходкоторогосоединен с вторым выходом блока управления, выход второго элемента И соединен с первым входом шестого элементаИ, выход которого соединен с восьмымвыходом блока управления, вторые входыпервого, пятого и шестого элементов Исоединены с первым входом блока управления, четвертый вход блока управлениясоединен с первым входом седьмого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ ичерез второй элемент задержки - с третьим входом первого элемента ИЛИ, и че-,рез третий элемент задержки - с чет.вертым выходом блока управления, вто:рой прямой вход второго элемента И соединен с вторым входом блока управления,вторым и третьим входами соответственно седьмого и первого элементов И, второй вход блока управления соединен с единичным входом триггера режима, нулевой вход которого соединен с третьим входом блока управления, единичный выход триггера режима соединен с первым входом восьмого элемента И, выход которого соединен с третьим входом седьмого элемента И, с одиннадцатым выходом блока управления и с вторым входом Ьторого элемента ИЛИ, нулевой выходтриггера режима соединен с первым входом девятого элемента И, выход котороо соединен с десятым выходом блока управления, третьим прямым и третьим входами соответственно второго и четвертого элементов И, вторые входы восьмогои девятого элементов И соединены с первым входом блока управления. рй и. 1,отлич ю. щ е е с я тем, что,блок формирования адреса содержит шифратор, элемент ИЛИ, элемент И, два блока элементов И и два ,счетчика, причем информационный вход блока соединен с первым входом первого8741 100 блока элементов И, выход которого соединен с входом шифратора, выход которого соединен с установочным входом первого счетчика, выходы которого являют-, ся вторым выходом блока формирования адреса, пятый управляющий вход блоха формирования адреса соединен с вторыми входами первого блока элементов И, чет. вертый и второй управляющие входы блока формирования адреса соединены с входами элемента И, выход которого соединен с динамическим входом первого счет- чиха и через элемент ИЛИ - с динамическим входом второго счетчика, выход которого через второй блох элементов И соединен с первым выходом блока формирования адреса, первый управляющий вход блока формирования адреса соединен с вторыми входами второго блока элементов И, третий управляющий вход блока соединен с вторым входом виремента ИЛИ.4. Устройство по п. 1, о т и и ч в - ю ш е е с я тем, что блок контроля содержит узел контроля четности, блок элементов ИЛИ, три элемента.ИЛИ, инвертор, три элемента задер)ккичетыре элемента И, два триггера,дешифратор и счетчик, выходы которого соединены с входами дешифрвтора, первый выход которого через инвертор соединен с первым выходом блока контроля, второй выход дешифратора соединен соответственно с первыми входами первого, второго и прямым входом третьего элементов И, первый, второй информационные входы блока контроля соединены с .входами блока элементов ИЛИ, выход которого соединен с входом узла контроля четности, выход 1 которого соединен соответственно с первым и инверсным входами четвертого и пятого элементов И, второй и третий управляющие входы блока соединены с входами первого элемента ИЛИ, выход которого че рез первый элемент задержки соединен с1 вторым входом четвертого элемента И, выход которого соединен с входом счетчике, выход которого соединен с входом дешвраторавыход первого элемента задержки через второй элемент задержки соединен соответственно с прямым и вторым входами пятого и первого элементов И, выходы которых соединены с входами второго элемента ИЛИ, выход которого соединен с входом установки в нуль счетчика, первый управляэмций вход блока соединен соответственно с вторым и.инверсным входами второго и третьего элементов И, выход второго элемента И соединен с первым входом третье го элементе ИЛИ, второй вход которогосоединен с выходом шестого элемента И, а выход - с единичным входом первого триггера, инверсный выход которого соединен с четвертым выходом блока, выход третьего элемента И соединен с третьим выходом блока, со счетным входом второго триггера и с первым входом шестого элемента И, второй вход которого через третий элемент задержки соединен с пятым выходом блока и прямым выходом второго триггера, вход которого соединен с четвертым входом блоха, а инверсный выход - с вторым выходом блока."использовано в устройствах управления цифровых вычислительных машин, Известен микропрограмный процессор с восстановлением при сбоях, содержащий блок сопряжения с памятью, блок памяти, блок регистров, блок управления регистр микрокоманд регистр адреса микрокоъювнд, коммутатор выдачи, арифметикологический блок, блох контроля, счетчик сбоев, коммутатор приема, регистр адреса приема, регистр исходной информации, регистр адреса повтора, элементы И Я,0 33 2.Недостатком этого процесса являетсанизкая функциональная надеМаость и низкое быстродействие, обусловленные невоз-,моясностью автоматического восстановленин микрокоманд приотказах ячеекблока памяти,Наиболее близким по технической сущности и достигаемому результату к предлагаемому является вычислительное устрой-ство, содержащее блок формирования адреса, блох управления, блок основной памяти, блок управлщощей памяти,арифметический блок, кбммута тор, регистр операнда, буферный регистр, регистр адреса микроко3. 1008 манд, регистр микрокоманд и регистр адреса команд, выходы которого соединены с первой группой входов буферного регистра, выходы которого соединены с первой .руппой входов блока основной памяти, выходы которого через коммутатор соединены с первой группой входов арифметического блока, выходы которого соединены с входами регистра операнда, первая группа выходов которого соединена с вто О рой группой входов арифметического блока вторая группа выходов регистра операнда соединена с второй группой входов коммутатора, вторая группа выходов соединена с первой группой входов регистра 15 адреса мккрокоманды, вторая группа входов которого соединена с первой группой выходов блока формирования адреса, вторая группа выходов которого соединена с второй группой входов буферного регисте ра, причем первый и второй выходы блока, управления соединены соответственно с первым и вторым управляющими входами коммутатора, третий выход блока управления соединен с управляющими входами буферного регистра и блока основной памяти и с первым управляющим входом бло ка формирования адреса, второй и третий управляющие входы которого соединены соответственно с четвертым и пятым выходами блока управления, шестой и седьмой выходы которого соединены соответственно с первым и вторым управляющими входами блока управляющей памяти, выходы которого соединены с входами регистре микрокоманд, выходы которого соединены с третьей группой входов коммутаторе Д .Недостатками этого устройства являются низкая функциональная надежность и низ кое быстродействие.Низкая функциональная надежность устройства обусловлена отсутствием контроля микрокоманд при переписи их в блок управляюшей памяти и считывании из него, а также невозможностью автоматического восста45 новления правильного значения микрокоманды при сбоях или при отказе соответствующей ячейки блока управляющей памяти. 50Низкое быстродействие устройства обусловлено тем, что в нем восстановление правильного значения микрокомандыпри сбоях возможно лишь путем повторного выполнения всей микропрограммы/ 55 а при отказах ячеек блока управляющей памяти - путем перезаписи всей микропрограммы, в то время как вполне достаточно было бы повторить считывание или 741 фперепись лишь забракованной микрокоманды.Цель изобретения - повышение отказоустойчивости и быстродействия устройства.Поставленная цель достигается тем, нто в устройство, содержащее блок форми- рования адреса, блок управления, блок основнс" памяти, блок управляющей памяти, арифметический блок, коммутатор, регистр операнда, буферный регистр, регистр адреса микрокоманд и регистр адреса команд, выходы которого соединены с первой группой входов буферного регистра, выходы ко торого соединены с адресными входами блока основной памяти, выход которого соединен с первым информационным входом коммутатора, первый выход которого соединен с первым входом арифметического блока, выход которого соединен с входом регистра операнда, первый выход которого соединен с вторым входом ериф 1 метического блока, второй выход регистре операнда соединен с первым управляющим входом коммутатора, второй вьход которого соединен с первым информационным входом регистра адреса микрокоменды, второй информационный вход которого соединен с первым выходом блока формирования адреса, второй выход которого соединен с второй группой входов буферного регистра, первый и второй выходы блоке управления соединены соответственно с вторым и третьим управляющими входами коммутатора, третий выход блоке управления соединен с управляющими входами буферного регистра и блока основной памяти и с первым управляющим входом блока формирования адреса, второй и третий управляющие входы которого соединены соответственно с четвертым и пятым выходами блока управления, шестой и седьмой выходы которого соединены соответственно с первым и вторым управляющим входами блока управляющей памяти, выход которого соединен с входом регистра микрокоманд, выход которого соединен с вторым информационным входом коммутатора, дополнительно введены два буферных регистра, элемент ИЛИ, два блока элементов ИЛИ, пять блоков элементов И, элемент задерж. ки и блок контроля, первый выход которого соединен с первым входом блока управления и четвертым управляющим входом блока формирования адреса, второй выход блоха контроля соединен с четвертым управляющим входом коммутатора, третий выход которого соединен с первым информационным входом блока конт5 1008741 6роля и с первым входом первого блока ИЛИ, третий выход дешифратора соединен элементов И, выход которого соединен с первым входом первого элемента И, с информационным входом блока управляю- выход которого соединен с пятым выходом щей памяти, выход которого соединен сблока управления четвертый выход девторым информационным входом блока конт шифратора через второй и третий элероля, третий выход которого соединен с )менты ИЛИ соединен соответственно с уятым управляющим входом блока форми- первым и третьим выходами блока управ- рования адреса, выход регистра адреса ления, пятый выход дешъфратора соединен микрокоманд соединен с ннформвцион- с первым инверсным входом второго эленым входом блока формирования адре- .1 О мента И и с первым входом третьего са и с первыми входами первого, второ- элемента И, выход которого соединен с го и третьего блоков элементов И, выход первым входом четвертого элемента ИЛИ, первого блока элементов И подключен к выход которого соединен с динамическим второму входу первого блока элементов входом счетчика, выходы которого сое- ИЛИ, выход второго блока элементов И 15 динены с входами дешифратора, третйй вход подключен к адресному входу блока упрв- блока управления соединен с вторым инляюшей памяти, выход третьего блока эле версным входом второго элемента И.и с мент в И подключен к входу второго бу- первь 1 м входом четвертого элемента И. Выферного регистра, выход которого соединен ход которого соединен с вторым входом с первым входом четвертого блока еле 1 о четвертого элемента ИЛИ, пятый вход ментов И, выход которого соединен с в.-, блока управления соединен с вторыми входом третьего регистра, выход которого дами третьего и четвертого элементов И . соединен с первым входом пятого блокаи спервым прямым входом второго элеэлементов И, выход которого соединен с мента И, выход которого соединен с шесвторым входом второго блока элементов 15 тым выходом блока управления, через пер. ИЛИ, четвертый и пятый выходы блока вый элемент задержки с первым входом контроля соединены соответственно с пятого элемента И, выход которого соевторым и третьим выходами блока управ- динен.с вторым выходом блока управлеления, восьмой выход которого соединен ния, выход второго элемента И соединен с вторым входом четвертого блока эле- Зо с первым входом шестого элемента И, ментов И и через элемент задержки с выход которого соединен с восьмым вывторым входом третьего блока элементов ходом блока управлениявторые входы И, девятый выход блока управления сое- первого , пятого и шестого элементов И динен с вторыми входами первого и пято- соединены с первым входом блока управ го блоков элементов И и с инверсным ления четвертый вход блока управления35Эвходом второго блока элементов И,.пер соединен с первым входом седьмого элевый и десятый выходы блока управления мента И, выход которого соединен с вто+ соединены с первым и вторым входами рым входом третьего элемента ИЛИ черезэлемента ИЛИ, выход которого соединен орой элемент задержки - с третьим с вторым входом второго блока элементоввходом первого элемента ИЛИ и через40И, одиннадцатый третий, шестой и пятый трегий элемент задержки - с четвертым выходы блока управления соединены соотг- выходом блока. управления; второй прямой ветственно с цервым,вторым третьим и вход второго элемента И соединен с)четвертым управляющими Входами блока вторым входом блока управления, вторым контроля, первый второй, третий, четвер- и тречъим входами соответственноседь- .4, тый и пятый управляющие входы устройст- мого и первого элементов И, второйва соединены соответственно с четвер вход блока управления соединен с единичтым, пятым, шестым, седьмым и вось- ным входом триггера. режима, нулевой мым входами блока управления.ютвход которого соединен с, третьйм входом, При этом блок управления содержит блока управления, единичнйй выход тригтриггер режима, девять элементов И, . гера режима соединен с первым входом три элемента задержки, четыре элементе восьмого элемента И, выход которого ИЛИ, счетчик и дешифратор, первый вы- соединен с третьим входом седьмого элеход которого соединен с девятым выходом менте И, с одиннадпатым выходом бло-блоха управления и с первым входом ка управления и с вторым входом второго. первого элемента ИЛИ,.выход которого элемента ИЛИ, нулевой выход триггера соединен с седьмым выходом блока уп- режима соединен с первым входом девяравления, второй выход дешифратора сое- того элемента И, выход которого:соедидинен с вторым входомпервого элемента нен с десятым выходом блока управления,7 10 О 8третьим прямым и третьим входами соответственно второго и четвертого элементов И, вторые входы восьмого и девятогоэлементов И соединены с первым входомблока управления.5Кроме того, блок формирования адре. са содержит шифратор элемент ИЛИ, элемент И, два блока элементов И и двасчетчика, причем информационный вход блока формирования адреса соединен с первым входом первого блока элементов И,выход которого соединен с входом шифратора, выход которого соединен с установочным входом первого счетчика, выходы которого являются вторым выходомблока формирования адреса, пятый управляющий вход блока формирования адреса соединен с вторыми входами первогоблока элементов И, четвертый и второйуправляющие входы блока формирования 20адреса соединены с входами эдемента И,выход которого соединен с динамическимвходом первого счетчика и через элемент ИЛИ - с динамическим входом второго счетчика, выход которого через вто- Ирой блок элемента И соединен с первымвыходом блока формирования адреса,первый управляющий вход блока формирования адреса соединен с вторыми входамивторого блока эламентов И, третий управ-ЗОляюший вход блока соединен с вторым входом элемента ИЛИ,Блок контроля содержит узел контролячетности, блок элементов ИЛИ, три элемента ИЛИ, инвертор, три элемейта задержки четыре элемента И, два триггера,дешифратор и счетчик, выходы которогосоединены с входами дешифратора, первыйвыхой которого через инвертор соединен спервым выходом блока контроля, второй вы- оход дешифратора соединен соответственно,с первыми входами первого, второго и прямым входом третьего эдементов И, первый и второй информационные входы блока контроля соединены с входами блокаэлементов ИЛИ, выход которого соединенс входом узда контроля четности, выходкоторого соединен соответственно с первым и инверсным входами четвертого ипятого элементов.И, втоРой и третий унравляющие входы блока соединены с входами первого элемента ИЛИ, выход которого через первый элемент задержки соединен с вторым входом четвертого элемента И, выход которого соединен сосчетным входом счетчика, выход которогосоединен с входом дешифратора, выходпервого элемента задержки через второйэлемент задержки соединен соответствен 741 8но с прямым и вторым входами пятого ипервого элементов И, выходы которыхсоединены с входами второго элементаИЛИ, выход которого соединен с входомустановки в нуль счетчика, первый управ.ляющий вход блока соединен соответст .венно с вторым и инверсным входамивтороо и третьего элементов И, выходвторого элемента И соединен с первым вхо1 цом третьего элемента ИЛИ, второй входкоторого соединен с выходом шестого элемента И, а выход - с единичным входомпервого триггера, инверсный выход которого соединен с четвертым выходом.бло;.ка, выход третьего элемента И соединенс третьим выходом блока, со счетным входом второго триггера и с первым входом;шестого элемента И, второй вход которого через третий элемент задержки соеди- .нен с пятым выходом блока и прямым выходом второго триггера, вход которогосоединен с четвертым управляющим входомблока, а инверсный выход - с вторым выходом блока,На фиг, 1 представлена функциональнаясхема предлагаемого устройства; на фиг,2 функциональная схема блока управления;на фиг. 3 - функциональная схема блокаформирования адреса; на фиг. 4 - функциональная схема коммутатора; на фиг. 5функциональная схема блока контроля;на фиг. 6 - функциональная схема арифметического блока,Устройство (фиг, 1) содержит регистр1 адреса команд, регистр 2 адреса микрокоманд, блок 3 формирования адреса,блок 4 управления, буферный регистр 5,блок 6 основной памяти, блок элементов7 и 8, элемент ИЛИ 9, блок элементовИ 10, элемент 11 задержки, блоки элементов ИЛИ 12 и 13, блок элементовИ 14, коммутатор 15, блок 16 управляю.щей памяти, буферный регистр 17, блокэдементов И 18, арифметический блок 19регистр 20 операнда, регистр 21 микрокоманд, буферный регистр 22, блок 23контроля, первая группа входов 24 буферного регистра 1, адресные входы 25блока основной памяти, выход 26 регистра адреса микрокоманд, второй выход 27блока формирования адреса, первый выход 28 блока формирования адреса, первый 29, второй,30, третий 32, пятый 33управляющие входы устройства, одиннадцатый 34, первый 35, третий 36, четвертый 37, пятый 38, второй 39, шестой 40, седьмой 41, девятый 42, десятый 43 восьмой 44 выходы блока управления, первый информационный вход 45741 10функционирование устройства, на выходах34 и 35 блока 4 формируется сигнал,а на выход 36 подаются импульсы переписи. По сигналу на. вйходе 35 коммутатор 15 подключает группу входов45 к группе выходов 50, образуя цепьдля подачи информации из блока 6 основной памяти на группу информационныхвходов 52 блока 16 управляющей памяти,По этому сигналу группа выходов 26 регистра 2 адреса макрокоманд через блокэлементов И 8 подключается к группеадресных входов 53 этого блока.При подаче импульса переписи с выхода 36 блока 4 управления иэ блока 3формирования адреса через выход 27 вбуферный регистр 5 записывается адресначальной ячейки основной памяти, в которойхранится начальная мнкрокоманда переписываемой микропрограммы, а через вы:ход 28 в регистр 2 зайсываетса адрестой ячейки управляющей памяти, в которуюэта макрокоманда будет записана., Зтимже импульсом микрокоманда считыветсяиз блока 6 основной памяти и черезгруппу выходов 50 коммутатора 15 подается на группу информационных входов52 блока 16 управляющей памяти и нагруппу входов блока 23 контроля, который стробируется этим же ймпульсом носуществляется контроль микрокоманды.По сигналу записи, подаваемому изблока 4 управления на выход 41 блока16 управляющей памяти, осуществляетсязапись в него информации с группы входов 52, по адресу, поданному на группувходов 53 иэ регистра 2,Затем блок 23 контроля формируетрезультат контроля макрокоманды.При отсутствии в ней искажений сигналы на его выходах не иэменаютса. Поэтому при поступлении сигнала с выхода37 блока 4 управлениа в блоке 3 формирования адреса формируются адреса спе 1дуюшнх ячеек основной и управляющей па, мяти, При поступлении очередного импульса переписи устройство работает аналогично, осуществляется перепись спедуюшейми кроко манды.При наличии искажений в. переписываемой микрокоманде сигнал на выходе 59блока 23 контроля принимает нулевоезначение, вследствие чего в блоке 3формирования адреса ячеек основной иуправляющей памяти, сформированныеперед переписью :микрокоманды, остаются прежними. Поэтому при поступленииочередного импульса перепчси осулествлаетСя повторное считывание этой микро 9 1008коммутатор выходы 46-48 первого, второго и пятого блоков элементов И соответственно, первый 49, третий 50 и второй 51 выходы коммутатора соответственно информационный и адресный входы 52и 53 блока управляющей памяти, выход54 блока управляющей памяти, соответственно первый й второй выходы 55 и56 регистра операнда, выход 57 регистра)микрокоманд, выход 58 буферного ре-1 Огистра 22, соответственно первый, второй,четвертый, третий пятый выходы 59-63блока 23 контроля.Блок 4 управления (фиг. 2) содержиттриггер 64 режима элементы И 65-73,элементы 74-76 задержки, элементыИЛИ 77-80, счетчик 81 идешнфратора 82,соответственно пятый, третий, второй,первый и четвертый выходы 83-87 дешифратора,20Блок 3 формирования адреса (фиг. 3)содержит первый блок элементов И .88,элемент И 89 второй блок элементов И90, элемент ИЛИ 91, первый и второйсчетчики 92 и 93, шифратор 94 динамические входы 95 и 96 первого и второго счетчиков, установочный вход 97 пер-.вого счетчика 92.Коммутатор 15 (фиг. 4) содержит бяоки элементов. И 9 В 104 и блок элементов ИЛИ 105,30Блок 23 контроля (фиг. 5) содержитблок элементов ИЛИ 106, элементыИЛИ 107-109 узел 110 контропя четности, элементы И 111-116, элементы117-119 задержки триггеры 120 и 121,33)дешифратор 122, инвертор 123 и счетчик 124, выход 125 узла контропя четности, выход 126 элемента задержки,первый, второй выходы 127 и 128 дешифратора 122, вход 129 установки фсчетчика 124 в нуль.Арифметический блок 19 (фиг. 6)содержит регистр 130 и сумматор, 131Устройство может работать в режимеперег 1 иси микропрограммы из блока 6 45основной памяти в блок 16 управпяюшейпамяти в рабочем режиме и режиме восстановления,В исходном состоянии все регистрыустановлены в нуль, на выходах 59-61 30блока 23 контроля сигналы имеют единичное значение, на остальных его выходах ина всех выходах блока 4 управления- нулевое, на вход 30 подаются импульсы переписи, на вход 31 - тактовые импульсы рабочей частоты.Режим. переписи задается сигналом навходе 30 блока 4 управления, При подачена его вход 29 сигнала, расширяющего /11 10087команды и запись ее в ту же ячейку управляющей памяти, что и в предыдущемтакте, Если при этом искажений в микрокоманде не будет обнаруженно, то сигнална выходе 59 блока 23 контроля принимает единичное значение, в блоке 3 формирования адреса формируются адреса следующих ячеек основной и управляющей памяти, вследствие чего устройство переходит к переписи последуюших микрокоманд, 0Если же при повторной переписи вмикрокоманде будут вновь обнаружены искажения, то ее перепись повторяется, Кактолько количество повторений переписи превысит допустимое значение, заданное вблоке 23 контроля и позволяющее сделатьвывод о том, что причиной искаженийявляется не сбой, а устойчивый отказв блоке 6 основной памяти или в цепяхпередачи информации из этого блока, то 20на выходе 61 блока 23 контроля сигналпринимает нулевое значение, фиксируяотказ, Поэтому запрещается подача импульсов переписи из блока 4 управления,вследствие чего перепись микропрограммы 25прехращается.По окончании переписи микропрограммына вход 29 блока 4 управления подаетсянулевой сигнал. При этом подача импульсов переписи на его выход 36 прекращается, а в блоке 3 формирования адреса запоминается адрес ячейки управляющей памяти, следующей за той, в которую была записана конечная микрокомандемикропрограммы. Кроме того, при этомсигналы на выходах 34 и 35 принимаютнулевые значения, запирая блок элементовИ 8 и производя в коммутаторе 15 отключение группы входов 45 от группывыходов 50, подключая их к группе выхо-дов 49,В рабочем режиме устройство осуществляет выполнение команд по микропрограмме, записанной в блоке 16 управляющейпамяти, Рабочий режим задается сигналомна входе.31 блока 4 управления. При подаче на вход 29 сигнала, разрешающего функционирование устройства, на выходе 43 блока 4 управления формируется постоянный сигнал, по которому от 50пирается блок элементов И 8, подключаягруппу выходов 26 регистра 2 адресамикрокоманд к группе адресных входов53 блока 16 управляющей памяти,Из регистра 1 адреса команд в буферный регистр 5 подается адрес команды и осуществляется ее считывание изблока 6 основной памяти. Команда сгруппы входов 45блока подается через 41 12группу выходов 49 коммутатора 15 варифметический блок 19, С группы выходов 51 коммутатора 15 на регистр 2поступает адрес начальной микрокомандычой микропрограммы, которая соответствует этой команде. Из регистра 2 этотадрес поступает через блок элементовИ 8 .а группу адресных входов 53 блока 16 управляюшей памяти,С приходом тактового импульса навход ЗЗ блока 4 управления на его выходе 40 формируется сигнал, хоторыйпоступая на выход 40 блока 16 управляющей памяти, осуществляет считываниенанегомикрокоманды. С группы выходов54 этого блока микрокоманде поступаетв регистр 21 микрокоманд и в блок23 контроля, который стробируется сиг.налом с выхода 40 блока 4 управленияи осушествпяет контроль микрокоманды,Одновременно со считыванием подается сигнал на выход 44 блока 4 управ-ления по которому содержимое регистра17 переписывается в регистр 22, а затем из регистра 2 в регистр 17 записывается адрес считываемой микрокоманды.При отсутствии искажений в считанноймикрокоманде сигналы на выходах блока 23 контроля не изменяются, По импульсу на выходе 39 блока 4 управления срабатывает коммутатор 15, подавая из регистра; 21 через группувыходов 49 на арифметический блок 19содержимое поля микроопераций считанной микрокоманды, а через группу выходов 51 на регистр 2 - адрес следующей микрокоманды, модифицированныйсигналами с группы выходов 56 регистра20 операнда.Считывание следующей микрокомандыиз блоха 16 управляющей памяти осуществляется аналогично по приходу очередного тактового импульса на вход 33блока 4 управления. При этом к моментуначала ее считывания в регистре 1 7 все гда будет установлен адрес предшествовавшей ей микрокоманды.Если блок 23 контроля обнаружит иска.жения в считанной микрокоманде, то сигнал на его выходе 59 принимает нулевоезначение, вследствие чего запрещаетсяформирование сигналов на выходах 44и 39 блока 4 управления. Поэтому выдача этой мйкрокоманды через коммутатор 1 5 не произойдет, на регистре 2 останется записанным ее адрес, а на регистре 22 будет установлен адрес предшествовавшей ей микрокоманды. Поэтому в следующем такте вновь произой13 10087 дет считывание и контроль той микрокоманды, в которой было обнаружено искажение. Если при этом искажений в ней небудет обнаружено, то сигнал на выходе 59 блока 23 контроля принимает единич-ное значение, на выходе 39 блока 4 управления формируется сигнал, по которо.му через коммутатор 15 из регистра 21на регистр 2 подается адрес следующеймккрокоманды, а на арифметический 0блок 19 сигналы микроопераций, Одновременно разрешается формирование в последующих тактах сигнала на выходе 44блока 4 управления. Таким образом восста.навливается нормальный режим считывания мнкрокоманд, описанный выше.Если же при повторном считывании микрокомандьт:в ней вновь будут обнаруженыискаженця, то ее считывание повторяется. Как только количество повторений 29превысит значение, заданное в блоке 23контроля и позволяющее сделать выводо том, что причиной искажений мнкроко,манды является не сбой, а устойчивыйотказ в блохе 16 управляющей памяти, 25то микрокоманда бракуется, и устройствопереходит в режим восстановления, в хотором осуществляется восстановлениезабракованной микрокоманды в блоке 16 управляющей памяти путем переписи еев свободную ячейку этого блока из блока 6 основной памяти. При этом на выходе 62 блока 23 контроли формируетсяимпульсный единичный сигнал, на его выходах 59 и 63 - постоянные единичныеЗ 5сигналы, а сигнал на вцходе 60 принимаетнулевое значение. По сигналу с выхода 62блоха 23 контроля адрес искаженной микрокоманды подается из регистра 2 в блок3 формирования адреса который по этому .адресу формиру адрес соответствующей ячейки блока 6 основной памяти. Нулевым значением на выходе 60 блока 23контроля в коммутаторе 15 запрещаетсяподача информации из регистра 21 микро.команд на арифметический блок 19 и на45регистр 2 адреса микрокоманд, а такжеиз блока 6 основной памяти на арифметический блок 19. По сигналу с выхода63 блок 23 запрещается формирование ситъналов на выходах 40, 39, 44 блока 4управления. Устройство переходит в режим восстановления.При поступлении очередного импульса навход 33 блок 4 управления формирует сигнал ца выходе 35, по которому коммутатор 5515 подключает группу входов 45 к группевыходов 50, образуя цепь для подачи информации из блока 6. основной памяти на 41 . 14группу информационных входов 52 блока16 управляющей памяти. Одновременноформируется сигнал на выходе 36 блока4 управления, по которому из блока 6 .основной памяти по адресу, поступившемуна его группу выходов 25 через. буферныйрегистр 5 с группы выходов 27 блока 3формирования адреса, считывается неискаженное значение микрокоманды, Этамикрокоманда поступает на группу информационных входов 52 блока 16 управляющей памяти и на группу входов блока 23 контроля, который стробируетсясигналом с выхода 36 блока 4 управленияи осуществляет контроль переписываемоймихрокоманды. Одновременно в регистр2 через группу выходов 28 блока 3формирования адреса записывается адресячейки блока 16 управляющей памяти, следующей за последней занятой ячейкой иявляющейся свободной, Згот адрес былсформирован по окончании режима переписи. Из регистра 2 через блок элементовИ 8 адрес подается на группуадресныхвходов 53 блока 16 управляющей памяти.При поступлении очередного тактового импульса на выходе 41 блока 4 управления формируется сигнал, по которомуосуществляется запись считанной микрокомаидыв свободную ячейку блока 16управляющей памяти,При поступлении следующего тактовогоимпульса на выходах 41 и 42 блока 4 управления формируются сигналы, .по которымосуществляется изменение адресной части в микрокоманде, которая предшествуетискаженной, При этом в нее вместо адреса искаженной микрокоманды из регистра2 записывается адрес той ячейки, в которой теперь хранится неискаженное значение переписываемой микрокоманды.Тем самым обеспечивается обход отказав -шей ячейки блока 16 управляющей памяти при возможном повторном выполнении микропрограммы. При этом по сигналу на выходе 42 блока 4 управления за пирается блок элементов И 8 и отпираются блоки элементов И 7.и 10, Черезблок элементов И 7 из регистра 2 нагруппу информационных входов 52 блока16 управляющей памяти подается новоезначение изменяемой адресной части,Адрес, по которому производится записьинформации, поступает на группу адреных входов 53 через блок элементовИ 10 из регистра 22,Если при переписи в микрокомандене было обнаружено искажени, то сигналы навыходахблока," 23 контроля ос

СмотретьЗаявка

3268673, 10.02.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

БАЙДА НИКОЛАЙ КОНСТАНТИНОВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕВ МИХАИЛ ПАВЛОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, КУРИЛО АНАТОЛИЙ НИКОЛАЕВИЧ, СИДОРЕНКО ВАЛЕНТИН ИВАНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: вычислительное, микропрограммное

Опубликовано: 30.03.1983

Код ссылки

<a href="https://patents.su/17-1008741-mikroprogrammnoe-vychislitelnoe-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное вычислительное устройство</a>

Предыдущий патент: Умножитель частоты следования импульсов

Следующий патент: Микропрограммное устройство управления

Случайный патент: Способ подготовки растительного сырья к извлечению сока