Устройство для суммирования фибоначчиево-десятичных кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 945862

Авторы: Баженов, Кремез, Москаленко, Роздобара, Фомин

Текст

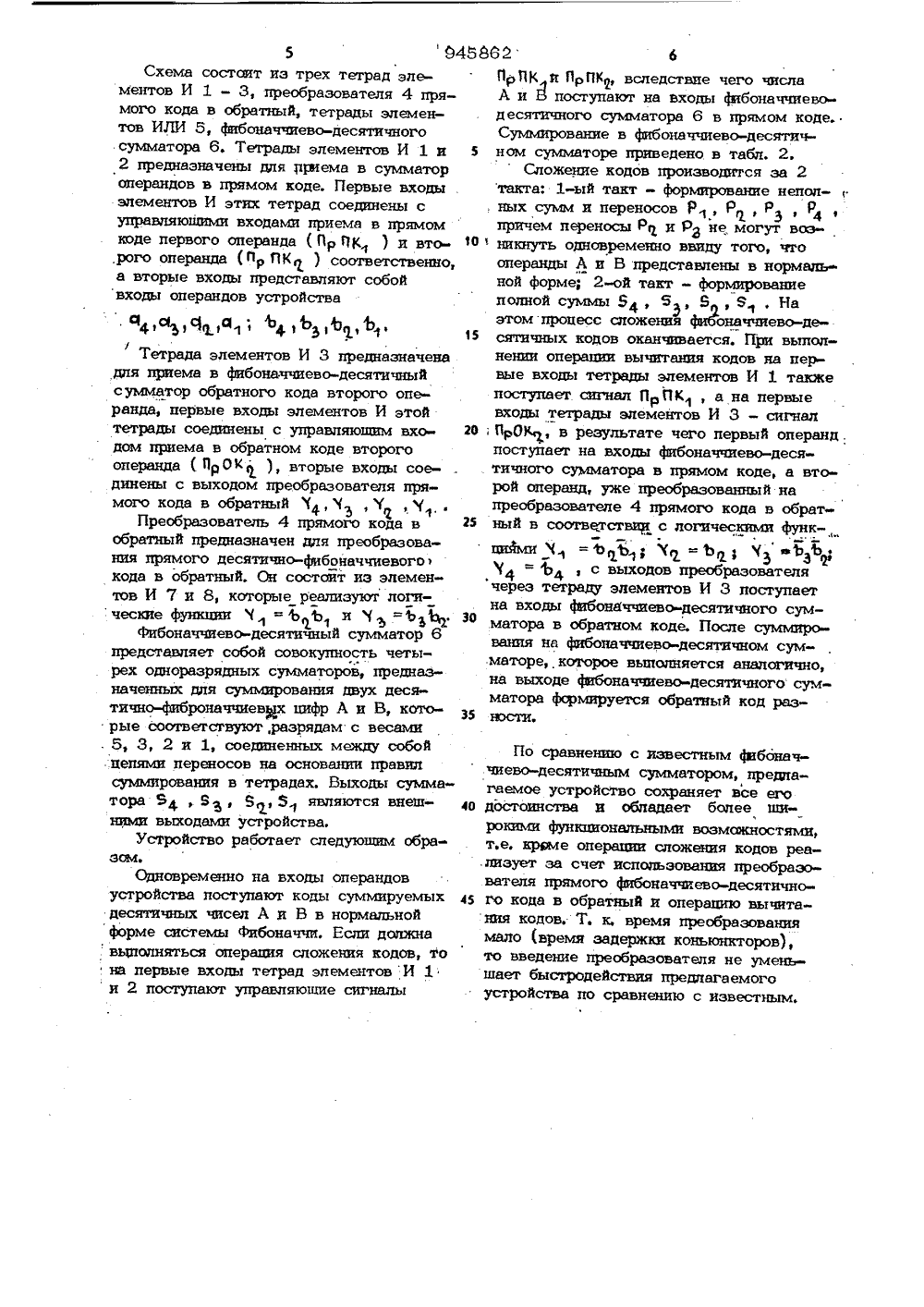

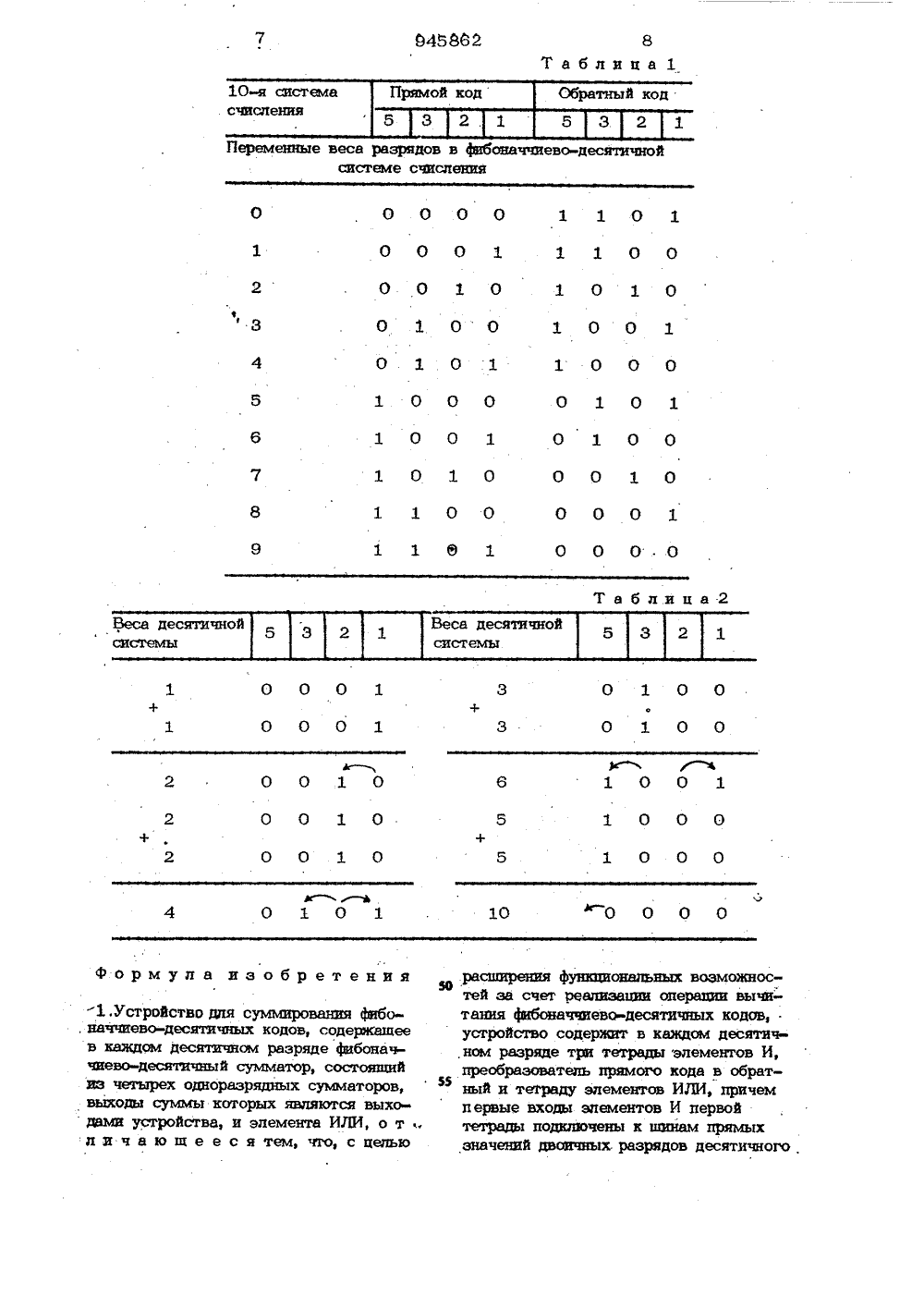

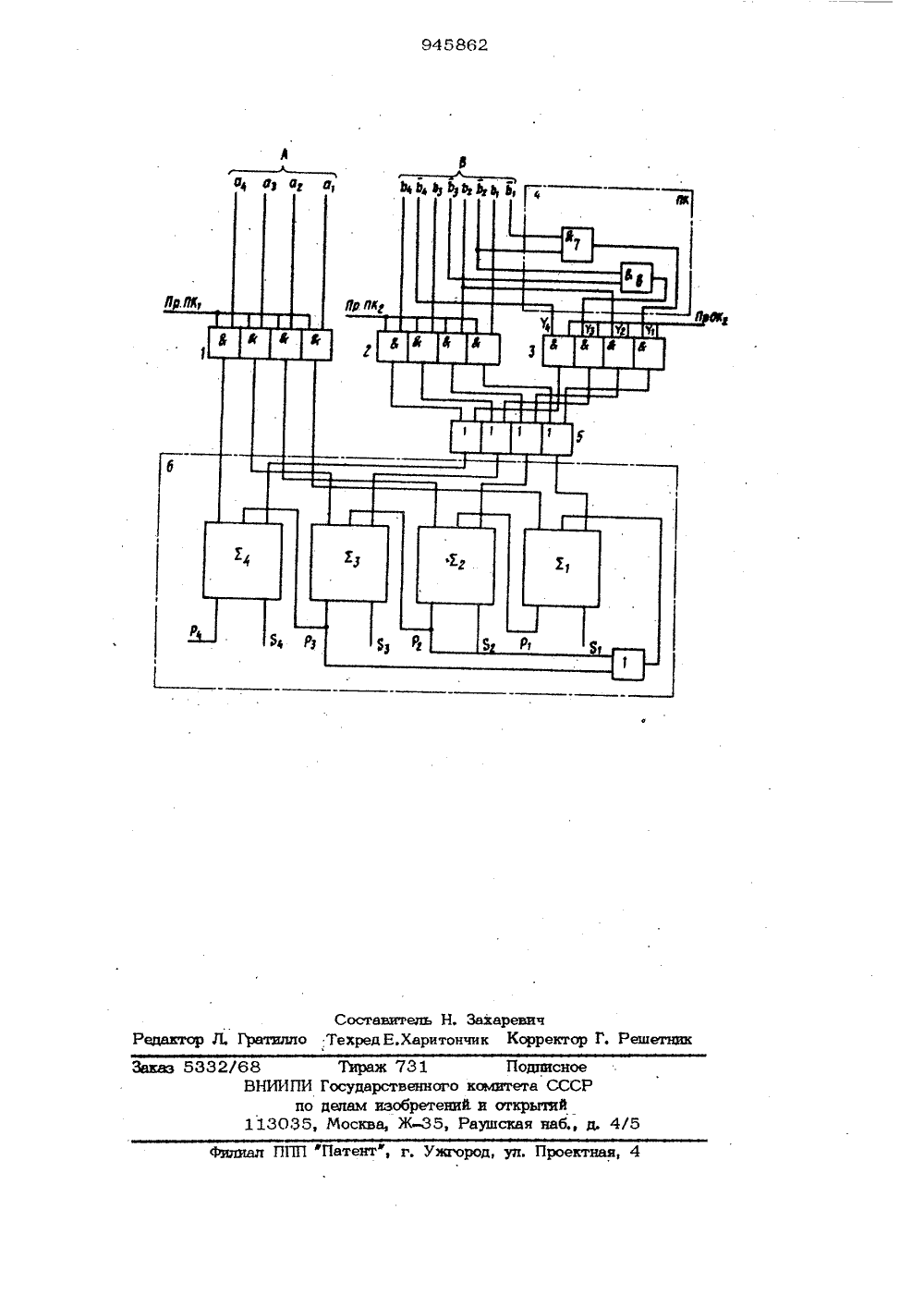

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик(22) Заявлено 27.01.81(21) 3241673/18-24 с присоединением заявки М 9 кудврствне 4 кеатвт ФФФР вв йвави взевретеввйвтврмтвй(72) Авторы изобретения 7) Заявител 54) УСТРОИСТВО ДЛЯ СУММИРОВАНИЯ ФИБОНАЧЧИЕВО-ДЕСЯТИЧНЫХ КОД котороепию резульОднакося такие н вить коррекнтся к вычислнтельыть испоньэс вычислительных дпя сложения ьчисел, содержащее оединенных в коль оичш-десятичных -триггеров, элев И, элементов йстве сохраняютак необходимость использование особностью обк предлагаемомуспоженав ттдесятичных ятдставлеютя квж В таких устройствак цтж сумъвтрованиндвух десятичных цифр, сумма которыхе 10, полученный код необходиморректировать прибавлением к немуаспа 6. Это ведет к усложнениюработоя сумматора, к умего быстродействия. Кроме того,ком устройстве нспопьзуется двоесистема счисления, облвдакецая нулевойспособностью обнаружения ошибкиИзвестно также устройство дпя сложения и вычитании десятичных чисел,испотцззуется фисчисления, обпвдаюеостью обнаружениякоррекция резульботтьшко управ" еньшениюв тачнвя уО тата спожени Недостати ся то юуо он циональные в Цепью изоб ние функатого устройствимеет огрвниченнь жностйе ленин является расцтнреайсностей устрой- операции вы егаичных кодов. внальиых вм реапизашзиево-д асят Изобретение относной технике н может бв специализированныхмаши пахеИзвестно устройстворазрядных десятичныхп последовательно сцо шинами переноса двтетрад сумматоров, Дментов ИЛИ, элементозадержки 1,позволяет осущтата за одинв этом устроедостатки, кррекции результата нкода, не обладающего спружения оптнбкие Наиболее близким является устройство дпя разрядных ибоначчиевосел, в котором дпя предой десятичной цифры боначчиевая система щая нулевой способн апнбки и исключаетсяом э о3 04Поставленная цель достигается тем, что устройство дпя суммирования фибоначчиево-десятичных кодов, содержащее в каждом десятичном разряде фибоначчиеводесятичный сумматор, состоящий из четырех одноразрядных сумматоров, выходы суммы которых являются выходами устройства и элемента ИЛИ, содержит в каждом десятичном разряде три тетрады элементов И, треобразователь прямого кода в обратный и тетраду элементов ИЛИ, причем первые входы элементов И первой тетрады подключены к шинам прямых значений двоичных разрядов десятичного разряда первого операнда устройства, вторые входы элементов И первой тетрады подключены к управляющему входу приема в прямом коде первого операнда устройства, а выходы элементов И первой тетрады подключены к соответствуюнцм первым входам одноразрядных сумматоров, первые входы элементов И второй тетрады подключены к шинам прямых значений двоичных разрядов десятичного разряда второго операнда устройства, вторые входы элементов И второй тетрады подкпючены к управляющему входу приема в прямом коде второго операнда устройства, первый вход преобразователя прямого кода в обратный подключен к шине инверсного значения первого двоичного разряда десятичного разряда второго операнда устройства, второй и третий входыпреобразователя прямого кода в сбратный подключены к шине инверсного значения второго двоичного разряда десятичного разряда второго операнда устройства, четвертый вход преобразователя прямого кода в обратный подключен к шине инверсного значения третьего двоичного разряда десятичного разряда второго операнда устройства, первый вход первого .элемента И третьей тетрады подключен к первому выходу преобразователя прямого кода в обратный, первый вход второго элемента И третьей тетрады соединен с первым входом второго элемента И второй тзтрады, первый вход третьего элемента И третьей тетрады подключен к второму выходу преобразователя прямого кода в обратный, первый вход четвертого элемента И третьей тетрады подкпючен к шине инверсного значения четвертого двоичного разряда десятичного разряда второго операнда устройства, вторые входы элементов И третьей тетрады подключены к управляющему входу приема в обратном коде второго операнда устЬй 62 а Ч Ь, Ь 1 ч,:ю," 3 1 4= Ь 4На основании этих выражений строится преобразователь кода каждой десятич,ной цифры. Очевидно, что при преобра зовании обратного кода в прямой логичеокие функции, реализуемые преобразователем, останутся прежними, т.е. преобразователь может быть испопьзован и дляпреобразоцания из обратного кода в пря-мой..На чертеже приведена функциональнаясхема одного десятичного разряда устрой- ствяе ройства, выходы элементов И третьейтетрады подключены к первым входамсоответствующих элементов тетрадыэлементов ИЛИ, вторые входы которыхподключены к выходам элементов И второй тетрады, а выходы элементов ИЛИтетрады подключены к вторым входамсоответствующих одноразрядных сумматоров, а также тем, что преобразователь 10 прямого кода в обратный состоит издвух элементов И, причем первый и второйвходы первого элемента И подключены кпервому и второму входам преобразователя соответственно, а выход первого эле 1 з мента И подключен к первому выходупребразователя, первый и второй входывторого элемента И подключены к третьему и четвертому входам преобразователя соответственно, а выход второго эле мента И подключен к второму выходупреобразователя прямого кода в обратный.Реализация операции вычитания фнбоначчиево-десятичных кодов обеспечивает- а ся путем преобразования вычитаемого( Ьд, Ь , Ь, Ь ), в обратный фибоначчиево-десятичный код. Обратный кодобразуется дополнением каждой десятичной цифры до девятки. Логические функЗ 0 цни, реализуемые преобразователем, определяются из табл. 1.Учитывая, что прямые коды поступиют на вход преобразователя только внормальной форме, т.е, других кодовыхкомбинаций помимо перечисленных втаблице в графе фПрямой кодф на входепреобразователя быть не может, на основании таблицы выражаем У. 1 У4 как функции 4 ф Ъ ф14004 ВМ 2 8Таблица 1 Обратный код Прямой код 10-я система. счисления 5 3 2 . 1 5 3 2 1 Переменные веса разрядов в фбоначчиево-десятичной системе счисления О 0 0 0 0 О 0 1 О 0 1 0 О Ф3 0 1 0 0 0 1 0 1 1 0 0 О 1 0 0 1 1 О 1 0 1 1 0 0 1 1 6 1 Таблнпа 2 Веса десятичной 5 3 2 1 Веса десятичной 5 3 2системы системы 0 1 О 0 О 0 1 0 0+2 0 1 0 1 0 0 0 0 Юрасширения функциональных возможностей за счет реализации операции вы щ- тания фнбоначжево-десятичных кодов, устройство содерзат в каждом десятич,ном разряде три тетрады элементов И, преобразователь прямого кода в обратный и тетраду элементов ИЛИ, причем первые входы элементов И первой тетрады подключены к панам прямых значений двоичных разрядов десятичного,Формула из обр ет ения-1.Устройство для суммирования або, наччиево-десятичных кодов, содеркащее в каждом десятичном разряде фибоначчиево-десятичный сумматор, состоящий из четырех одноразрядных сумматоров, выходы суммы которых являются выхо двми устройстве, и элемента ИЛИ, о т ., личающеесятем, что, сцелью 1 1 0 1 1 1 0 0 1 О 1 0 1 0 О 1 1 0 0 О 0 1 0 1 0 1 0 0 0 0 1 0 О 0 0 1 0 0 О 09 04 разряда первого операнда устройства, вторые входы элементов И первой тетрады подключены к управляющему. входу приема в прямом коде первого операнда устройства, выходы элементов И первой тетради подключены к первым входам соотвегствуюших одноразрядных сумм торов, первые входы элементов И второй тетрады подключены к шинам прямых значений двоичных разрядов десятичного разряда второго операнда устройства, вторые входы элементов И второй тетрады подключены к управляющему входу приема в прямом коде второго операнда устройства, первый вход преобразователя прямого кода в обратный подключен к шине инверсна о значения первого двоичного разряда десяти щого разряда второго операнда устройства, второй и третий входы преобразователя прямого кода в обратный подюпочены к шине инверсного значения второго двоичного разряда десятичного разряда второго операнда устройства, четвертый вход преобразователя прямого кода в обратныйдключен к шине инверсного значения третьего двоичного разряда десятичногоРазряда второго операнда устройства, первый вход первого элемента И третьей тетрады подключен к первому выходу преобразоватепг прямого кода в обратный, первый вход второго элемента И трегьей тетрады соединен с первым входом второго элемента И второй тетрады первый вход третьего элемента И третьей тетради подключен ко второму выходу преобразователя прямао кода в обратный, первый вход четвертсго элемента И третьей тетрады подюпочен к шине Вйй 2. 10инверсного значения четвертого двоичного разряда десятичного разряда второго операнда устройства, вторые входы элементов И третьей тетрады подключ ны к управляющему входу приема в обратном коде второго операнда устройства, выходы элементов И третьей тетрады п(щключены к первым входам соответствующих элементов ИЛИ тетрады, вторые входы-которых подключены к выходам элементов И второй тетрады, а выходы элементов ИЛИ тетрады подключены к вторым входам соответствуюших одноразрядных сумматоров.2, Устройствопо п. 1, отличаю щ е е с я тек, что, преобразователь прямого кода в обратный состсвт иэ двух элементов И, причем первый и вто.рой входы первого элемента И подключе.ны к первому и второму входам преобразователя соответственно, а выход первого элемента И подключен к первому выходу преобразователя, первый и второй входы второго элемента И подключены к третьему и четвертсму входам преоб- .разователя соотвегственио, наход второго элемента И подключен к втораму выходу преобраэоаатещ прямого кода в обратный. 30Источиппа информащщ,принятые во внимание щв эксяертиэе1. Акнепторная заявка ЯпонииМ 82-38367, кл. й 06 Р 7/388, 1977,2. Авторское свидетельство СССР% 488206, зл. 9 06 Р 7/49, 1978.3. Авторское свидетельство СССРМ 662931, кл, 506 Р 8/00, 1976Ьр.945862 э фю аа Составитель Н. Захаревич Гратилло Техред Е.Харитончнк Корректор Г. РешПодписноеого комитета СССРретений и открьгщй5, Раушская наб., д, 4/ филиал ППП Патент", г. Ужгород, ул. Проектная, 4 332/68 Тираж 731 ВНИИ ПИ Государственн по делам иэоб 113035, Москва, Ж5

СмотретьЗаявка

3241673, 27.01.1981

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

БАЖЕНОВ ЮРИЙ МИХАЙЛОВИЧ, КРЕМЕЗ ГЕОРГИЙ ВАЛЬТЕРОВИЧ, МОСКАЛЕНКО АЛЕКСАНДР ИВАНОВИЧ, РОЗДОБАРА ВИТАЛИЙ ВЛАДИМИРОВИЧ, ФОМИН АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/49

Метки: кодов, суммирования, фибоначчиево-десятичных

Опубликовано: 23.07.1982

Код ссылки

<a href="https://patents.su/6-945862-ustrojjstvo-dlya-summirovaniya-fibonachchievo-desyatichnykh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования фибоначчиево-десятичных кодов</a>

Предыдущий патент: Многофункциональный логический модуль

Следующий патент: Генератор одномерных дискретных случайных блужданий

Случайный патент: Способ механического анализа почв и грунтов