Устройство для прямого преобразования чисел из кода системы остаточных классов в полиадический код и обратно

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1817246

Автор: Литвинов

Текст

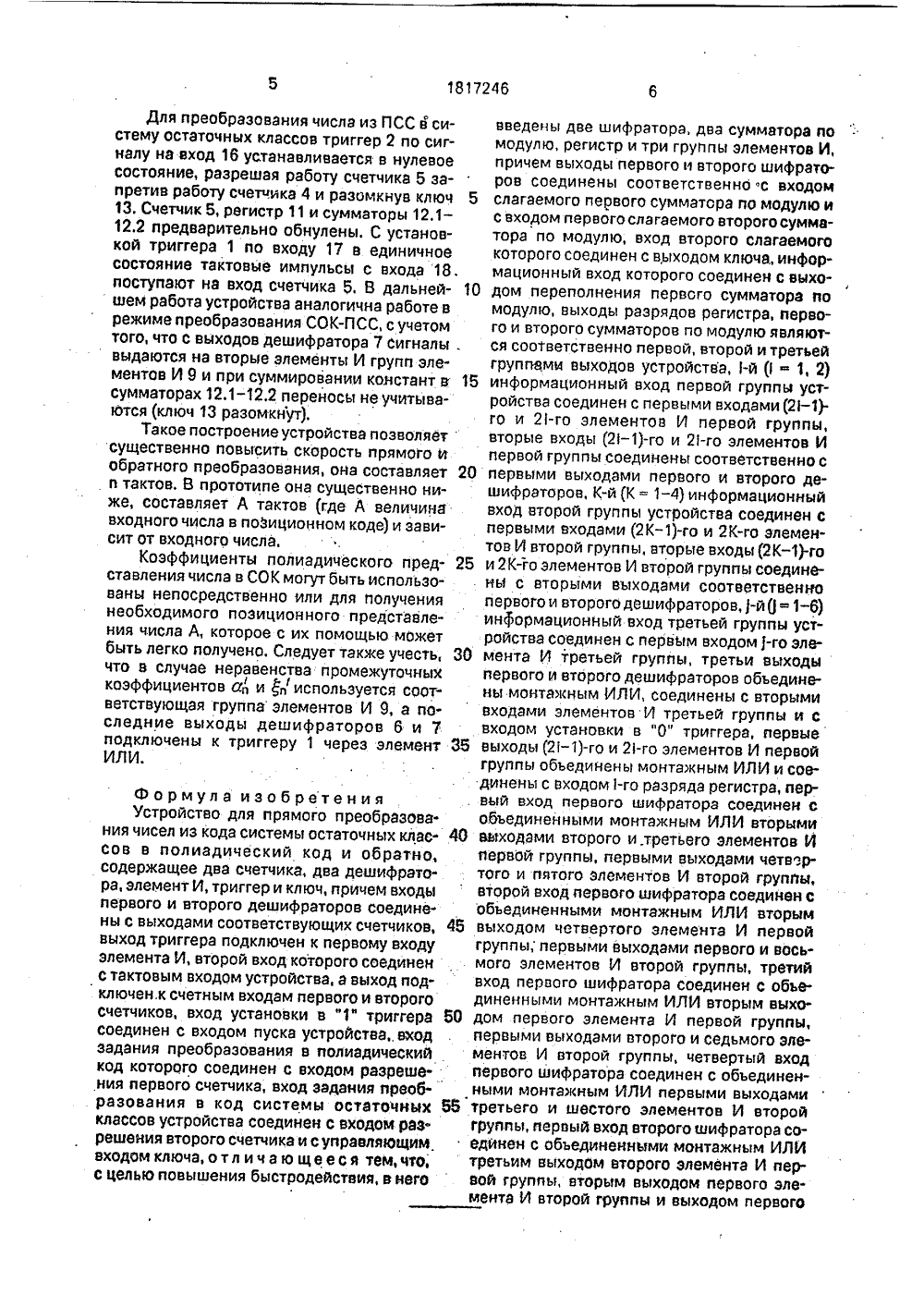

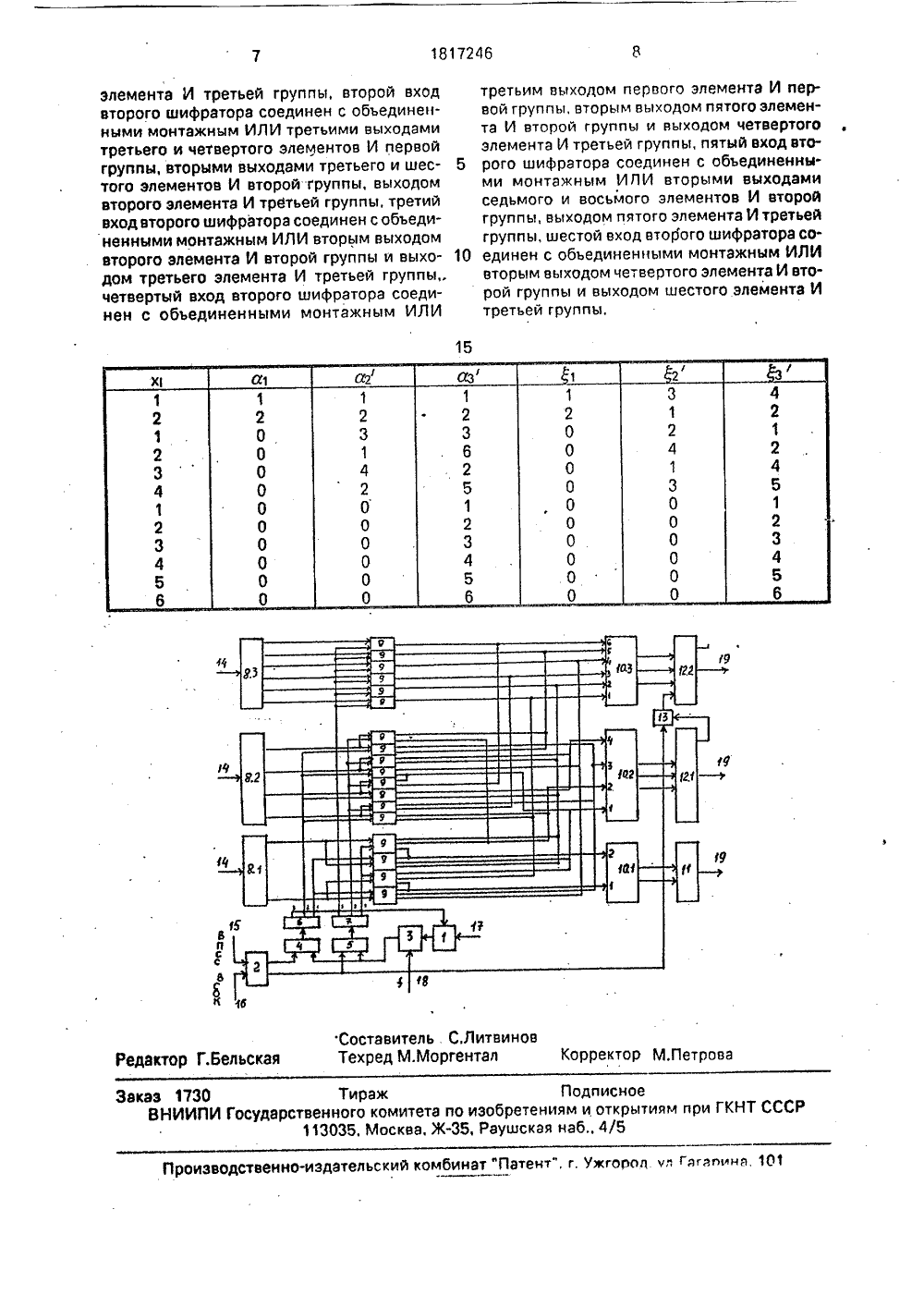

(19) .03 М 7/18 ГОСУДАРСТВЕННОЕ ПАТЕНТНОВЕДОМСТВО СССР(ГОСПАТЕНТ СССР) ОЛИСАНИЕ ИЗОБРЕТЕНК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ НИЯ Р 1, счислен как А" для нах знание предстаОбо разован вПССп.0 обР Р 1 Х Р 2 Х. озффициентыф пония чисел х можно редставления чисанием, Аналогично Очевидно, что лиадического пре найти козффицие ла А в ПСС их сум зная кдставленты имиров ния устройстваипы,(21) 4779924/24(56) Авторское свидетельство СССРМ 1141398, кл. Н 03 М 7/18, 1983,Авторское свидетельство СССРЬ 1089573, кл. Н 03 М 7/18, 1983.(54) УСТРОЙСТВО ДЛЯ ПРЯМОГО ПРЕОБРАЗОВАНИЯ ЧИСЕЛ ИЗ КОДА СИСТЕМЬОСТАТОЧНЫХ КЛАССОВ В ПОЛИАДИЧЕСКИЙ КОД И ОБРАТНО Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для перевода чисел из полиадической системы счисления (ПСС) в систему остаточных классов(СОК) и обратно,Цель изобретения - повышение быстродействия устройства.На чертеже приведена функциональная схема устройства в предположении, что основания СОК равны р 1= 3, р 2 = 5, рз".7.Устройство для прямого и обратного преобразования чисел из кода системы остаточных классов в полиадический код содержит триггеры 1-2, элемент И 3, счетчики 4-5, дешифраторы 6-7, входные регистры 8.1-8.3, группы элементов И 9, шифраторы 10.1-10.3, дополнительный регистр 11, сумматоры 12,1-12.2 по модулям, ключ 13 информационные входы 14 устройства, управляющие входы 15-16, вход пуска 17, тактовый вход 18 и выходы 19 устройства.В основу функционироваположены следующие принц(57) Изобретение относится к вычислительной технике и может бьть использовано для реверсивного преобразования чисел иэ полиадической системы счисления в систему остаточных классов. Целью изобретения является повышение быстродействия, Устрой- ство содержит счетчики, дешифраторы, элемент И, триггер, шифраторы, сумматоры по модулю, регистр и три группы элементов И, 1 ил. 1 табл,ОК число А представляется остаткаа 2 ап)отделения егонаосноваР 2-, рп. В полиадической системе ия, то же число. А представляется Ь+ ЬР 1+4 ЗР 1 Р 2+ ". + ПР 1 Р 2.-Рп, т.Е. ождения числа в ПСС необходимо коэффициентов ф полиадического вления этого числа.значим х =а =ф тогда для преоб. ия числа А (а 1, а а ) иэ СОК редставим его в следующем виде:рассуждай получаем для преобразованиячисла А из ПСС в СОК.+(О, О, .,О, /хпр 1 Р 2, ", Рп/Рп),Пусть Р 1 = 3, р 2 = 5, рз = 7 построим для "0данной системы таблицу промежуточных.значений ф и а определяемых по входнымзначениям хьПокажем на примерах для выбраннойсистемы оснований данный метод преобра- "5зования чисел,. П р и м е р 1, А = 32 = (2, 2, 4) СОКЬ Ь эа 1=2 2 1 2 20а=2+04 . 2аз 4 0 О 42 0 81 перенос учитываетсяф= 2 О 225М перенос не учитываетсяПроверка показывает, что А =ф 1+ф 2 Р 1+ 30+ фзр 1 Р 2 = 2 + О. 3 + 235 = 32,Пример 2.А = 95 = (2, 1, 6) ПССа 1 а 2 С 355=2 2 2 2В=2 О 3 3фз= 6 0 0 62 0 11перенос неучитывается 40а = 2 О 41 перенос не учитываетсяДействительно, А =95 =(2, О, 4) в СОК, Устройство для прямого и обратного преобразования чисел кода СОК в полиади- .ческий код работает следующим образом,В исходном состоянии счетчики 4 и 5 регистр 11 и сумматоры 12,1-12.2 (модульные, накапливающие) обнулены, триггер.1 также в нулевом состоянии.В режиме преобразования в полиадиче ский код сигнал подается на вход 15, который устанавливает триггер 2 в единичное состояние разрешая Работу счетчика 4, запретив работу счетчика 5, замкнув ключ 13. Остатки числа в СОК подлежащего преобразованию, в унитарном коде по входам 14 подаются в регистры 2,1 - 2.3. С приходом единичного сигнала на вход 17, триггер 1 устанавливается в единичное состояние разрешая прохождение тактовых импульсов с входа 18 черезэлемент И 3 на вход счетчика 4. С каждым тактовым импульсом счетчик 4 изменяет свое состояние на единицу, на выходах соединенного с ним дешифратора 6 появляются импульсы поступающие на управляющие входы соответствующих групп элементов И 9, (Причем элемент И 1-ой группы элементов И 9 имеет(и+1-) выходов, т.е. может быть выполнен на базе п двух входовых элементов И, входы которых объединены.) С приходом первого импульса по первому остатку записанному в регистре 8.1 с выходов элементов И 9 первой группы поступят сигналы на шифраторы 10,1 - 10.3, с выходов которых цифровые значения промежуточных констант записываются в дополнительный регистр 11 и сумматоры 12.1 - 12.2. С приходом второго импульса, появится сигнал на втором выходе дешифратора 6, который поступит на управляющие входы второй группы элементов И 9. На первых входах второй группы элементов И 9 присутствует сигнал с регистра 8,2, а сигнал с выходов элементов И 9 второй группы поступит на входы шифраторов 10,2 - 10,3, с выходов которых соответствующие значения запишутся в сумматоры 12,1-12.2 т,к, а 1 = 1. При этом если на выходе сумматора 12,1 сформировался перенос, то он поступит на второй вход сумматора 12.2 т.к. ключ 13 замкнут, С приходом 3-го импульса с 3-го выхода дешифратора 6 сигнал поступит на управляющие входы третьей группы элементов И 9, с выходов которых в соответствии с кодом остатка в регистре 8,3 выдается сигнал на шифратор 10.3, По этому импульсу в сумматор 12.2 записывается последняя константа (перенос этого сумматора не учитывается) т,е. преобразование закончено, получены все коэффициенты полиадицеского представления входного числа в СОК поступающие на "выход 19, С последнего выхода дешифратора 6 сигнал подается также на нулевой вход триггера 1 (в необходимых случаях через элемент задержки) установив его в нулевое состояние и запретив прохождение тактовых импульсов по входу 18, Перед очередным циклом преобразования из СОК в ПСС обнуляются регистр 11, сумматоры 12,1-12.2 и счетчик 4 (цепи не показаны). После записи очередных остатков в регистры 8.1-8.3 оно может быть продолжено.1817246Для преобразования числа из ПСС в си- введены две шифратора, два сумматора по стему остаточных классов триггер 2 по сиг- модулю, регистр и три группы элементов И, налу на вход 16 устанавливается в нулевое причем выходы первого и второго шифратосостояние, разрешая работу счетчика 5 за- ров соединены соответственно с входом претив работу счетчика 4 и разомкнув ключ 5 слагаемого первого сумматора по модулю и 13. Счетчик 5, регистр 11 и сумматоры 12,1- с входом первого слагаемого второгосумма,2 предварительно обнулены. С установ- тора по модулю, вход второго слагаемого кой триггера 1 по входу 17 в единичное которогосоединенсвыходомключаинфорсостояние тактовые импульсы с входа 18, мационный вход которого соединен с выхопоступают на вход счетчика 5. В дальней дом переполнения первого сумматора по шем работа устройства аналогична работе в модулю, выходы разрядов регистра, перво- режиме преобразования СОК-ПСС, с учетом го и второго сумматоров по модулю являют- того, что с выходов дешифратора 7 сигналы . ся соответственно первой, второй и третьей вцдаются на вторые элементы И групп эле- группами выходов устройства, -й 0 1, 2) ментов И 9 и при суммировании констант в 15 информационный вход первой группы устсумматорах 12,1-12.2 переносы не учитыва- ройства соединен с первыми входами(21-1)- ются(ключ 13 разомкнут), го и 21-го элементов И первой группы,Такое построениеустройства позволяет вторые входы (21 - 1)-го и 21-го элементов И существенно повысить скорость прямого и первой группы соединены соответственно с обратного преобразования, она составляет 20 первыми выходами первого и второго деи тактов, В прототипе она существенно ни- шифраторов, К-й (К = 1-4) информационный же, составляет А тактов (где А величина вход второй группы устройства соединен с входного числа в позиционном коде) и зави- первыми входами (2 К)-го и 2 К-го элеменсит от входного числа тов И второй группы, вторые входы(2 К)-гоКоэффициенты полиадического пред и 2 К=гоэлементовИ второйгруппысоединеставления числа в СОК могут быть использо- ньяи с вторыми въаодами соответственно ваны непосредственно или для получения первого и второго дешифраторов,3-й 0 =1-6) необходимого позиционного представле- информационный вход третьей группы устния числа А, которое с их помощью может ройства соединен с первым входом 1-го элебцтьлегко получено. Следуеттакжеучесть, 30 мента И третьей группы, третьи выходы что в случае неравенства промежуточных первогоивторогодешифраторовобъедине 5 lкоэффициентов ал и ф используется соот- ны монтажным ИЛИ, соединены с вторыми ветствующая группа элементов И 9, а по- входами элементов И третьей группы и с следние выходы дешифраторов 6 и 7 входом установки в "0" триггера, первые подключены к триггеру 1 через элемент 35 выходы(21-1)-го и 21-го элементов И первой ИЛИ. группы объединены монтажным ИЛИ и соединены с входом Ио разряда регистра, перФормула изобретения . вцй вход первого шифратора соединен с Устройство для прямого преобразова- объединеннь 1 ми монтажным ИЛИ вторыми ния чисел из кода системы остаточных клас аыходами второго и.третьего элементов И сов в полиадический код и обратно, первой группы, первыми выходамичетв.рсодержащее два счетчика, два дешифрато- того и пятого элементов И второй группы, ра, элемент И, триггер и ключ, причем входы: второй вход первого шифратора соединен с первого и второго дешифраторов соедине- объединенными монтажным ИЛИ вторым ны с выходами соответствующих счетчиков, 45 выходом четвертого элемента И первой выход триггера подключен к первому входу группы; первыми выходами первого и вось- элементаИ,второй входкоторогосоединен мого элементов И второй группы, третий с тактовым входом устройства, а выход под- вход первого шифратора соединен с объеключен.к счетным входам первого и второго диненными монтажным ИЛИ вторым выхосчетчиков, вход установки в "1" триггера 50 дом первого элемента И первой группы, соединен с входом пуска устройства, вход . первыми выходами второго и седьмого элезадания преобразования в полиадический ментов И второй группы, четвертый вход код которого соединен с входом разреше- первого шифратора соединен с объединенния первого счетчика, вход задания преоб- ными монтажным ИЛИ первыми выходами разования в код системы остаточных И третьего и шестого элементов И второй классов устройства соединен с входом раз- группы, первый вход второго шифратора сорешения второго счетчика и с управляющим единен с объединенными монтажным ИЛИ входомключа,отличающееся тем,что, третьим выходОм второго элемента И перс цельюповышения быстродействия, внего вой группы, вторым выходом первого элемента И второй группы и выходом первогоЗаказ 1730 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва. Ж, Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г. Ужгооол мл гдглоинв, 101 элемента И третьей группы, второй вход второго шифратора соединен с объединенными монтажным ИЛИ третьими выходами третьего и четвертого элементов И первой группы, вторыми выходами третьего и шестого элементов И второй труппы, выходом второго элемента И третьей группы, третий вход второго шифратора соединен с объединенными монтажным ИЛИ вторым выходом второго элемента И второй группы и выходом третьего элемента И третьей группы четвертый вход второго шифратора соединен с объединенными монтажным ИЛИ третьим выходом первого элемента И первой группы, вторым выходом пятого элемента И второй группы и выходом четвертого элемента И третьей группы, пятый вход вто рого шифратора соединен с объединенными монтажным ИЛИ вторыми выходами седьмого и восьмого элементов И второй группы, выходом пятого элемента И третьей группы, шестой вход второго шифратора со единен с объединенными монтажным ИЛИвторым выходом четвертого элемента И второй группы и выходом шестого элемента И третьей руппы.

СмотретьЗаявка

4779924, 08.01.1990

ВОЙСКОВАЯ ЧАСТЬ 32103

ЛИТВИНОВ СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: H03M 7/18

Метки: классов, код, кода, обратно, остаточных, полиадический, преобразования, прямого, системы, чисел

Опубликовано: 23.05.1993

Код ссылки

<a href="https://patents.su/4-1817246-ustrojjstvo-dlya-pryamogo-preobrazovaniya-chisel-iz-koda-sistemy-ostatochnykh-klassov-v-poliadicheskijj-kod-i-obratno.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для прямого преобразования чисел из кода системы остаточных классов в полиадический код и обратно</a>

Предыдущий патент: Цифроаналоговый преобразователь

Следующий патент: Устройство для контроля дешифраторов

Случайный патент: Газовая холодильная машина