Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

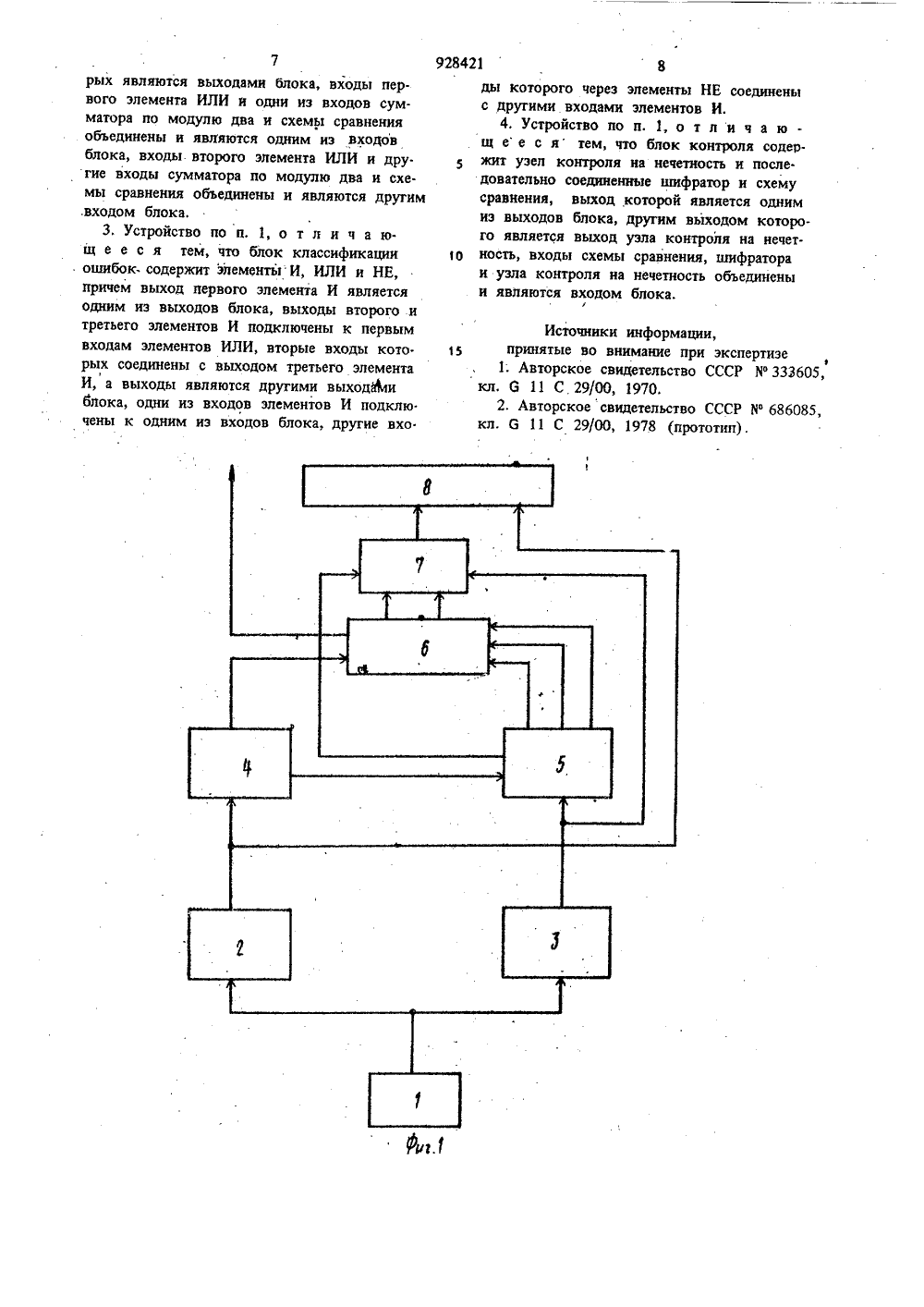

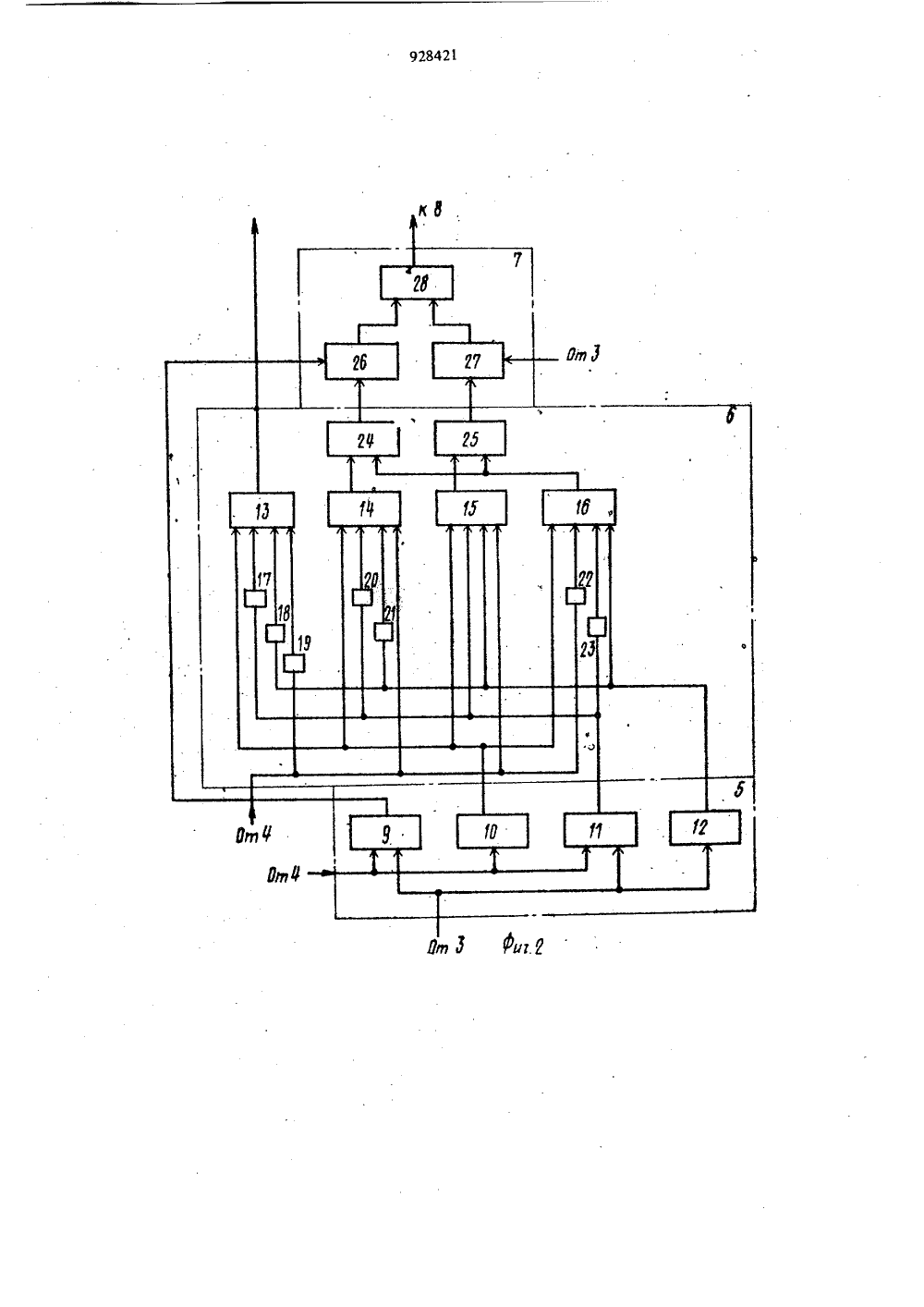

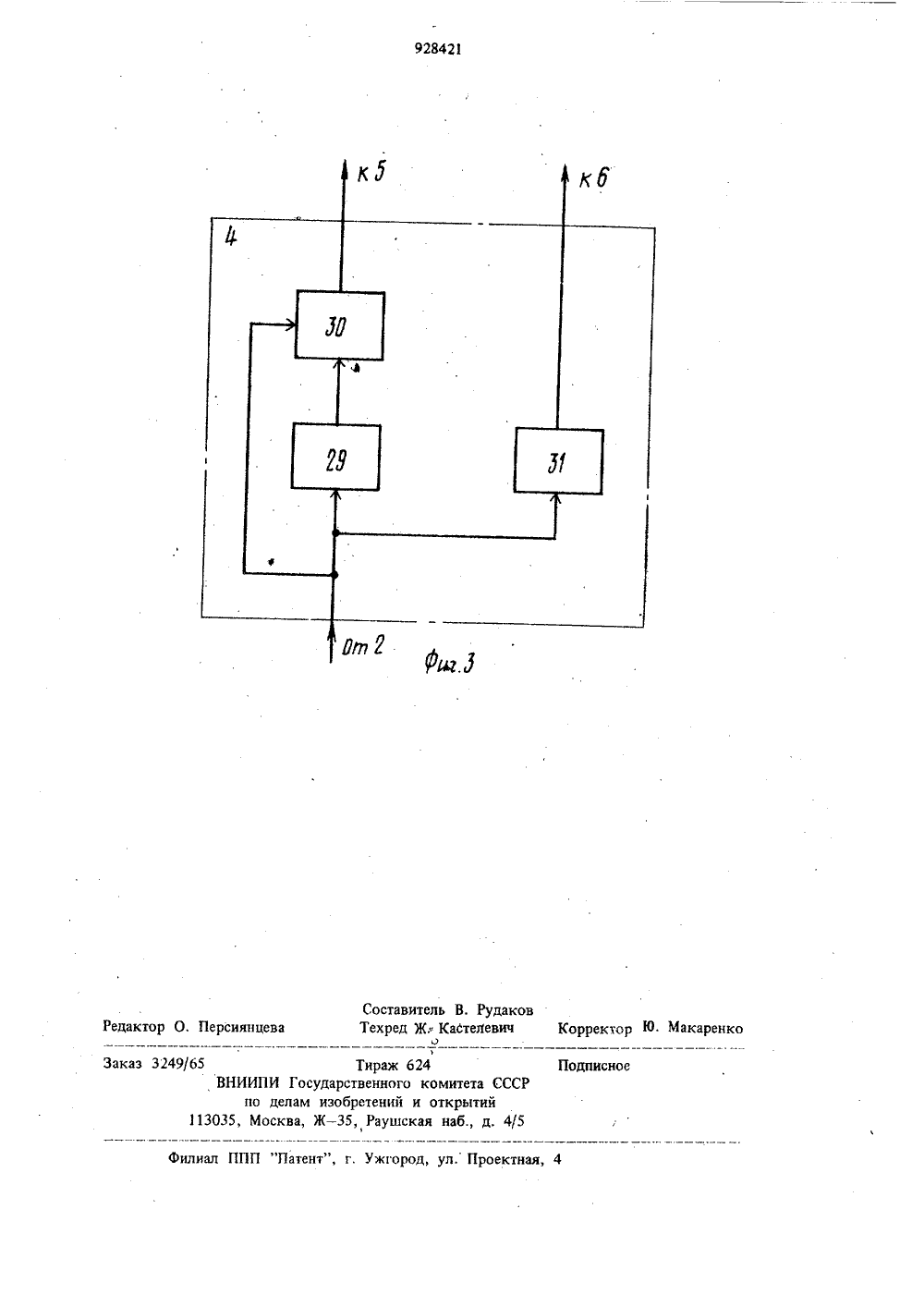

ОП ИКАНИЕИЗОВРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТИЛЬСТ 8 У 1 ц 928421 Союз СоветскихСоциапнстичвскихРеспублик(51)М. Кл. 6 11 С 29/06 Гоеудеретвеяый коиятет СССР ио делаи язебретения я открытейИзобретение относится к запоминающим устройствам.Известно запоминающее устройство с исправлением одиночных ошибок, содержащее блок памяти, соединенный с регистром числа, выполненным на триггерах со счетным входом, и блок контроля, осуществляющий контроль считанной информации по четности 1).Недостатком этого запоминающего устрой 1 о ства является сильное снижение быстродействия эа счет повторных циклов записи и считывания в процессе исправления ошибки.Наиболее близким техническим решением к данному изобретению является запоминаю 15 щее устройство с исправлением ошибок, вызвызванных дефектами накопителя, содержащее основной и дополнительный блоки памя. ти, адресные входы которых соединены с блоком выборки адреса, регистр числа, информационные входы которого соединены с выходами основного блока памяти, а управляю. щие входы - с выходами элементов И, блок контроля, входы которого соединены с выходами основного блока памяти, а вы ходы - с входом регистра числа и входами логических элементов И, дешифратор, входы которого соединены с выходами дополнительного блока памяти, а выходы - с входами ., логических элементов И, Исправление ошибок, вызванных наличием в основном блоке памяти дефектных запоминающих элементов, происходит при воспроизведении информации по сигналу, поступающему нз блока конт. роля путем инвертирования информации в ошибочном разряде регистра числа номер ошибочного разряда хранения в дополнитель.ном блоке памяти 12.Недостатком этого запоминающего устрой. ства является низкая надежность вследствие невозможности обнаружения и исправления ошибок, вызванных эксплуатационными отказами запоминающих элементов.Целью изобретения является повышение надежности запоминающего устройства.Поставленная цель достигается тем, что в запоминающее устройство с исправлением ошибок, содержащее формирователь адрес.40 45 50 55 ных сигналов, выход которого соединен со входами основного и дополнительного накопителей, выходы которых подключены со-. ответственно к первым входам регистра числа и дешифратора, выход которого соединен со вторым, входом регистра числа, введены блок анализа ошибок, блок клас. сификации ошибок и блок контроля, причем входы блока анализа ошибокподключены соответственно к первому выходу блока контроля и выходу дополнительного накопи. теля, а выходы соединены соответственно со вторым входом дешифратора и одним из входов блока классификации ошибок, другой входкоторого подключен к второму выходу блока контроля, вход которого соединен с выходом основного накопителя, первый выход блока классификации ошибок является одним из выходов устройства, а второй и третий выходы соединены соответственно с третьим и четвертым входами дешифратора.При этом блок анализа ошибок целесообразно выполнить в виде блока, содержащего сумматор по модулю,два, эдементы ИЛИ и схему сравнения, выходы которых являются выходами блока, входы первого элемента ИЛИ и одни из входов сумматора по модулю два и схемы сравнения объединены и являются одним из входов блока, входы второго элемента ИЛИ и другие входы сумматора по модулю два и схемы сравнения обьединекы и являются другим входомблока,Блок классификации ошибок целесообразно вьитолнить в виде блока, содержащего элементы И, ИЛИ и НЕ,. причем выход первогоэлемента И является одним из выходов бло.ка,. выходы второго и третьего элементов Иподключены к первым входам элементовИЛИ, вторые входы которых соединены свыходом третьего элемента И, а выходыявляются другими выходами блока, однииз входов элементов И подключены к одним из входов блока, другие входы которого через элементы НЕ соединены с другими входами элементов И.Предпочтительным вариантом выполненияблока контроля является блок, содержащийузел контроля на нечетность и последовательно соединенные шифратор и схему срав.пения, выход которой является одним извыходов блока, другим выходом которогоявляется выход узла копроля на нечетность,входы схемы сравнения, шифратора и узлаконтроля на нечетность объединены и явля.ются входом блока.,На фиг, 1 изображена структурная схемапредложенного запоминающего устройства сисправлением ошибок; на фиг. 2 - частьэтой схемы с детальным раскрытием структу 5 16 15 29 25 30 5 ры дешифратора, блока анализов ошибок иблока классификации ошибок; на фиг, 3 -структурная схема блока контроля.Запоминающее устройство (см. фиг. 1)содержит формирователь 1 адресных сигналов, основной 2 и дополнительный 3 накопители, блок 4 контроля, блок 5 анализаошибок, блок 6 классификации ошибок,дешифратор 7 и регистр 8 числа, Блок 5 содержит (см. фиг, 2) сумматор 9 по модуля,два, элемент ИЛИ 10, схему 11 сравненияи элемент ИЛИ 12. Блок 6 содержит элемен.ы И 13 - 16, элементы НЕ 17 - 23, элементыЛИ 24 и 25. Дешифратор 7 содержит двадополнительных дешифратора 26 и 27 и элемент ИЛИ 28, Блок 4 содержит ем. фиг. 3)шифратор 29, схему 30 сравнения и узел31 контроля на нечетность, При этом накопитель 2 см, фиг. 1) содержит некотороеколичество дефектных запоминающих элементов, но не более одного по каждому адресу.В адресах дефектных запоминающих элементов заранее хранятся коды номеров дефектных разрядов. Накопитель 3 дефектовне имеет,Запоминающее устройство работает следую.щим образом,Формирователь 1 вырабатывает код адреса,который одновременно поступает на адресные входы основного 2 и дополнительного 3накопителей. В основном накопителе 2 хра.нятся коды чисел вместе с контрольнымиразрядамч, например кода Хемминга с минимальным кодовым расстоянием, равнымчетырем,В режиме воспроизведения информации число из основного. накопителя 2 поступает на блок 4 контроля, который формирует синдром, Синдром является номером ошибочного разряда числа при возникновении одиночной ошибки и суммой по модулю два номеров ошибочных разрядов числа - при возникновении двукратной ошибки, Блок 4 контроля формирует также сигнал контроля числа на нечетность.Синдром и код номера дефектного зало. минающего элемента из накопителя 3 поступает в блок 5,Блок 5 вырабатывает сигналы управления в случаях: появления синдрома, не равного "0"; появления кода номера дефектного запоминающего элемента, не равного "О"; появления синдрома, не равного коду номера дефектного запоминающего элемента. Блок 5 производит также суммирование по модулю два синдрома и коды номера дефектногозапоминающего элемента, считанного из накошпеля 3.92842 О 2 О 25 зо 35 40 45 50 55 Управляющие сигналы с блока 5 одновре-менно с сигналом контроля числа на нечетность с блока 4 контроля поступают в дешифратор 7,Код номера дефектного запоминающегоэлемента иэ накопителя 3 и сумма по модулю два этого кода и синдрома из блока 5поступают в дешифратор 7.Если ошибок в числе нет, то на управляющих выходах блока 5 сигналы отсутствуют,т.е. синдром и код номера дефектного запоминающего элемента равны друг другу иравны нулю. При отсутствии управляющихсигналов на этих выходах блока 5 на егоинформационных выходах присутствует нулевой код. Число, поступившее из накопителя2 на регистр 8 числа, готово к выдаче.Если однократная ошибка вызвана отказомзапоминающего элемента в процессе эксплуатации устройства, то на выходах блока 5присутствуют управляющие сигналы, которыеговорят о наличии синдрома, не равного нулю,кода номера дефектного запоминающеФ элемента, равного нулю, и об их неравенстве,При такой комбинации сигналов на управляющих выходах блока 5 на его информационных выходах присутствует код, совпадающийс синдромом, который поступает на входыдешифратора 7. Сигналы с выходов блока 5поступа 1 от на блок 6.Но сигналу с блока 6 сигнал с возбужденного выхода дешифратора 7 поступает навход регистра 8 числа, исправляя ошибку путем инвертирования информации в соответствующем разряде регистра 8 числа.Если однократная ошибка вызвана технологичееким отказом запоминающего элемента,то на выходах блока 5 присутствуют управляющие сигналы, которые говорят о наличиисиндрома кода номера дефектного запоминаю.щего элемента, не равных нулю и об ихравенствеПри такой комбинации сигналов на управляющих выходах блока 5 на первых егоинформационных выходах присутствует код,совпадающий с кодом номера дефектногозапоминающего элемента, Код номера де.фектного запоминающего элемента, считанныйиз накопителя 3, поступает на входы дешифратора 7, минуя блок 5. Сигналы с выходовблока 5 поступают в блок 6. По сигналу сблока 6 сигнал с возбужденного выхода де.шифратора 7 поступает на вход регистра 8числа, исправляя ошибку путем инвертирова-.ния информации в соответствующем разрядерегистра 8 числа.Если двукратная ошибка вызвана эксплуа.тационным и технологическим отказами запоминающих элементов, то на управляющихвыходах блока 5 присутствуют сигналы, ко 1 6торые говорят о наличии синдрома и коданомера дефектного запоминающего элемен.та, не равных нулю, и об их неравенстве.При такой комбинации сигналов на управляющих выходах блока 5 на его информаци.онных выходах присутствует код, являющийся номером того ошибочного разряда числа,ошибка в которой вызвана наличием эксплу.атационного отказа запоминающего элемента.Код с выходов блока 5 и код номера дефектного запоминающего элемента из накопителя 3 поступают на дешифратор 7. Сигналыс блока 6, сигналы с возбужденных выходовдешифратора 7 поступают на входы регистра8 числа, исправляя двукратнУю ошибку путеминвертирования информации в соответствую.ших разрядах регистра 8 числа,Если возникла неисправ 1 ая ошибка, блок6 посылает сигнал на выход устройства,Предлагаемое запоминающее устройство сисправлением ошибок, вызванных дефектаминакопителя и эксплуатационными отказамизапоминающих элементов, отличается отизвестного устро 1 ства тем, чтэ имеет более. высокую надежность за счет исправленияошибок, вызванных эксплуатационнымн откаэами запоминающих элементов. Формула изобретения а1. Запоминающее устройство с исправлением ошибок, содержащее формирователь адресных сигналов, выход которого соединен со входами основного и дополнительного накопителей, выходы которых подключены соответственно к первым входам регистра числа и дешифратора, выход которого соединен со вторым входом регистра числа, о тл и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содер.жнт блок анализа ошибок, блок классификации ошибок и блок контроля, причем входы блока анализа ошибок подключены соответственно к первому выходу блока контроля и выходу дополнительного накопителя, а выходы соединены соответственно со вторым входом дешифратора и одним иэ. входов блока классификации ошибок, другой вход которого подключен к второму выходу блока контроля, вход которого соединен с выходом основного накопителя, первый выход блока классификации ошибок является одним из выходов устройства, а второй и третий вы. ходы соединены соответственно с третьим и четвертым входами дешифратора,2. Устройство по п. 1 о т л и ч а ющ е в с я тем, что блок анализа ошибок содержит сумматор по модулю два, элементы ИЛИ и схему сравнения, выходы кото 7рых являются выходами блока, входы первого элемента ИЛИ и одни из входов сумматора по модулю два и схемы сравненияобъединены и являются одним из входовблока, входы второго элемента ИЛИ и другие входы сумматора по модулю два и схемы сравнения объединены и являются другим,входом блока,3, Устройство по п, 1, о т л и ч а ю.щ е е с я тем, что блок классификацииошибок. содержит элементы И, ИЛИ и НЕ,причем выход первого элемента И являетсяодним из выходов блока, выходы второго итретьего элементов И подключены к первымвходам элементов ИЛИ, вторые входы кото.рых соединены с выходом третьего элементаИ, а выходы являются другими выходамиблока, одни из входов элементов И подклю.чены к одним иэ входов блока, другие вхо. 928421ды которого через элементы НЕ соединеныс другими входами элементов И.4, Устройство по и. 1, о т л и ч а ющ е е с я тем, что блок контроля содер.жит узел контроля на нечеткость и последовательно соединенные шифратор и схемусравнения, выход которой является однимиз выходов блока, другим выходом которого является выход узла контроля на нечето ность, входы схемы сравнения, шифратораи узла контроля на нечетность объединеныи являются входом блока.Источники информации,1 принятые во внимание при экспертизе1; Авторское свидетельство СССР Яф 333605,кл, 6 11 С 29/00, 1970,2. Авторское свидетельство СССР Р 686085,кл. О 11 С 29/00, 1978 прототип).928421 Составитель В, РудаковТехред Ж. Каетелевич Корректор Ю. Макаренко Редактор О. Персиянцева Подписное Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4 Заказ 3249/65 Тираж б 24 ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж - 35, Раушская наб., д. 4/5

СмотретьЗаявка

2883521, 15.02.1980

ПРЕДПРИЯТИЕ ПЯ А-1178

КУЛТЫГИН АНАТОЛИЙ КОНСТАНТИНОВИЧ, ВАРИЕС НИНА ИОСИФОВНА, ВЛАСОВА ГАЛИНА ХРИСАНФОВНА

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 15.05.1982

Код ссылки

<a href="https://patents.su/6-928421-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Аналоговое запоминающее устройство

Следующий патент: Устройство для контроля блоков памяти

Случайный патент: Датчик максимального ускорения