Устройство декодирования для коррекции модулей ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1737515

Автор: Конопелько

Текст

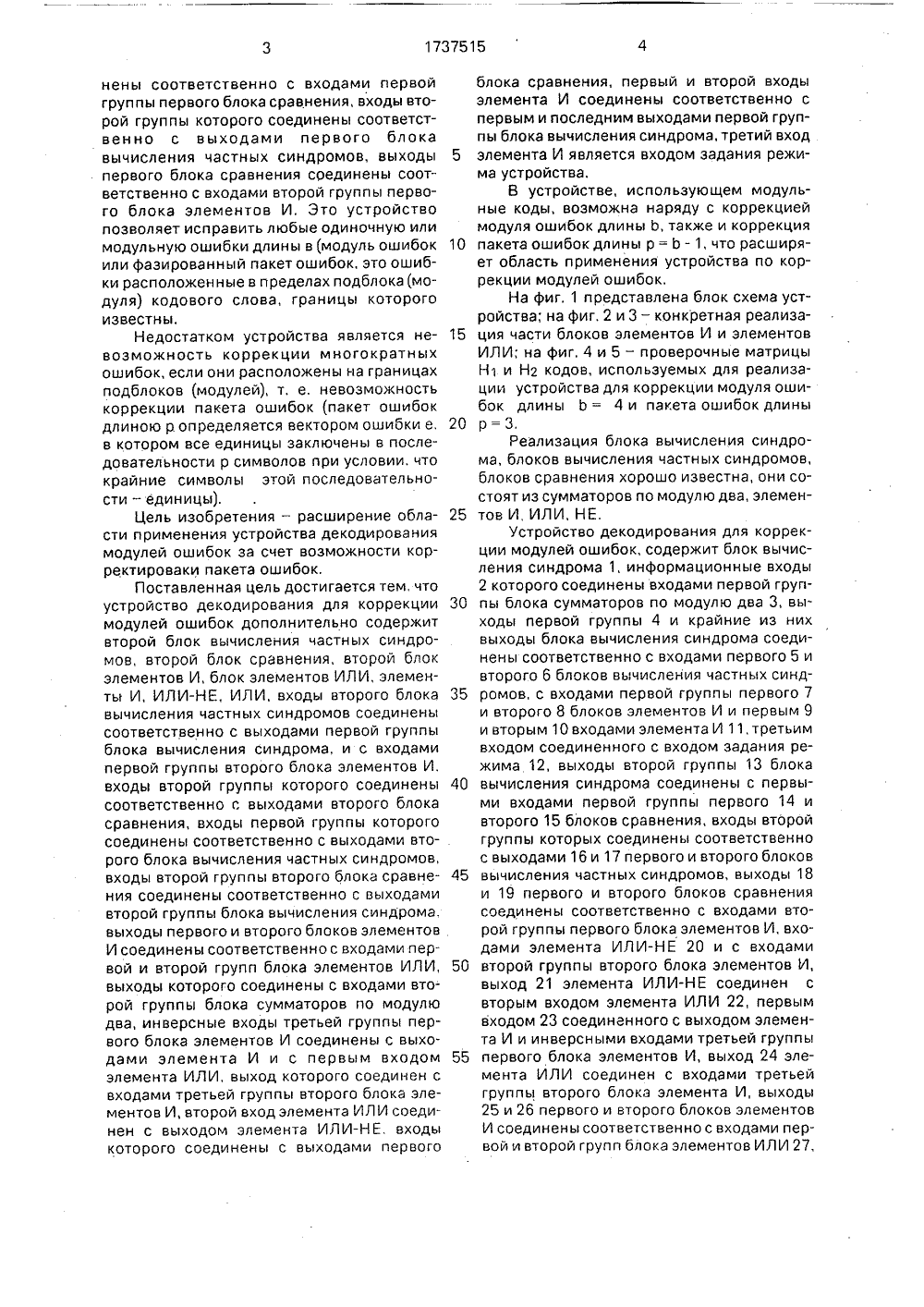

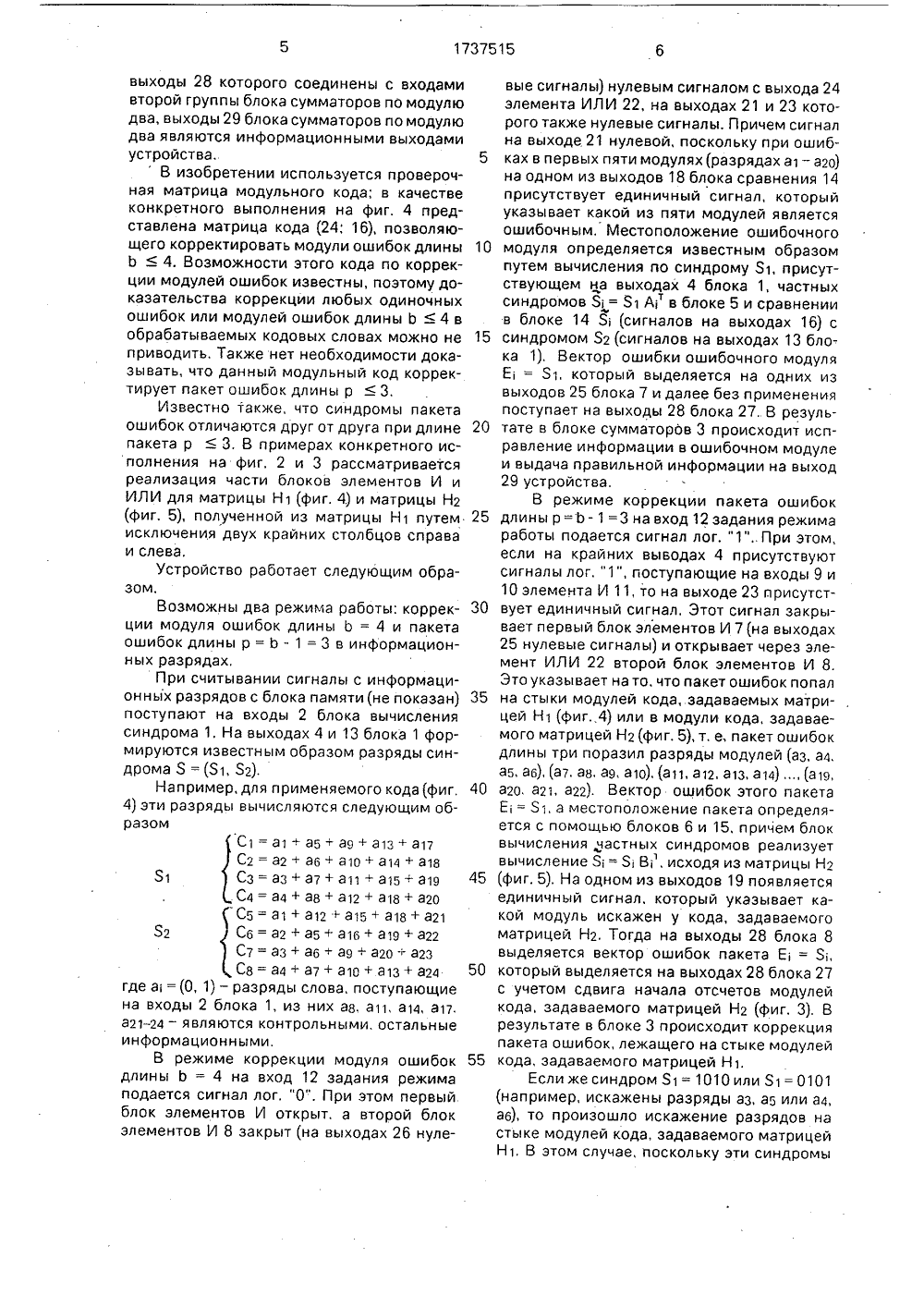

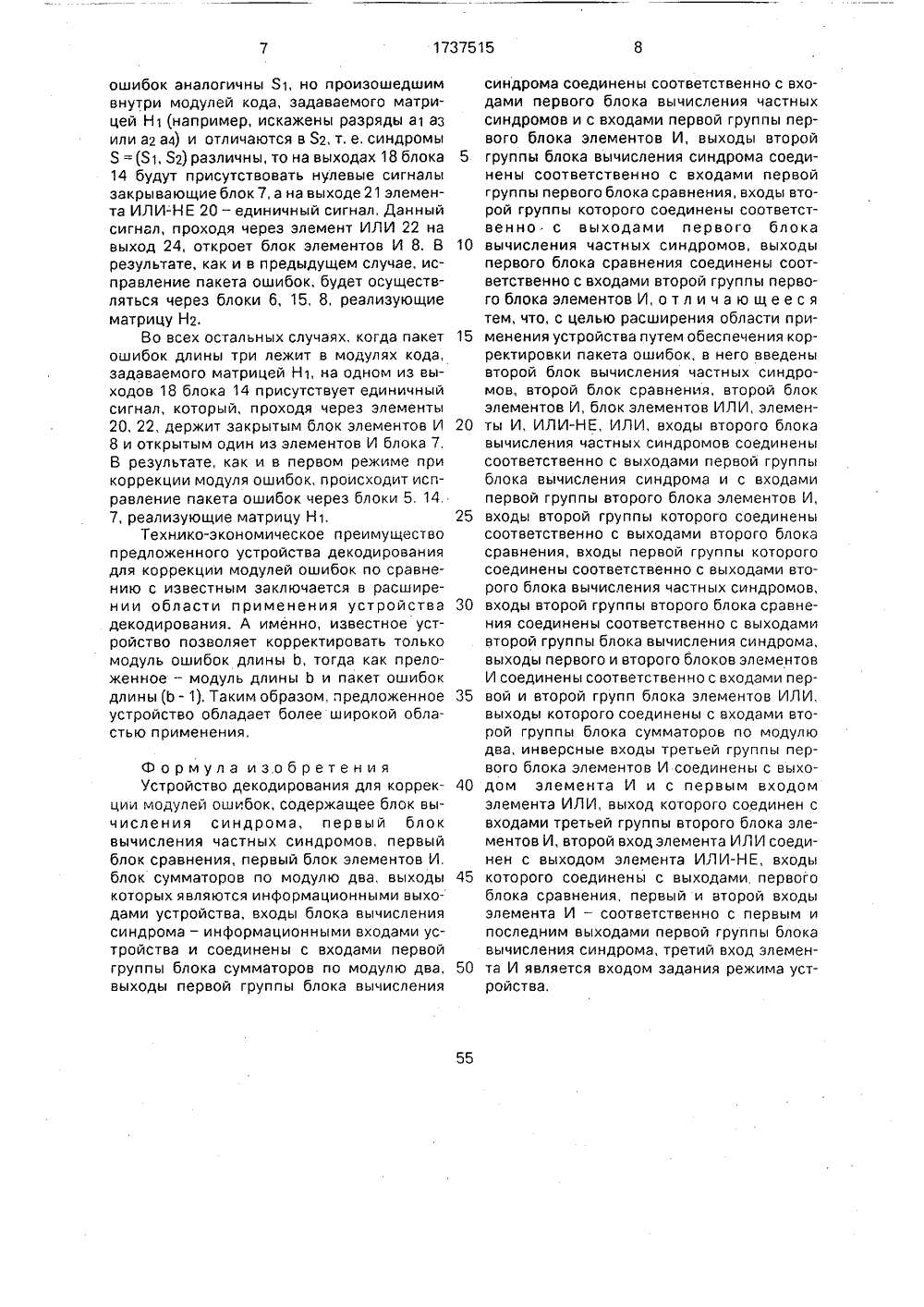

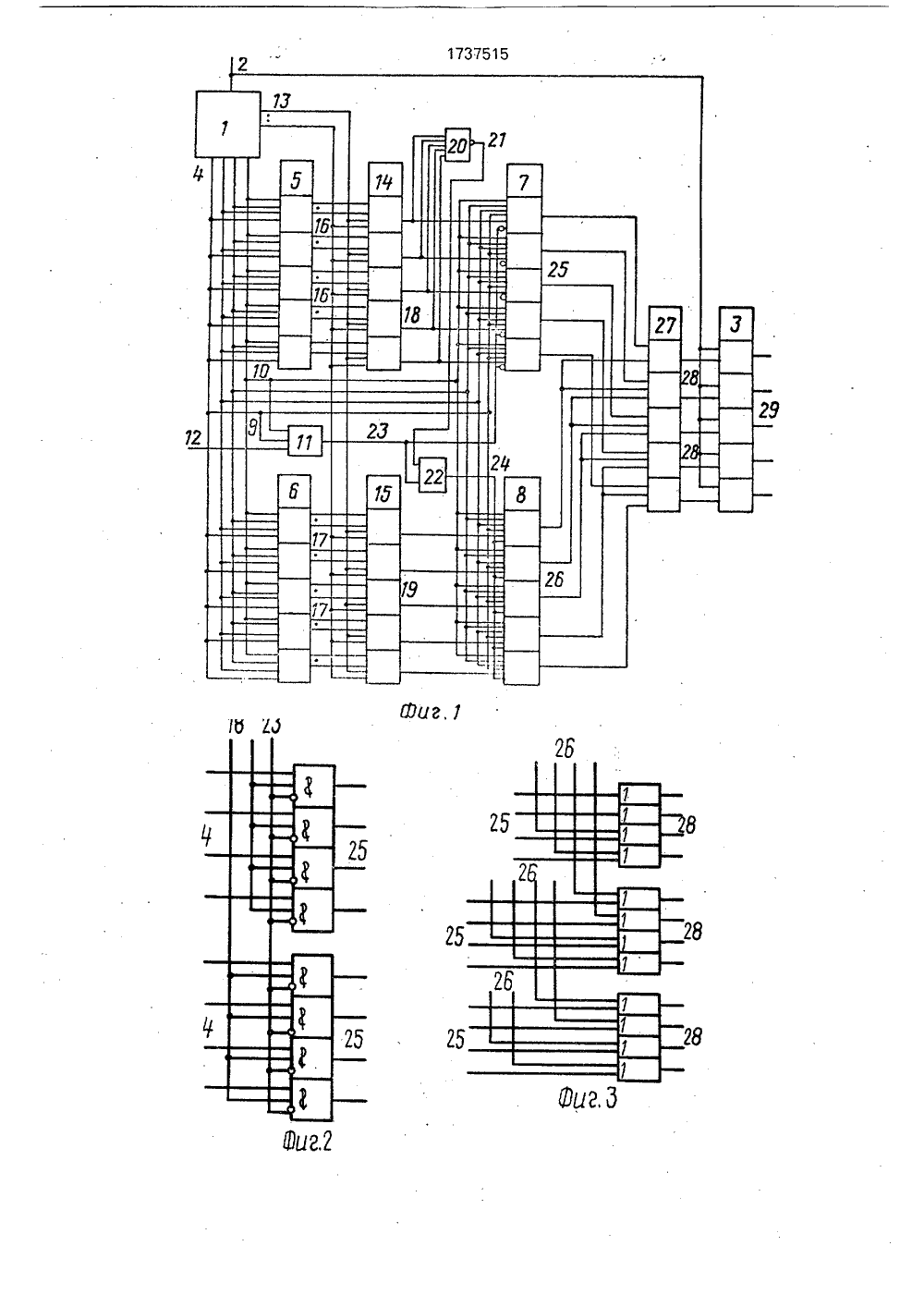

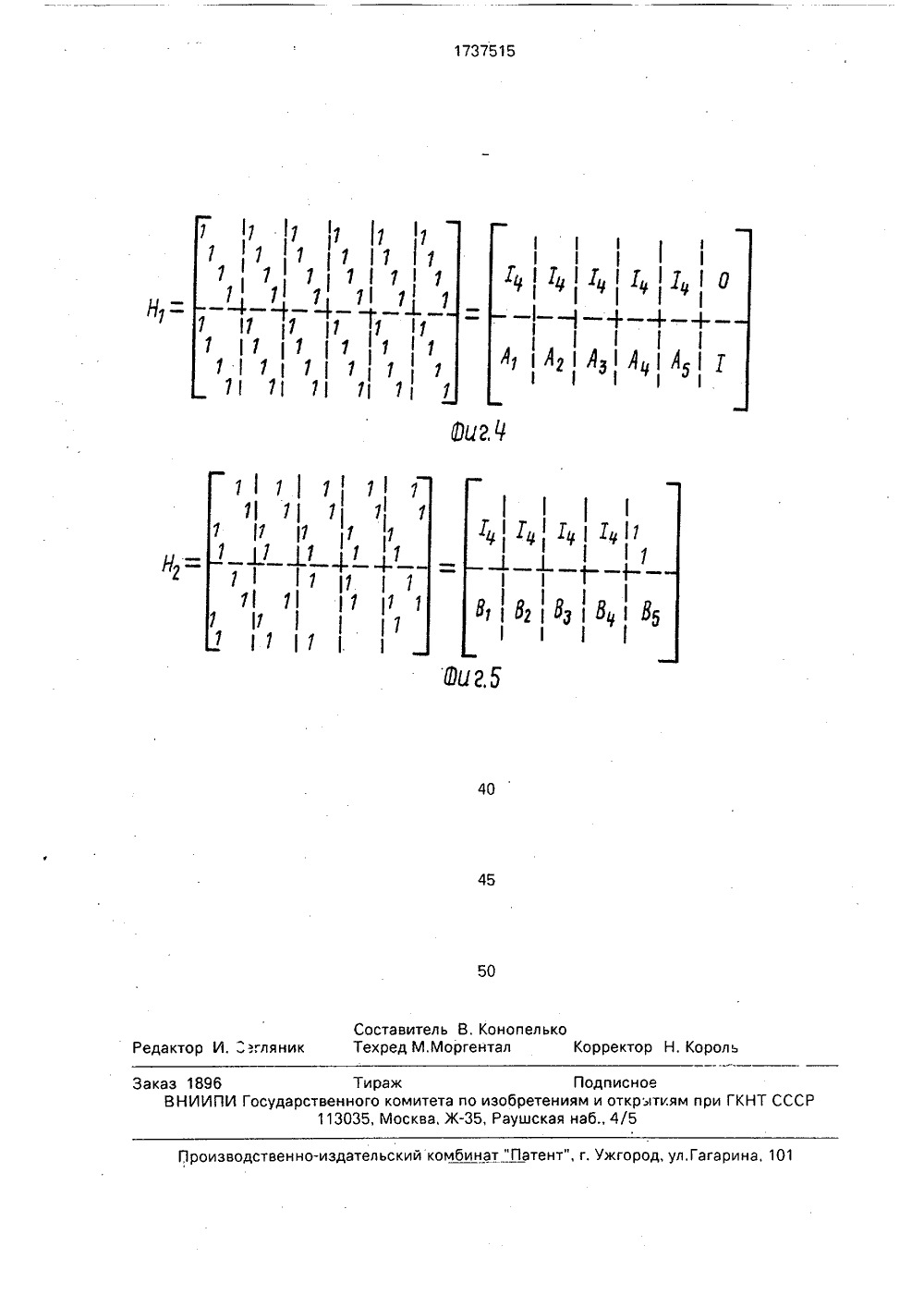

(19 6 11 С 29/О ГОСУДАРСТВЕННЫЙПО ИЗОБРЕТЕНИЯМПРИ ГКНТ СССР МИТЕТТКРЫТИЯ14 ПИСАНИ ЗОБ Т И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Минский радиотехнический институт(56) Авторское свидетельство СССРМ 1302326, кл. 0 11 С 29/00, 1985,Конопелько В.К, и Лосев В,В. Надежноехранение информации в полупроводниковых запоминающих устройствах, М.: Радио(54) УСТРОЙСТВО ДЕКОДИРОВАНИЯ ДЛЯКОРРЕКЦИИ МОДУЛЕЙ ОШИБОК(57) Изобретение относится к области вычислительной техники, а именно к устройст-.вам контроля запоминающих устройств, иможет быть использовано для повышениянадежности запоминающих устройств,Целью изобретения является расширение Изобретение относится к вычислительной технике, а именно к устройствам контроля запоминающих устройств, и может быть использовано для повышения надежности запоминающих устройств,Известны устройства декодирования для контроля памяти, содержащее блок вычисления синдрома, дешифраторы адреса и синдрома, селектор, корректирующие сумматоры по модулю два, позволяющие производить коррекцию ошибок в любом одном разряде кодового слова на основе использования кодов Хэмминга.Однако подобные устройства декодирования для контроля памяти характеризуются недостаточной надежностью из-за невозможности коррекции многократных ошибок, произошедших в соседних разрядах, а именно пакетаошибок,(2области применения устройства декодирования модулей ошибок за счет возможности наряду с коррекцией модулей ошибок производить и коррекцию пакета ошибок. Это достигается применением специальных матриц кодирования, введением дополнительных блоков, элементов и связей. Устройство содержит блок 1 вычисления синдрома, блок 3 сумматоров по модулю два, первый 5 и второй 6 блоки вычисления частных синдромов, элемент И 11, первый 14 и второй 15 блоки сравнения, элемент ИЛИ-НЕ 20, элемент ИЛИ 22 и блок элементов ИЛ И 27. В ведение до пол нител ьн ых блоков, элементов и связей позволяет соответствующим образом использовать верхние разряды синдрома модульного кода для определения местоположения пакета ошибок, Это дает возможность корректировать как модуль так и пакет ошибок. 5 ил. Наиболее близким и сложности и схемному реше емому является устройство для коррекции модулей ош щее блок вычисления син блок вычисления частных с вый блок сравнения, первый И, блок сумматоров по моду которых являются информа дами устройства, входы бл синдрома являются информ дами устройства и соедин первой группы блока суммат два, выходы первой группы ния синдрома соединены с входами первого блока вычи синдромов и с входами пер ваго блока элементов И, группы блока вычисления с о техническои нию к предлагадекодированияибок, содержадрома, первьйиндромов, перблок элементов лю дВд, Выходы ЦИОННЫМИ ВЫХО- ока вычисления ационными вхоены с входами оров по модулю блока вычислеоответственно с сления частных вой группы первыходы второй индрома соеди50 55 нены соответственно с входами первой группы первого блока сравнения, входы второй группы которого соединены соответственно с выходами первого блока вычисления частных синдромов, выходы первого блока сравнения соединены соответственно с входами второй группы первого блока элементов И, Это устройство позволяет исправить любые одиночную или модульную ошибки длины в (модуль ошибок или фазированный пакет ошибок, это ошибки расположенные в пределах подблока (модуля) кодового слова, границы которого известны,Недостатком устройства является невозможность коррекции многократных ошибок, если они расположены на границах подблоков (модулей), т, е. невозможность коррекции пакета ошибок (пакет ошибок длиною р. определяется вектором ошибки е, в котором все единицы заключены в последовательности р символов при условии, что крайние символы этой последовательности - единицы).Цель изобретения - расширение области применения устройства декодирования модулей ошибок за счет возможности корректироваки пакета ошибок.Поставленная цель достигается тем, что устройство декодирования для коррекции модулей ошибок дополнительно содержит второй блок вычисления частных синдромов, второй блок сравнения, второй блок элементов И, блок элементов ИЛИ, элементы И, ИЛИ-НЕ, ИЛИ, входы второго блока вычисления частных синдромов соединены соответственно с выходами первой группы блока вычисления синдрома, и с входами первой группы второго блока элементов И, входы второй группы которого соединены соответственно с выходами второго блока сравнения, входы первой группы которого соединены соответственно с выходами второго блока вычисления частных синдромов, входы второй группы второго блока сравнения соединены соответственно с выходами второй группы блока вычисления синдрома. выходы первого и второго блоков элементов И соединены соответственно с входами первой и второй групп блока элементов ИЛИ, выходы которого соединены с входами второй группы блока сумматоров по модулю два, инверсные входы третьей группы первого блока элементов И соединены с выходами элемента И и с первым входом элемента ИЛИ, выход которого соединен с входами третьей группы второго блока элементов И, второй вход элемента ИЛИ соединен с выходом элемента ИЛИ-НЕ. входы которого соединены с выходами первого 5 10 15 20 25 30 35 40 45 блока сравнения, первый и второй входы элемента И соединены соответственно с первым и последним выходами первой группы блока вычисления синдрома, третий вход элемента И является входом задания режима устройства.В устройстве, использующем модульные коды, возможна наряду с коррекцией модуля ошибок длины Ь, также и коррекция пакета ошибок длины р = Ь -1, что расширяет область применения устройства по коррекции модулей ошибок,На фиг, 1 представлена блок схема устройства; на фиг. 2 и 3 - конкретная реализация части блоков элементов И и элементов ИЛИ; на фиг, 4 и 5 - проверочные матрицы Н 1 и Н 2 кодов, используемых для реализации устройства для коррекции модуля ошибок длины Ь = 4 и пакета ошибок длины р= 3,Реализация блока вычисления синдрома, блоков вычисления частных синдромов, блоков сравнения хорошо известна, они состоят из сумматоров по модулю два, элементов И, ИЛИ, НЕ,Устройство декодирования для коррекции модулей ошибок, содержит блок вычисления синдрома 1, информационные входы 2 которого соединены входами первой группы блока сумматоров по модулю два 3, выходы первой группы 4 и крайние из них выходы блока вычисления синдрома соединены соответственно с входами первого 5 и второго 6 блоков вычисления частных синдромов, с входами первой группы первого 7 и второго 8 блоков элементов И и первым 9 и вторым 10 входами элемента И 11, третьим входом соединенного с входом задания режима 12, выходы второй группы 13 блока вычисления синдрома соединены с первыми входами первой группы первого 14 и второго 15 блоков сравнения, входы второй группы которых соединены соответственно с выходами 16 и 17 первого и второго блоков вычисления частных синдромов, выходы 18 и 19 первого и второго блоков сравнения соединены соответственно с входами второй группы первого блока элементов И, входами элемента ИЛИ-НЕ 20 и с входами второй группы второго блока элементов И, выход 21 элемента ИЛИ-НЕ соединен с вторым входом элемента ИЛИ 22, первым входом 23 соединенного с выходом элемента И и инверсными входами третьей группы первого блока элементов И, выход 24 элемента ИЛИ соединен с входами третьей группы второго блока элемента И, выходы 25 и 26 первого и второго блоков элементов И соединены соответственно с входами первой и второй групп блока элементов ИЛИ 27,выходы 28 которого соединены с входамивторой группы блока сумматоров по модулюдва, выходы 29 блока сумматоров по модулюдва являются информационными выходамиустройства. 5В изобретении используется проверочная матрица модульного кода; в качествеконкретного выполнения на фиг, 4 представлена матрица кода (24; 16), позволяющего корректировать модули ошибок длины 10Ь4. Возможности этого кода по коррекции модулей ошибок известны, поэтому доказательства коррекции любых одиночныхошибок или модулей ошибок длины Ь4 вобрабатываемых кодовых словах можно не 15приводить, Также нет необходимости доказывать, что данный модульный код корректирует пакет ошибок длины р 3.Известно также, что синдромы пакетаошибок отличаются друг от друга при длине 20пакета р3, В примерах конкретного исполнения на фиг. 2 и 3 рассматриваетсяреализация части блоков элементов И иИЛИ для матрицы Н 1(фиг. 4) и матрицы Н 2(фиг, 5), полученной из матрицы Н 1 путем. 25исключения двух крайних столбцов справаи слева,Устройство работает следующим образом.Возможны два режима работы: коррекции модуля ошибок длины Ь = 4 и пакетаошибок длины р = Ь - 1 = 3 в информационных разрядах,При считывании сигналы с информационных разрядов с блока памяти(не показан) 35поступают на входы 2 блока вычислениясиндрома 1, На выходах 4 и 13 блока 1 формируются известным образом разряды синдрама Я =(Я 1, Яг),Например, для применяемого кода(фиг, 404) эти разряды вычисляются следующим образом С 1 = а 1+ а 5+ а 9+ а 1 з+ а 17С 2 = а 2+ аб+ а 10+ а 14+ а 18Сз = аз + а 7+ а 11+ а 15+ а 19С 4 = а 4+ а 8+ а 12+ а 18+ а 20 45+С 5 = а 1+ а 12 + а 15+ а 18+ а 21Сб = д 2 + д 5+ д 18 + д 19 + д 22С 7 = аз+ аб+ а 9+ а 2 о+ а 2 зС 8 = а 4+ а 7+ а 1 о+ а 1 з+ аг 4 50 где а =(О, 1) - разряды слова, поступающие на входы 2 блока 1, из них а 8. а 11, а 14, а 17, а 21-24 - являются контрольными. остальные информационными.В режиме коррекции модуля ошибок 55 длины Ь = 4 на вход 12 задания режима подается сигнал лог, "0". При этом первый блок элементов И открыт. а второй блок элементов И 8 закрыт (на выходах 26 нулевые сигналы) нулевым сигналом с выхода 24 элемента ИЛИ 22, на выходах 21 и 23 которого также нулевые сигналы. Причем сигнал на выходе 21 нулевой, поскольку при ошибках в первых пяти модулях (разрядах а 1 - а 2 о) на одном из выходов 18 блока сравнения 14 присутствует единичный сигнал, который указывает какой из пяти модулей является ошибочным. Местоположение ошибочного модуля определяется известным образом путем вычисления по синдрому Я 1, присутствующем на выходах 4 блока 1, частных синдромов Я = Я 1 А 1 в блоке 5 и сравнении в блоке 14 Я (сигналов на выходах 16) с синдромом Я 2 (сигналов на выходах 13 блока 1), Вектор ошибки ошибочного модуля Е = Я 1, который выделяется на одних из выходов 25 блока 7 и далее без применения поступает на выходы 28 блока 27, В результате в блоке сумматоров 3 происходит исправление информации в ошибочном модуле и выдача правильной информации на выход 29 устройства,В режиме коррекции пакета ошибок длины р =Ь=3 на вход 12 задания режима работы подается сигнал лог. "1"При этом, если на крайних выводах 4 присутствуют сигналы лог, "1", поступающие на входы 9 и 10 элемента И 11, то на выходе 23 присутствует единичный сигнал. Этот сигнал закрывает первый блок элементов И 7 (на выходах 25 нулевые сигналы) и открывает через элемент ИЛИ 22 второй блок элементов И 8. Это указывает на то, что пакет ошибок попал на стыки модулей кода, задаваемых матрицей Н 1 (фиг.,4) или в модули кода, задаваемого матрицей Н 2 (фиг. 5), т. е, пакет ошибок длины три поразил разряды модулей (аз, а 4, а 5, аб), (а 7, а 8, а 9, а 1 о), (а 11, а 12, а 1 з, а 14) , (а 19, а 2 о. а 21, а 22). Вектор ошибок этого пакета Е = Я 1, а местоположение пакета определяется с помощью блоков 6 и 15, причем блок вычисления частных синдромов реализует вычисление Я = Я В, исходя из матрицы Н 2 (фиг. 5), На одном из выходов 19 появляется единичный сигнал, который указывает какой модуль искажен у кода, задаваемого матрицей Н 2. Тогда на выходы 28 блока 8 выделяется вектор ошибок пакета Е = Я;, который выделяется на выходах 28 блока 27 с учетом сдвига начала отсчетов модулей кода, задаваемого матрицей Н 2 (фиг, 3). В результате в блоке 3 происходит коррекция пакета ошибок, лежащего на стыке модулей кода, задаваемого матрицей Н 1.Если же синдром Я 1 = 1010 или Я 1 = 0101 (например, искажены разряды аз, а 5 или а 4, аб), то произошло искажение разрядов на стыке модулей кода, задаваемого матрицей Н 1. В этом случае, поскольку эти синдромы1737515 55 ошибок аналогичны Я 1, но произошедшим внутри модулей кода, задаваемого матрицей Н 1 (например, искажены разряды а 1 аз или аг а 4) и отличаются в 32, т, е, синдромы Я = (Я 1, Я 2) различны, то на выходах 18 блока 14 будут присутствовать нулевые сигналы закрывающие блок 7, а на выходе 21 элемента ИЛИ-НЕ 20 - единичный сигнал, Данный сигнал, проходя через элемент ИЛИ 22 на выход 24, откроет блок элементов И 8. В результате, как и в предыдущем случае, исправление пакета ошибок, будет осуществляться через блоки б, 15, 8, реализующие матрицу Нг,Во всех остальных случаях. когда пакет ошибок длины три лежит в модулях кода, задаваемого матрицей Н 1, на одном из выходов 18 блока 14 присутствует единичный сигнал, который, проходя через элементы 20, 22, держит закрытым блок элементов И 8 и открытым один из элементов И блока 7, В результате, как и в первом режиме при коррекции модуля ошибок, происходит исправление пакета ошибок через блоки 5. 14.7, реализующие матрицу Н 1.Технико-зкономическое преимущество предложенного устройства декодирования для коррекции модулей ошибок по сравнению с известным заключается в расширении области применения устройства декодирования. А именно, известное устройство позволяет корректировать только модуль ошибок длины Ь, тогда как преложенное - модуль длины Ь и пакет ошибок длины (Ь -1). Таким образом, предложенное устройство обладает более широкой областью применения,Формула изобретения Устройство декодирования для коррекции модулей ошибок, содержащее блок вычисления синдрома, первый блок вычисления частных синдромов, первый блок сравнения, первый блок элементов И. блок сумматоров по модулю два, выходы которых являются информационными выходами устройства, входы блока вычисления синдрома - информационными входами устройства и соединены с входами первой группы блока сумматоров по модулю два, выходы первой группы блока вычисления 5 10 15 20 25 30 35 40 45 50 синдрома соединены соответственно с входами первого блока вычисления частных синдромов и с входами первой группы первого блока элементов И, выходы второй группы блока вычисления синдрома соединены соответственно с входами первой группы первого блока сравнения, входы второй группы которого соединены соответственно с выходами первого блока вычисления частных синдромов, выходы первого блока сравнения соединены соответственно с входами второй группы первого блока элементов И, отл и ч а ю щеес я тем, что, с целью расширения области применения устройства путем обеспечения корректировки пакета ошибок, в него введены второй блок вычисления частных синдромов, второй блок сравнения, второй блок элементов И, блок элементов ИЛИ, элементы И, ИЛИ-НЕ, ИЛИ, входы второго блока вычисления частных синдромов соединены соответственно с выходами первой группы блока вычисления синдрома и с входами первой группы второго блока элементов И, входы второй группы которого соединены соответственно с выходами второго блока сравнения, входы первой группы которого соединены соответственно с выходами второго блока вычисления частных синдромов, входы второй группы второго блока сравнения соединены соответственно с выходами второй группы блока вычисления синдрома, выходы первого и второго блоков элементов И соединены соответственно с входами первой и второй групп блока элементов ИЛИ, выходы которого соединены с входами второй группы блока сумматоров по модулю два, инверсные входы третьей группы первого блока элементов И соединены с выходом элемента И и с первым входом элемента ИЛИ, выход которого соединен с входами третьей группы второго блока элементов И, второй вход элемента ИЛИ соединен с выходом элемента ИЛИ-НЕ, входы которого соединены с выходами первого блока сравнения, первый и второй входы элемента И - соответственно с первым и последним выходами первой группы блока вычисления синдрома, третий вход элемента И является входом задания режима устройства.

СмотретьЗаявка

4826477, 17.05.1990

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

КОНОПЕЛЬКО ВАЛЕРИЙ КОНСТАНТИНОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: декодирования, коррекции, модулей, ошибок

Опубликовано: 30.05.1992

Код ссылки

<a href="https://patents.su/6-1737515-ustrojjstvo-dekodirovaniya-dlya-korrekcii-modulejj-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство декодирования для коррекции модулей ошибок</a>

Предыдущий патент: Элемент памяти

Следующий патент: Способ получения токопроводящего наполнителя

Случайный патент: Способ контроля качества позитивных фоторезистов