Генератор псевдослучайной последовательности импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

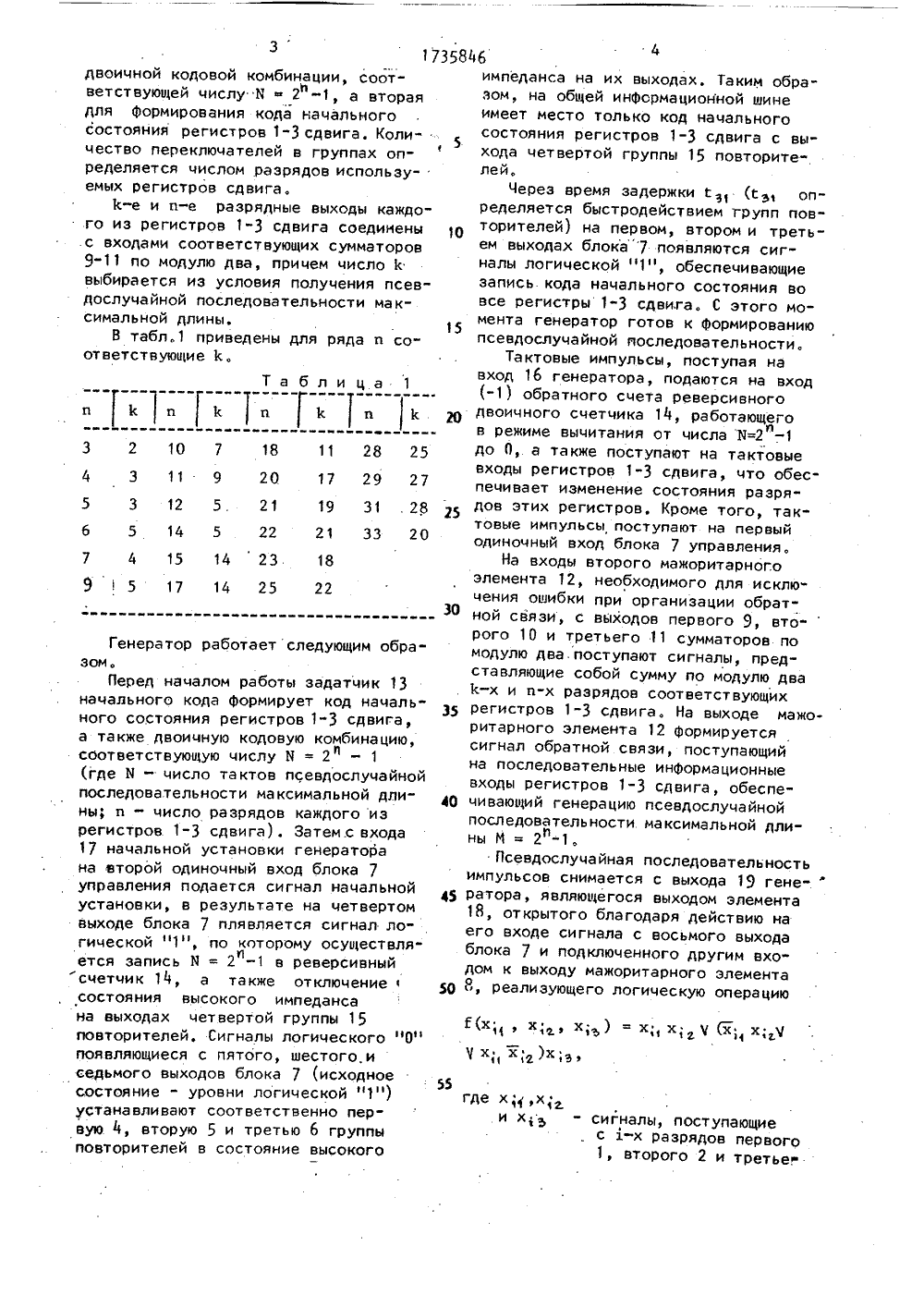

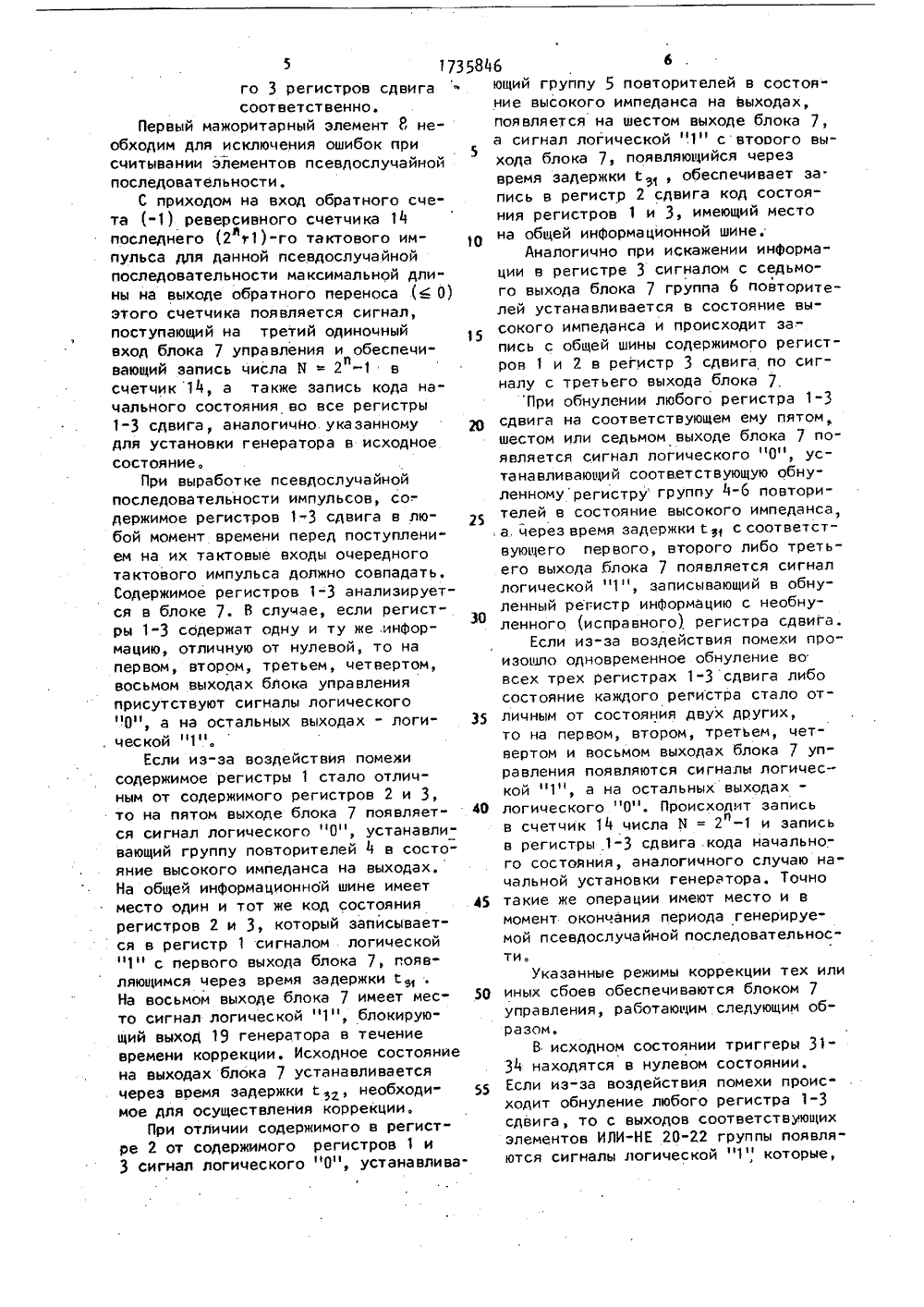

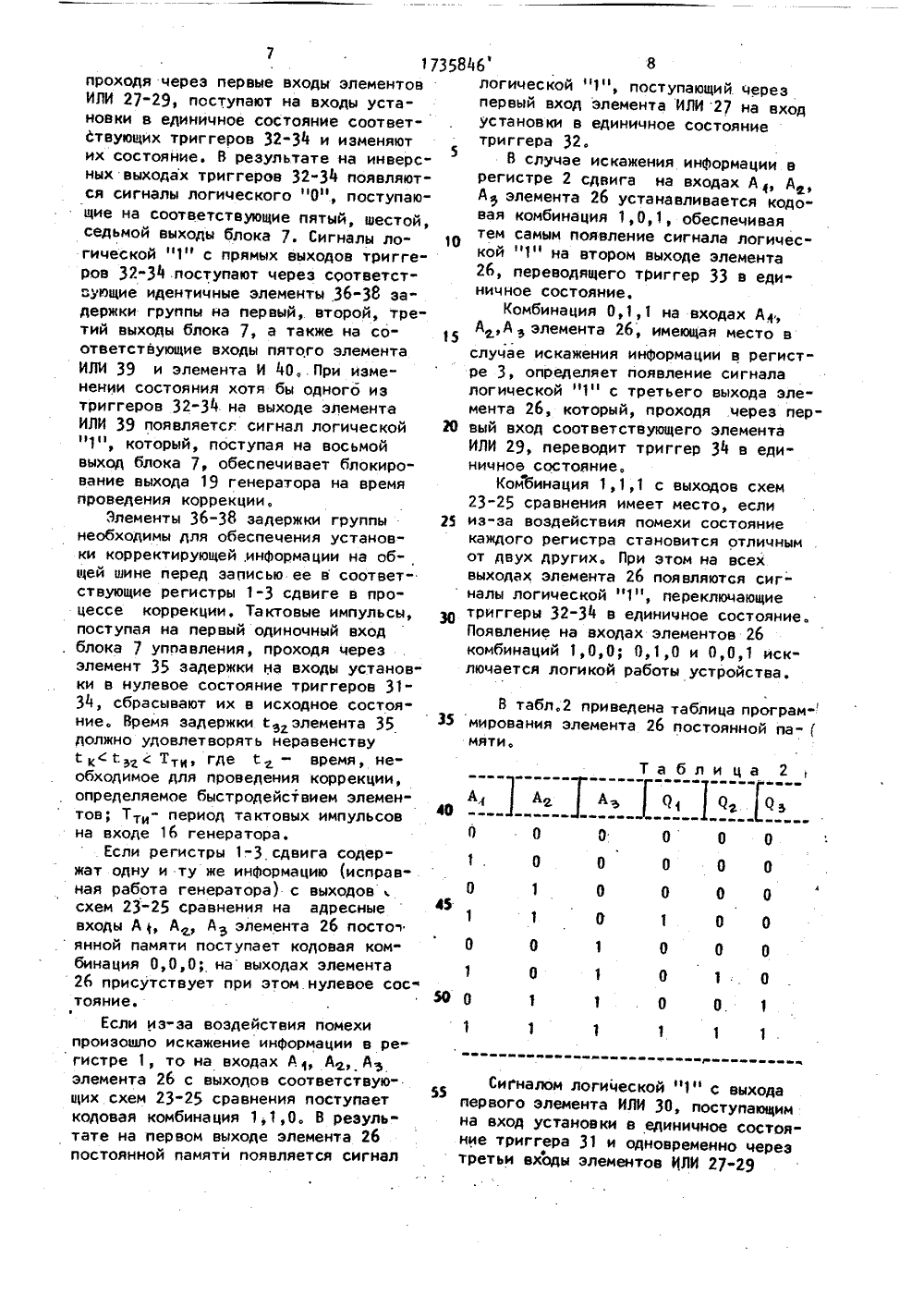

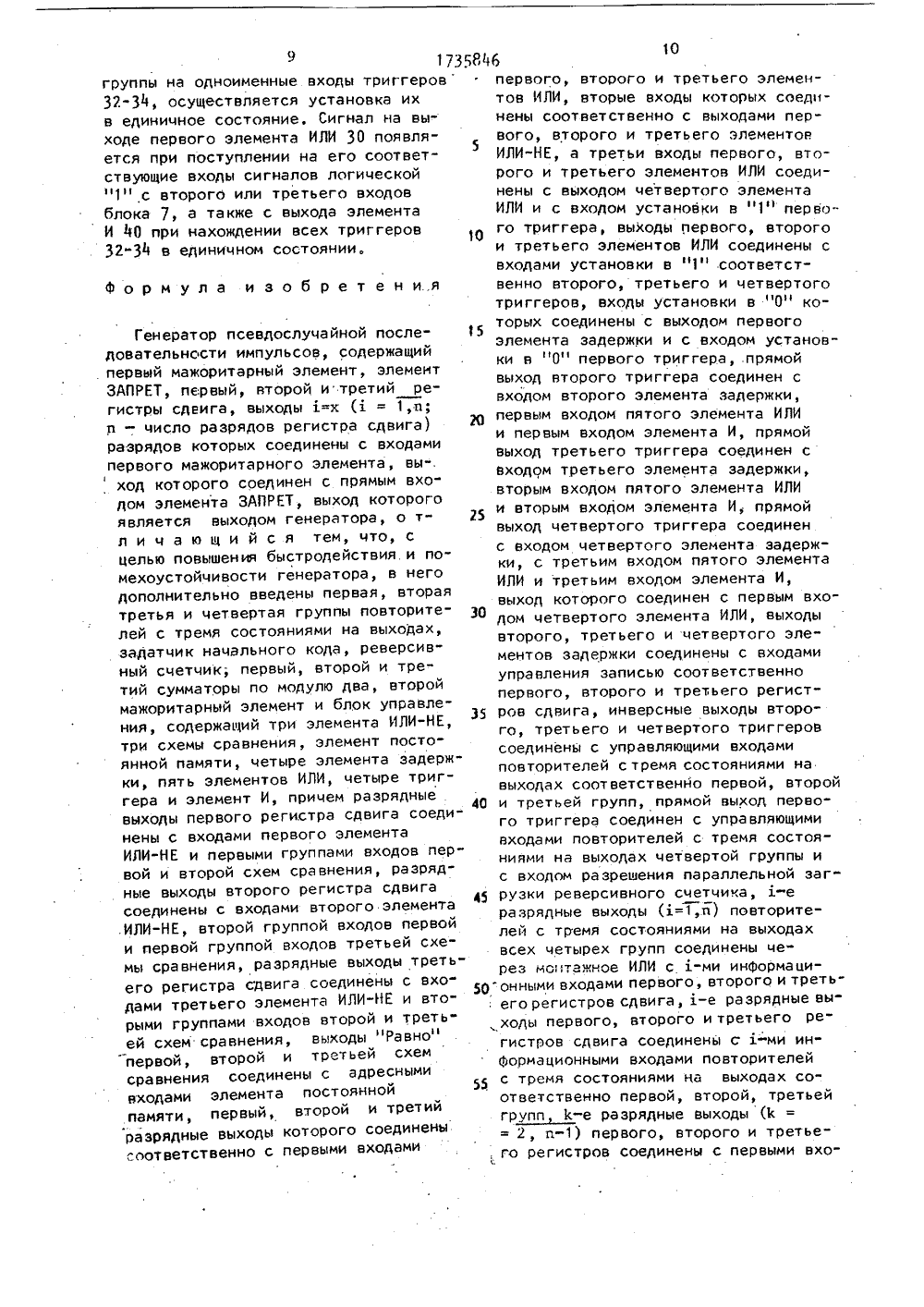

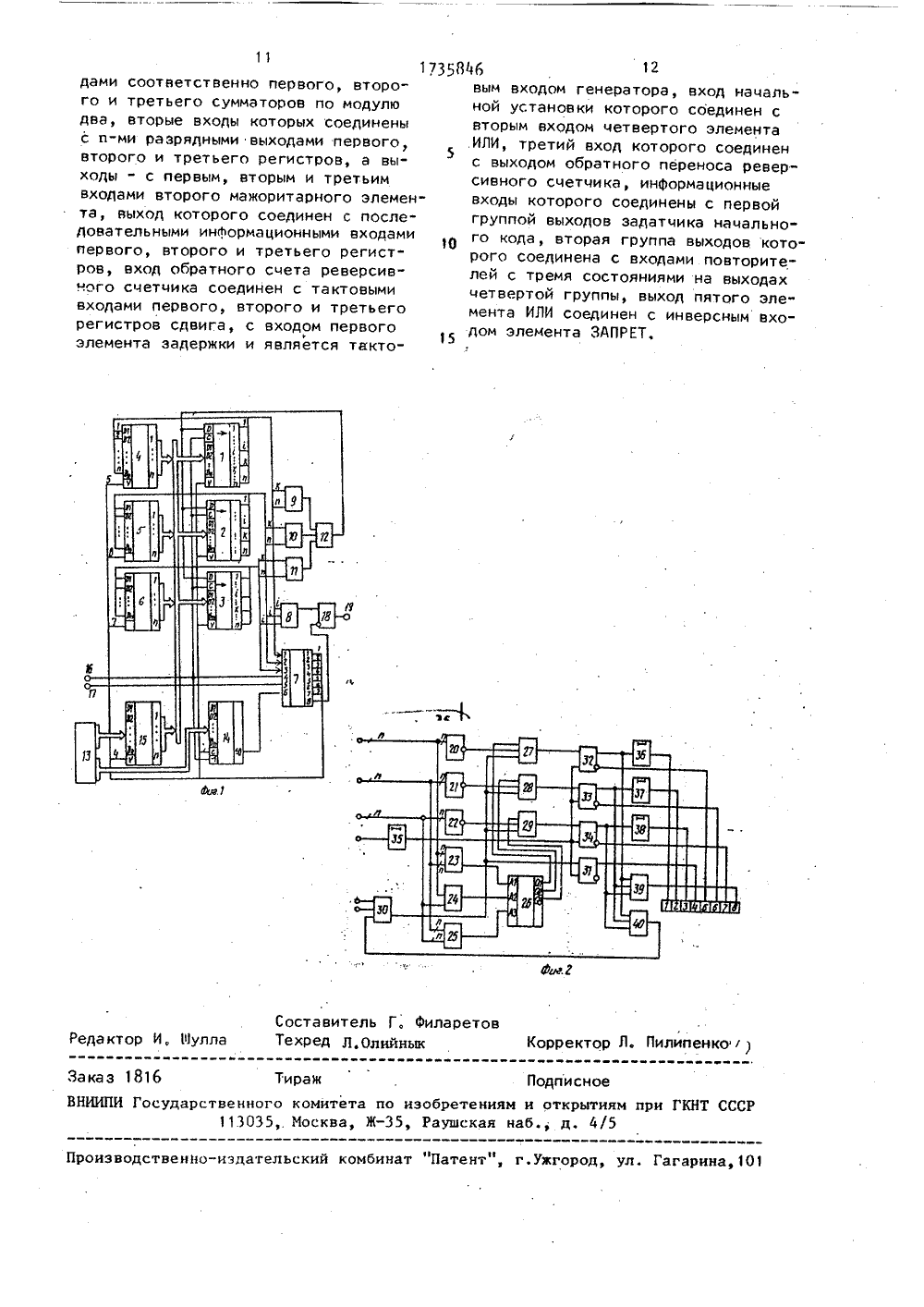

(Х 1Х 1 ь Х 1 ь) = Х Х Ц (Х Х; ЯЦх;, х; )х;з,55 где х;С,х;,и х ъ - сигналы, поступающие с -х разрядов первого второго 2 и третье.двоичной кодовой комбинации, соответствующей числу И2 -1, а вторая для формирования кода начального состояния регистров 1-3 сдвига. Количество переключателей в группах определяется числом разрядов используемых регистров сдвига.Е-е и и-е разрядные выходы каждого из регистров 1"3 сдвига соединены .с входами соответствующих сумматоров 9-11 по модулю два, причем число с выбирается из условия получения псевдослучайной последовательности максимальной длины,В табл.1 приведены для ряда и соответствующие с. и М и К и 1 и 7 18 11 28 25 4 3 11 9 20 17 29 27 5 3 12 5. 21 19 31 . 28 б 5 14 5 22 21 33 20 7 4 15 14 23 1895 17 14 25 22 Генератор работает следующим образом,Перед началом работы задатчик 13начального кода формирует код начального состояния регистров 1-3 сдвига,а также двоичную кодовую комбинацию,соответствующую числу И = 2 - 1(где М - число тактов псевдослучайнойпоследовательности максимальной длины; и - число разрядов каждого изрегистров 1-3 сдвига). Затем.с входа17 начальной установки генераторана второй одиночный вход блока 7управления подается сигнал начальнойустановки, в результате на четвертомвыходе блока 7 плявляется сигнал ло"гической "1", по которому осуществляется запись И = 2 -1 в реверсивныйсчетчик 14, а также отключение 1состояния высокого импедансана выходах четвертой группы 15повторителей. Сигналы логического "0"появляющиеся с пятого, шестого.иседьмого выходов блока 7 (исходноесостояние - уровни логической "1")устанавливают соответственно первую. 4, вторую 5 и третью 6 группыповторителей в состояние высокого 5 О 5 20 25 30 35 40 45 50 импеданса на их выходах, Таким образом, на общей информационной шинеимеет место только код начальногосостояния регистров 1-3 сдвига с выхода четвертой группы 15 повторителей,Через время задержки е, (ез, определяется быстродействием групп повторителей) на первом, втором и третьем выходах блока"7 появляются сигналы логической "1", обеспечивающиезапись. кода начального состояния вовсе регистры 1-3 сдвига. С этого момента генератор готов к формированиюпсевдослучайной последовательности,Тактовые импульсы, поступая навход 16 генератора, подаются на вход(-1) обратного счета реверсивногодвоичного счетчика 14, работающегов режиме вычитания от числа И=2 -1Йдо 0, а также поступают на тактовыевходы регистров 1-3 сдвига, что обеспечивает изменение состояния разрядов этих регистров, Кроме того, тактовые импульсы поступают ка первыйодиночный вход блока 7 управления.На входы второго мажоритарногоэлемента 12, необходимого для исключения ошибки при организации обратной связи, с выходов первого 9, вто-рого 10 и третьего 11 сумматоров помодулю два.поступают сигналы, представляющие собой сумму по модулю два1-х и и-х разрядов соответствующихрегистров 1-3 сдвига. На выходе мажоритарного элемента 12 формируетсясигнал обратной связи, поступающийна последовательные информационныевходы регистров 1-3 сдвига, обеспечивающий генерацию псевдослучайнойпоследовательности максимальной длины М = 2 -1.ИПсевдослучайная последовательностьимпульсов снимается с выхода 19 гене- "ратора, являющегося выходом элемента18, открытого благодаря действию наего входе сигнала с восьмого выходаблока 7 и подключенного другим вхо"дом к выходу мажоритарного элементареализующего логическую операциюа. 45 50 55 а 5 17го 3 регистров сдвигасоответственно.Первый мажоритарный элемент 8 необходим для исключения ошибок присцитывании элементов псевдослучайнойпоследовательности,С приходом на вход обратного счета ("1) реверсивного счетчика 14последнего (2 1)-го тактового имЮпульса для данной псевдослучайнойпоследовательности максимальной длины на выходе обратного переноса (6 О)этого счетчика появляется сигнал,поступающий на третий одиночныйвход блока 7 управления и обеспечивающий запись числа И = 2 -1 всчетчик 14, а также запись кода начального состояния во все регистры1-3 сдвига, аналогично указанномудля установки генератора в исходноесостояние.При выработке псевдослучайнойпоследовательности импульсов, содержимое регистров 1-3 сдвига в любой момент времени перед поступлени"ем на их тактовые входы очередноготактового импульса должно совпадать,Содержимое регистров 1-3 анализируется в блоке 7. В случае, если регистры 1"3 содержат одну и ту же .информацию, отличную от нулевой, то напервом, втором, третьем, четвертом,восьмом выходах блока управленияприсутствуют сигналы логического"0", а на остальных выходах - логической "1".Если из-за воздействия помехисодержимое регистры 1 стало отличным от содержимого регистров 2 и 3,то на пятом выходе блока 7 появляется сигнал логического "0", устанавливающий группу повторителей 4 в состояние высокого импеданса на выходах,На общей информационной шине имеетместо один и тот же код состояниярегистров 2 и 3, который записывается в регистр 1 сигналом логической"1" с первого выхода блока 7, гоявляющимся через время задержки н, .На восьмом выходе блока 7 имеет место сигнал логической "1", блокирующий выход 19 генератора в течениевремени коррекции, Исходное состояниена выходах блока 7 устанавливаетсячерез время задержки, необходимое для осуществления коррекции.При отличии содержимого в регистре 2 от содержимого регистрови3 сигнал логического "0", устанавлива ющий группу 5 повторителей в состояние высокого импеданса на выходах,появляется на шестом выходе блока 7,а сигнал логической ".1" с втооого выхода блока 7, появляющийся черезвремя задержки с 1, обеспечивает за.пись в регистр 2 сдвига код состояния регистров 1 и 3, имеющий местона общей информационной шине.Аналогично при искажении информации в регистре 3 сигналом с седьмого выхода блока 7 группа 6 повторителей устанавливается в состояние высокого импеданса и происходит за.пись с общей шины содержимого регистров 1 и 2 в регистр 3 сдвига по сигналу с третьего выхода блока 7При обнулении любого регистра 1-3сдвига на соответствующем ему пятом,шестом или седьмом выходе блока 7 появляется сигнал логического "0", устанавливающий соответствующую обнуленному регистру группу 4-6 повторителей в состояние высокого импеданса,а, через время задержки ес соответствующего первого, второго либо третьего выхода блока 7 появляется сигналлогической "1", записывающий в обнуленный регистр информацию с необнуленного (исправного) регистра сдвига.Если из-за воздействия помехи произошло одновременное обнуление вовсех трех регистрах 1-3 сдвига либосостояние каждого регистра стало отлицным от состояния двух других,то на первом, втором, третьем, четвертом и восьмом выходах блока 7 управления появляются сигналы логической "1", а на остальных выходахлогицеского "0". Происходит записьв счетчик 14 числа М = 2 -1 и записьяв регистры,1-3 сдвига. кода начального состояния, аналогичного случаю на"чальной установки генератора, Точнотакие же операции имеют место и вмомент окончания периода генерируемой псевдослучайной последовательнос"ти,Указанные режимы коррекции тех илииных сбоев обеспечиваются блоком 7управления, работающим следующим образом.В исходном состоянии триггеры 3134 находятся в нулевом состоянии,Если из-за воздействия помехи происходит обнуление любого регистра 1-3сдвига, то с выходов соответствуюн 1 ихэлементов ИЛИ-НЕ 20-22 группы появляются сигналы логической "1", которые,5846" 8 5 10 15 Ю ЪЬ 30 Табли ца 2 0 0 0 0 О 0 1 1 173проходя через первые входы элементовИЛИ 27-29, поступают на входы установки в единичное состояние соответствующих триггеров 32-34 и изменяютих состояние. В результате на инверсных выходах триггеров 32-34 появляются сигналы логического "0", поступающие на соответствующие пятый, шестой,седьмой выходы блока 7. Сигналы логической "1" с прямых выходов тригге"ров 32-34 .поступают через соответствующие идентичные элементы 36-38 эа"держки группы на первый,. второй, третий выходы блока 7, а также на соответствующие входы пятого элементаИЛИ 39 и элемента И 40,.При изменении состояния хотя бы одного изтриггеров 32-34 на выходе элементаИЛИ 39 появляется сигнал логической"1", который, поступая на восьмойвыход блока 7, обеспечивает блокирование выхода 19 генератора на времяпроведения коррекции.Элементы 36-38 задержки группынеобходимы для обеспечения установки корректирующей, информации на общей шине перед записью ее в соответствующие регистры 1-3 сдвиге в процессе коррекции, Тактовые импульсы,поступая на первый одиночный вход. блока 7 управления, проходя черезэлемент 35 задержки на входы установки в нулевое состояние триггеров 31"34 сбрасывают их в исходное состояУ35ние. Время задержки йз элемента 35должно удовлетворять неравенствукс( Хтк где Свремя необходимое для проведения коррекции,определяемое быстродействием элемен 40тов; Тти" период тактовых импульсовна входе 16 генератора,Если регистры 1.-3 сдвига содержат одну и ту же информацию (исправная работа генератора) с выходовсхем 23"25 сравнения на адресные43входы А 1, А, А элемента 26 постоянной памяти поступает кодовая ком"бинация 0,0,0; на выходах элемента26 присутствует при этом. нулевое сос.Ятояние.Если из-за воздействия помехипроизошло искажение информации в регистре 1, то на входах Ал, А, Аэлемента 26 с выходов соответствующих.схем 23-25 сравнения поступаеткодовая комбинация 1,1,0. В результате на первом выходе элемента 26постоянной памяти появляется сигнал логической "1", поступающий через первый вход элемента ИЛИ 27 на вход установки в единичное состояние триггера 32.В случае искажения информации в регистре 2 сдвига на входах А , А, А элемента 26 устанавливается кодовая комбинация 1,0,1, обеспечивая тем самым появление сигнала логической "1" на втором выходе элемента 26, переводящего триггер 33 в еди" ничное состояние.Комбинация 0,1,1 на входах А 1, А ,А з элемента 26, имеющая место в случае искажения информации в регистре 3, определяет появление сигнала логической "1" с третьего выхода эле" мента 26, который, проходя .через первый вход соответствующего элемента ИЛИ 29, переводит триггер 34 в единичное состояние.Комбинация 1,1,1 с выходов схем 23-25 сравнения имеет место, если из-за воздействия помехи состояние каждого регистра становится отличным от двух других. При этом на всех выходах элемента 26 появляются сиг- налы логической "1", переключающие триггеры 32-34 в единичное состояние. Появление на входах элементов 26 комбинаций 1,0,0; 0,1,0 и 0,0,1 иск" лючается логикой работы устройства. В табл,2 приведена таблица програм"мирования элемента 26 постоянной па-мяти. 1. О 0 О 0 0 1 О 1 0 0 о ао о о 1 0 1 0. 0 01 0 О. 1 Сигналом логической "1" с выхода первого элемента ИЛИ 30, поступающим на вход установки в единичное состояние триггера 31 и одновременно через третьи входы элементов ЦЛИ 27-299 17 группы на одноименные входы триггеров32-3 М, осуществляется установка их в единицное состояние, Сигнал на выходе первого элемента ИЛИ 30 появляется при поступлении на его соответствующие входы сигналов логической "1" с второго или третьего входов блока 7, а также с выхода элемента И Й 0 при нахождении всех триггеров 32-3 я в единичном состоянии. 38116 5 10 15 М 25 30 35 40 45 5 О онными входами первого, второго и третьего регистров сдвига, з-е разрядные вы 55 формула изобретения Генератор псевдослучайной последовательности импульсов, содержащий . первый мажоритарный элемент, элементЗАПРЕТ, первый, второй и третий регистры сдвига, выходы д=х (з = 1,п;и - число разрядов регистра сдвига)разрядов которых соединены с входамипервого мажоритарного элемента, вы-.ход которого соединен с прямым входом элемента ЗАПРЕТ, выход которогоявляется выходом генератора, о тл и ч а ю щ и й с я тем, что, сцелью повышения быстродействия. и помехоустойчивости генератора, в негодополнительно введены первая, втораятретья и четвертая группы повторителей с тремя состояниями на выходах,задатчик начального кода, реверсивный счетчик; первый, второй и третий сумматоры по модулю два, второймажоритарный элемент и блок управления, содержащий три элемента ИЛИ-НЕ,три схемы сравнения, элемент постоянной памяти, четыре элемента задержки, пять элементов ИЛИ, четыре триггера и элемент И, причем разрядныевыходы первого регистра сдвига соединены с входами первого элементаИЛИ-НЕ и первыми группами входов пер"вой и второй схем сравнения, разрядные выходы второго регистра сдвигасоединены с входами второго элементаИЛИ-НЕ, второй группой входов первойи первой группой входов третьей схемы сравнения, разрядные выходы третьего регистра сдвига соединены с входами третьего элемента ИЛИ-НЕ и вторыми группами входов второй и треть"н н ей схем сравнения, выходы Равнои первой, второй и третьеи схем сравнения соединены с адресными входами элемента постоянной памяти, первый, второй и третий разрядные выходы которого соединены соответственно с первыми входами первого, второго и третьего элементов ИЛИ, вторые входы которых соединены соответственно с выходами первого, второго и третьего элементовИЛИ-НЕ, а третьи входы первого, второго и третьего элементов ИЛИ соединены с выходом четвертого элементаИЛИ и с входом установки в "1" первого триггера, выходы первого, второгои третьего элементов ИЛИ соединены свходами установки в "1" соответственно второго, третьего и четвертоготриггеров, входы установки в "0" которых соединены с выходом первогоэлемента задержки и с входом установки в "0" первого триггера, прямойвыход второго триггера соединен свходом второго элемента задержки,первым входом пятого элемента ИЛИи первым входом элемента И, прямойвыход третьего триггера соединен свходом третьего элемента задержки,вторым входом пятого элемента ИЛИи вторым входом элемента И, прямой выход четвертого триггера соединенс входом четвертого элемента задержки, с третьим входом пятого элементаИЛИ и третьим входом элемента И,выход которого соединен с первым входом четвертого элемента ИЛИ, выходывторого, третьего и четвертого элементов задержки соединены с входамиуправления записью соответственнопервого, второго и третьего регистров сдвига, инверсные выходы второго, третьего и четвертого триггеровсоединены с управляющими входамиповторителей с тремя состояниями навыходах соответственно первой, второйи третьей групп, прямой выход первого триггера соединен с управляющимивходами повторителей с тремя состояниями на выходах четвертой группы ис входом разрешения параллельной загрузки реверсивного счетчика, -еразрядные выходы 0=1,й) повторителей с тремя состояниями на выходах всех четырех групп соединены через мст"жное ИЛИ с -ми информаци, ходы первого, второго и третьего регистров сдвига соединены с 1-ми информационными входами повторителей с тремя состояниями на выходах со"ответственно первой, второй, третьей групп у-е раврядные выходы Ос = = 2, и) первого, второго и третье, .го регистров соединены с первыми вхоираж Подписно комитета по изобретениям и открыт Москва, Ж, Раушская наб., д, 4 НИИП м при ГКНТ ССС Государственного 1130351.Производственно-издательский комбинат "Патент", г,ужгород, ул. Гагарина,101 17 ЯМ12 дами соответственно первого, второ- вым входом генератора, вход начальго и третьего сумматоров по модулю ной установки которого соединен с два, вторые входы которых соединены вторым входом четвертого элемента с и-ми разрядными выходами первого, .ИЛИ, третий вход которого соединен второго и третьего регистров, а вы- с выходом обратного переноса реверходы - с первым, вторым и третьим сивного счетчика, информационные входами второго мажоритарного элемен- входы которого соединены с первой та, выход которого соединен с после- группой выходов задатчика начальнодовательными информационными входами О го кода вторая группа выходо101 я уппа выходов кото- первого, второго и третьего регист- рого соединена с входами повторитеров, вход обратного счета реверсив- лей с тремя состояниями на выходах нрго счетчика соединен с тактовыми четвертой группы, выход пятого элевходами первого, второго и третьего мента ИЛИ соединен с инверсным вхорегистров сдвига, с входом первого15дом элемента ЗЯПРЕТ элемента задержки и является такто

СмотретьЗаявка

4691136, 16.05.1989

ПРЕДПРИЯТИЕ ПЯ Р-6348

МАНУКЯН ГЕОРГИЙ ЮРЬЕВИЧ, МКРТЫЧЯН САМВЕЛ АРАМОВИЧ

МПК / Метки

МПК: G06F 7/58

Метки: генератор, импульсов, последовательности, псевдослучайной

Опубликовано: 23.05.1992

Код ссылки

<a href="https://patents.su/6-1735846-generator-psevdosluchajjnojj-posledovatelnosti-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Генератор псевдослучайной последовательности импульсов</a>