Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1564621

Автор: Варавка

Текст

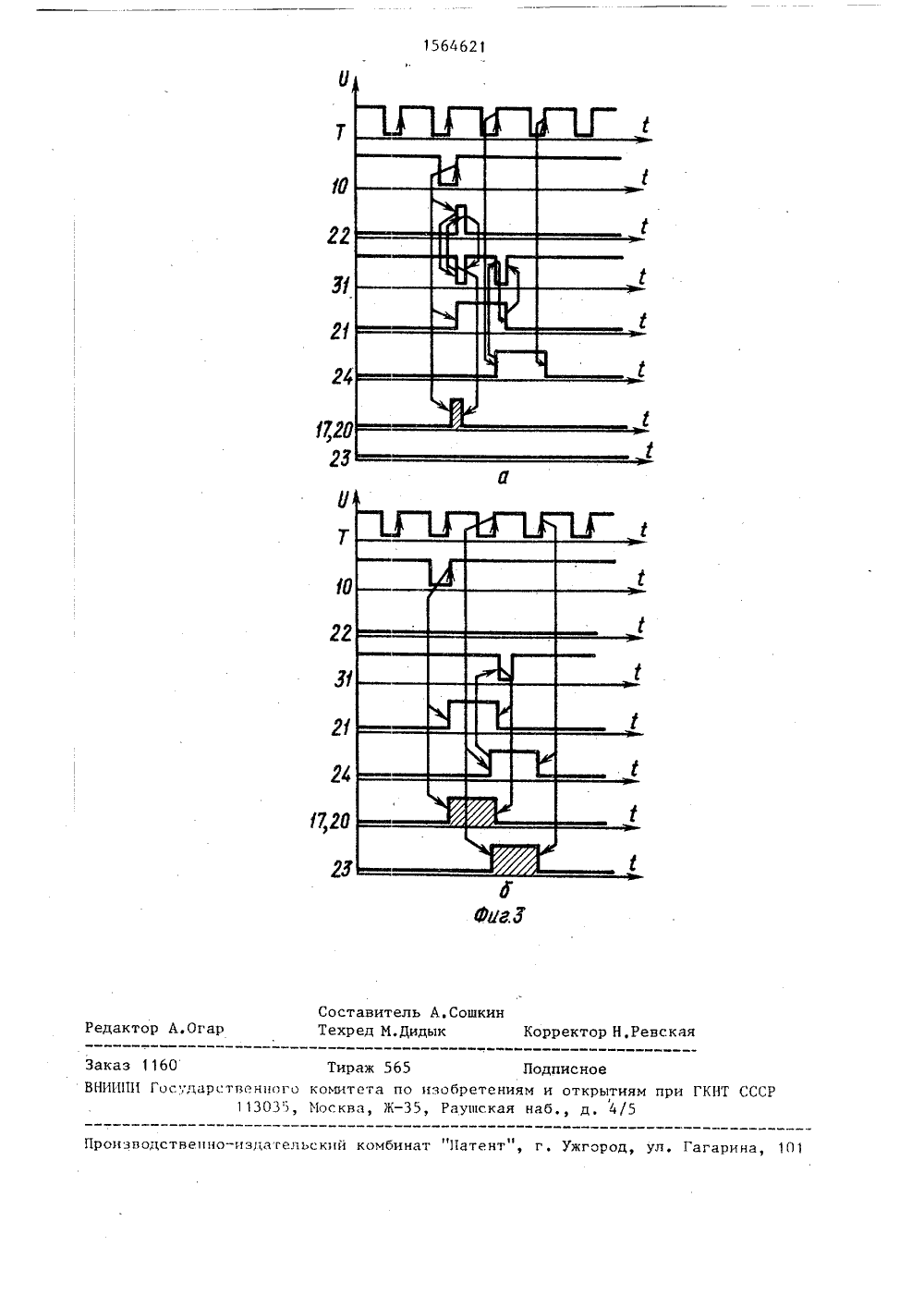

; г".(2 1) (22) (46) нальна устрой времен ва; на мы раб ереходах ГОСУДАРСТВЕННЫЙ НОМИТЕТпо изОБРетениям и ОтнРытиймПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБ й А ВТОРСНСМУ СВЯДЕТЕЛЬС 4385184/2 4-2 42902, 8815,05.90. Бюл, Ф 18(56) Мик Дж., Брик Дж. Проектирование микропроцессорных устройств с разрядно-модульной организацией, М.: 1984, с. 26, рис 2.3.Авторское свиде тельство СССР 9 1322281, кл, С 06 Р 9/22, 1987. (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ(57) Изобретение предназначено для использования в вычислительной технике при создании устройств ввода-вывода, аппаратуры сопряжения, измерительной и бытовой техники. Цель изо-. Изобретение относится к вычисли 3 тельной технике и может быть исполь зовано при создании широкого класса средств: устройств ввода-вывода, аппаратуры сопряжения, измерительной и бытовой техники.Цель изобретения - повышение быстройдействия устройства при многофункционал.:ном использовании разядов блока памяти микрокоманд и инхронизации признаков условий.На фиг, 1 представлена функциоя схема микропрограммного ства управления;.на фиг. 2 - ные диаграммы работы устройстфиг, 3 - временные диаграмоты устройства при условных брете ния - повышен ие быстродейств ияустройства при многофункциональномислользовании разрядов блока паляти микрокаманд и синхронизации призиаков условий. Устройство содержитмультиплексор, элемент ИСКЛЮЧАЮЩЕЕИЛИ, узел Формирования адреса микрокоманд, блок памяти, буферные регистры, первый и второй элементы НЕэлемент И, элемент И-НЕ. Цель достигается тем, что первый и второй буферные регистры, первый и второйэлементы НЕ, элемент И-НЕ, элемент Ипозволяют совместить во времениФункции предварительного буферирования разрядов блока памяти микроко"манд и синхронизации признаков условий. 3 ил,Устрсйство (Фиг. 1) содержит мультиплексор 1, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, вход 3 синхронизации устройства, узел 4 формирования адреса микрокоманды (УФАМ), блок 5 памяти микрокоманд, группу 6 дешиф-. раторов, выход 7 поля микроопераций блока 5 памяти микрокоманды, выход 8 микроопераций устройства, выход 9 полей логических условий и кода операции блока 5 памяти микрокоманд, выход 10 первого дещифратора группы 6 дешифраторов, первый буферный регистр 11, второй буферный регистр 12, первый элемент НЕ 13, второй элемент НЕ 14, элемент И-НЕ 15, элемент И 16, выход 17 первого разряда первого буферного регистра 11, 156462135 40 ход 18 логических условий устройста, вход 19 сброса (установки в "0") стройства, выход 20 с второго по -й разрядов первого буферного реГистра, выход 21 (Р+1)-го разряда Первого буферого регистра, выход 22 (Р+2)-го разряда первого буферного регистра, выход 23 с первого по ,(Р)-й разрядов второго буферного егистра, выход 24 (Р+1) -го разряда второго буферного регистра, вход 5 правления мультиплекора 1, вход 26 тробирования мультиплексора 1, призак 27 инверсии условия поля логиеских условий блока памяти микрскоанд, вход 28 .с первого по Р -й разядов первого буферного регистра, ходы 29 и 30 (Р+2)-го и (Р+ 1)-го азрядов первого буферного регисг.:аи вход 31 сброса первого буферного егистра.К особенностям устройства Относитфя следующее.Рахряды управляющей памяти, подвключенные к мультиплексору условий,хеме управления полярностью услоия, схеме выбора источника адресаледующей микрокоманды и управлсни.; 1 аботой стека, не используются приорсировании адреса перехода, при управлении внешними цепями. .Зто приводит к увеличению Объема аппа 11 атурь, расширяющей разрядность поля управляющей памяти,и увегению трудоемкости проектирования в части азработки микропрограммного обесп-" чения.В различной аппаратуре, где применимо предлагаемое устройство, возМожно подключение сигналов условий, ссинхронньх по Отношению к тактОвой частоте устройства. При их анализе (1 еэ предварительной синхронизации Возникают гонки в схеме управления .Текам и выбором источника адреса что приводит к сбоям в работе устройства. Возможность предварительной синхронизации сигналов условий до мультиплексирования, т.е. за дределами устройства, связана с аппаратными затратами, объем которых зависит ст количества анализируемьп Сигналов условий, Реализация требо ания многофункционального испольЗования:разрядного поля блока памя- ;и микрокоманд обязательно приводит К задержке во времени, так как необходимо организовывать предваритель"Работа на втором режиме Осуще твляется гри необходимости обеспечения выборки подлежащей выполнению микрокомандь, не являющейся очередной командой последовательности, з зависимости От условия ии без негоДанный переход происходит за дватакта синхронизирующей частоты. Впервом такте в группе 6 дешифраторов вырабатывается микрооперация 10, подключенная к первому буферному региСтру 11. Одновременно 50 ное буферирование считываемых изнего констант,Синхронизация внутри устройствасигналов условий, асинхронных поотношению к его тактовой частоте, дополнительно увеличивает временную за-.держку устройства, т.е. снижает егобыстродействие.Узел 4 может быть реализован намикросхеме 1804 ВУ 1,Устройство работает в двух режимах: либо осуществляет последовательную выборку микрокоманд Основной режим), либо реализует условный(безусловный) переход.Работа в тои или ином режиме определяется сигналами устанавливае 7мыми вторым буферным регис;ром 12.На входах кода операции УФАМ, Так,.сигналы 23 выбрают в качестве источника адреса. следующей микрокоманды или внутренний счетчик микрокоманд (СМК), или регистр адресаУФАМ или внутренний стек УФАМ,или шину данных, подкл:оченную квходам УФАМ, определяют режим работы со стеком. В Основном режиме разряды / блока 5 памяти микрокоманд,стробированные тактовой частотой,вырабатывают в группе 6 дешифратороводну или несколько микроогераций 8,.которые в "сопровоядении разрядов 9блока памяти микропрограмм выдаютсяво внешние устройства. Мкрооперации 8 записывают в регистры внешних устройств кодовые константыразрядов 9 в соответствии с определенным алгоритмом, в результате чего и производится Функция управленияВ этом режиме второй буферньй регистр 12 устанавливают на управляю.Цих входах УФАМ сигналы, соответствующие отключенному стеку, и выбирает СМК в качестве источника адреса следующей микрокоманды.1564621 5О 15 20 25 30 5разряды 9 блока памяти микрокоманд селектируют необходимое условие в мультиплексоре 1, выбирают его необходимую полярность в элементе 2. Часть разрядов 9 блока памяти микрокоманд подключена к гервому буФерному регистру 1 1. Они содержат инФормацию о предлагаемом источнике адреса перехода и режиме работы стека УФАИ. Посредством микроопера ции 10 в первом буФерном регистре 1 1 синхронизируется селектированное условие и в зависимости от его полярности предварительно запоминаются или не запоминаются) инФормационнонесущие разряды блока памяти микрокоманд. Однако после первого такта выходы второго буФерного регистра остаются без изменений. Собственно сам переход, осуществляется . после окоччания второго такта, когда второй буферный регистр 12 устанавливает на входах УФАМ код нового источника адреса микрокоманды. В течение второго такта разряды 9 блока памяти микрокоманд должны содержать адрес перехода, если предусматрива= ется в качестве источника адреса выбрать внутренний регистр адреса УФАИ. Как видно из Функциональной схемы, разряды 9 блока памяти микрокоманд подключены к входам внутреннего регистра адреса УФАИ. Запись в этот регистр всегда разрешена. ОДнако в режиме последовательной выборки микрокоманд записанные в регистр адреса разряды 9 блока памяти микрокоманд никакой Функциональной нагрузки не несут.По окончании второго такта второй буФерный регистр 12 устанавливает на своих выходах сигналы, соответствующие режиму последователь" ной выборки. Далее все повторяетоя. Работа в обоих режимах пояснена временными диаграммами на Фиг. 2.Таким образом, разряды 9 блока памяти микрокоманд используются в трех основных Функциях микропрограммного устройства управления, разнесенных во времени. Они участвуют в управлении внешними устройствами, подготовке источника адреса перехода в зависимости от условия, в Формировании самого адреса перехода. Таким образом реализуется многоФунк-: циональное использование разрядов блока памяти микрокоманд. Перед началом работы устройство устанавливается в исходное состояиие сигналом "Сброс" отрицательной полярности. Этот сигнал проходит через элемент И 16, поступает на установочный вход регистра 11 обнуляет его выходы. Ближайшим положительным перепадом тактовой частоты состояние регистра 11 переписывается в регистр 12. В результатеУФЛМ начинает работать в режимепоследовательной выборки микрокоманд с отключенным стеком. Предположим, что Возникла необходимость осуществления условного перехода.Б первом такте разряды 9 блока памяти микрокоманд работают следующимобразом. Разряды 25 логических условий из поля 9 селектируют в мультиплексоре 1 нужный сигнал условия, разряд 26 стробирования мультиплексора из поля логических условий разблокирует этот мультиплексор (при безусловном переходе он его блокирует), разряд 27 адаптирует селектированный сигнал условия так, что его подтверждение было отрицательной полярности. Разряды 28 кода операции несут инФормацию о выборе источника адреса перехода и режима работы стека на случай, если сигнал условия подтвердится. В этом же такте группа 6 дешиФраторов вырабатывает микрооперацию 10. Допустим, что селектируемый сигнал условия не подтвертдается. Тогда на входе 29 регистра 11 в первом такте появляется высокий потенциал (на вход 30 40 регистра 11 в первом такте подключен высокий уровень). Микроопера .ция 10 записывает положительным перепадом н регистр 11 подключенные к информацион ым входам сигналы, в том числе и сигнал условия, осуществляя его синхронизацию. Однако появившийся на выходе 23 потенциал высокого уровня после инвертирования в элементе 14 НЕ и прохождения 50 через элемент И 16 снова устанавливает регистр 11 в исходное состояние,Регистр 11, установившись в исходное состояние, восстанавливает на своем установочном входе высокий потенциал. Во втором такте выходы регистра 11 переписываются в регистр 12, но никаких изменений на входах УФАИ не происходит.Условный перепад не состоялся,Мнкропрограммное устройство управле-,ння по прежнему работает в режимепоследовательной выборки с отклю 5ченным стеком. На фиг. За приведена временная диаграмма условногоперехода для случая с неподтвержденным сигналом условия.Допустим, что селектируемый сигнаал условия подтверждается и предусматривается переход по содержимому внутреннего регистра адресаУ 1. Тогда микрооперацией 10 навыходе 23 регистра 11 записываетсяниэкий потенциал В этом случаерегистр 11 не устанавливается в исходное состояние. Выходы 17 и 20 сохраняют записанный код для УФАМ. Навьходе 21 устанавливается высокийуровень. Этот же потенциал устанавлИвается на втором входе элемента 15.Во втором такте выходы регистра 11переписываются в регистр 12, а разрядь 9 блока памяти микрокоманд, содержащие адрес перехода, записываютсяв регистр адреса УФАМ. В третьемтакте источником адреса выбираемоймнкрокоманды уже явлчется регистрафеса УФАМ (с занесенной в него 30инФормацией),Условный переход состоялся. Сразу после окончания второго такта на выхоце элемента 15 появляется сигнал отрицательной полярности, так как35 на выходах этого элемента подготовленны положительные потенциалы,В результате на установочный вхоо д регистра 11 проходит сигнал,устанавливающий его в исходное сос-. тояние. Выход 21 принимает нулевое значение, тогда сигнал 31 .восстанавливает свою положительную полярность. На фиг. Зб приведена: времен ная диаграмма условного перехода для случая с подтвержденным сигналом условия. Особенность работы устройства заключается в том, что синхронизация и анализ признака условия происходят одновременно с предварительной буферизацией на первом буферном регистре разрядов блока памяти мик 55 рокоманд, что исключают дополнительные временные задержкидля реализаций этих функций и увеличивает быстродействие работы устройства. Формула из о бр ет ения Микропрограммное устройство управления, содержащее мультиплексор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, узел формирования адреса микрокоманды, блок памяти микрокоманд, группу дешифраторов, причем выходы поля логических условий, признака анализа условий и признака инверсии условий блока памяти микрокоманд соединены соответственно с управляющим стробирую-, щим входом мультиплексора. и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы полей логических условий и кода операции блока памяти микрокоманд и признаков анализа условий и инверсии условий соединены с первым информационным входом узла формирования адреса микрокоманды и являются первым информационным выходом устройства, выход поля микроопераций блока памяти микрокоманд соединен с информационными входами дешифраторов группы, выходы которых являются вторым информационным выходом устройства,.выход мультиплексора соединен с вторым входом элемента ИСКЛЮЧАЮИ 1 ЕЕ ИЛИ, информационный вход мультиплексора подключен к выходу логических условий устройства, второй информационный вход узла формирования адреса микрокоманды соединен с входом кода операции устройст-. ва, вход синхронизации узла формирования адреса микрокоманды и входы стробирования дешифраторов группы подключены к входу синхронизации устройства, вход установки в "0" узла формирования адреса микрокоманды подключен к входу установки устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устрочства за счет совмещения во времени операций по буферированию считываемых из блока памяти микрокоманд с синхронизацией и анализом признаков условий, в него введены первый и второй буферные регистры, первый и второй элементы НЕ, элемент И-НЕ, элемент И, причем выход поля кода операции блока памяти микрокоманд соединен с 1-го по Р-й (где Р - разрядность кода операции) информационными входами первого буферного регистра, первый разряд выхода первого буферного регистра соединен с входом первого элементаНЕ, выход которого соединен с первым информационным входом буферного регистра, со второго но (Р+2)-й разряды выхода первого буферного ре 5 гистра соединены с второго по (Р+2)-й информационными входами второго буферного регистра, с первого но Р-й разряды выхода которого соединены с входами кода операции узла формирования адреса микрокоманды (Р+1)-й информационный вход первого буферного регистра соединен с потенциалом логической единицы устройства, (Р+1)-й разряд выхода первого буферного регистра соединен с первым входом элемента И-НЕ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с (Р+2)-м .информационным входом первого буферного регистра (Р+2)-й разряд выхода первого буферного регистра, соединен с входом второго элемента НЕ, выход которого соединен с первым входом элемента И, выход которого соединен с входом установки в "0 первого буферного регистра, первый выход первого дешифратора группы соединен с входом синхронизации первого буферного регистра, выход элемента И-НЕ соединен с вторым входом элемента И, третин вход элемента И соединен с входом становки устройства, вход синхро низации второго буферного регистра соединен свходом синхронизации устройства.1564621 Составитель А.СТехред М.Дидык шки Редактор А,Ог орректор Н,Ревска Заказ 1160 565 Подписное и м при ГКНТ СССР комитета по изаб Москва, Ж, Ра комбинат "Патент, г. Ужгород, ул, Гагарина, 1 П кш 1 роцзводственно-издател ИППИ Гос;дарственного 113035, 1720 2 У

СмотретьЗаявка

4385184, 29.02.1988

ПРЕДПРИЯТИЕ ПЯ А-3517

ВАРАВКА ВЯЧЕСЛАВ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.05.1990

Код ссылки

<a href="https://patents.su/6-1564621-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для управления микропроцессорной системой

Следующий патент: Многоканальное устройство для подключения источников информации к общей магистрали

Случайный патент: Машина для срезания и направленного повала деревьев