Устройство для вычисления булевых функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1517018

Автор: Музыченко

Текст

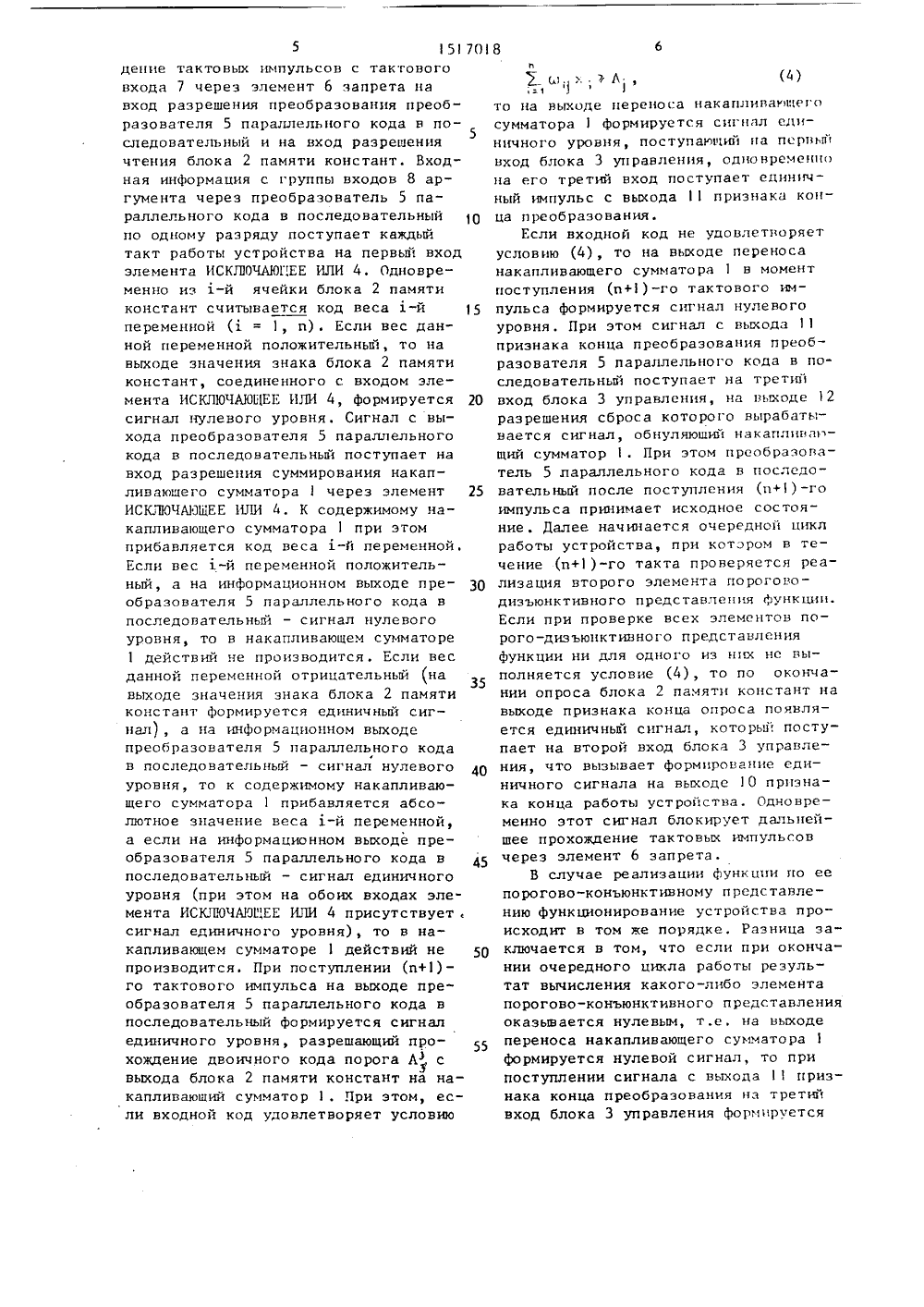

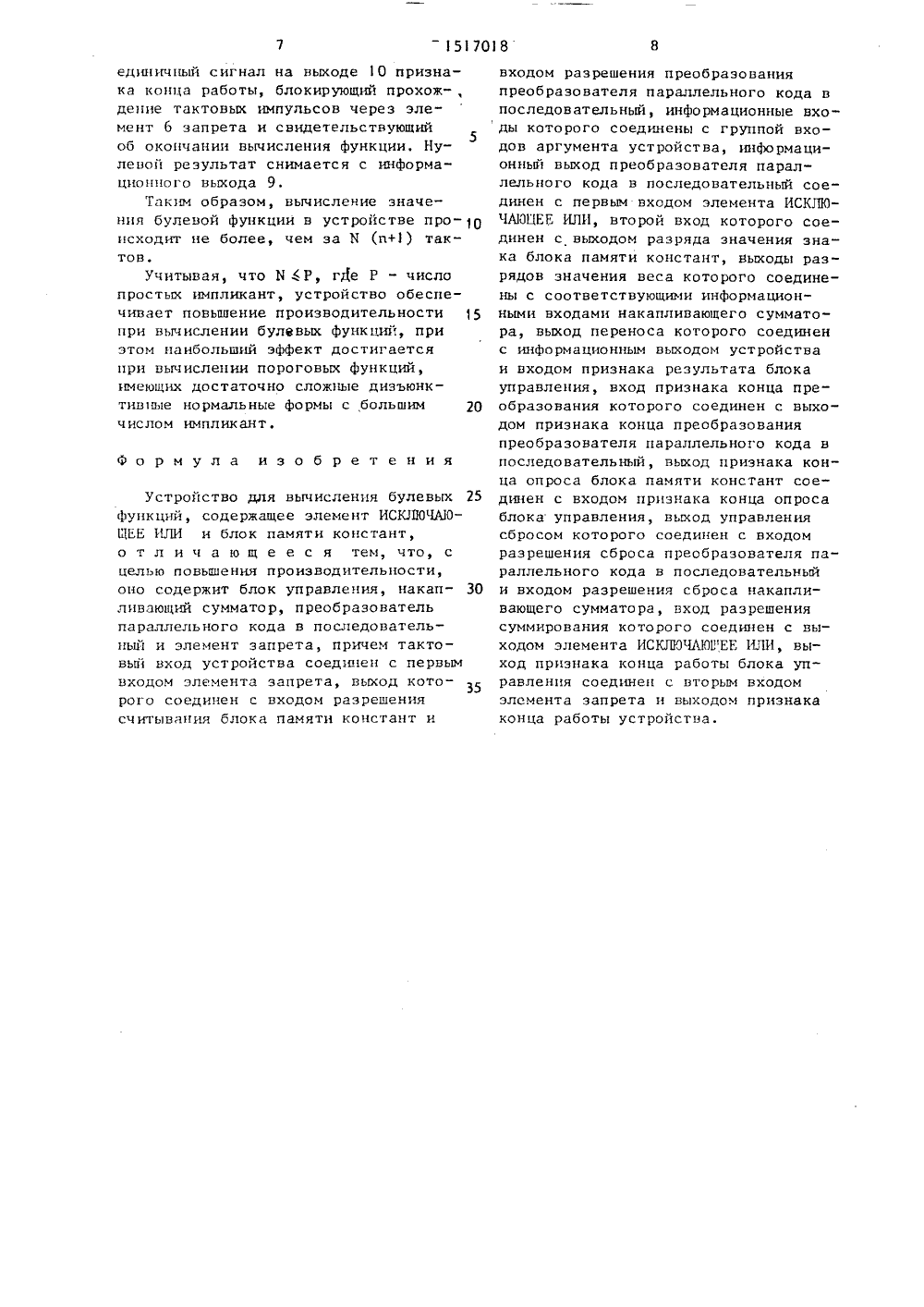

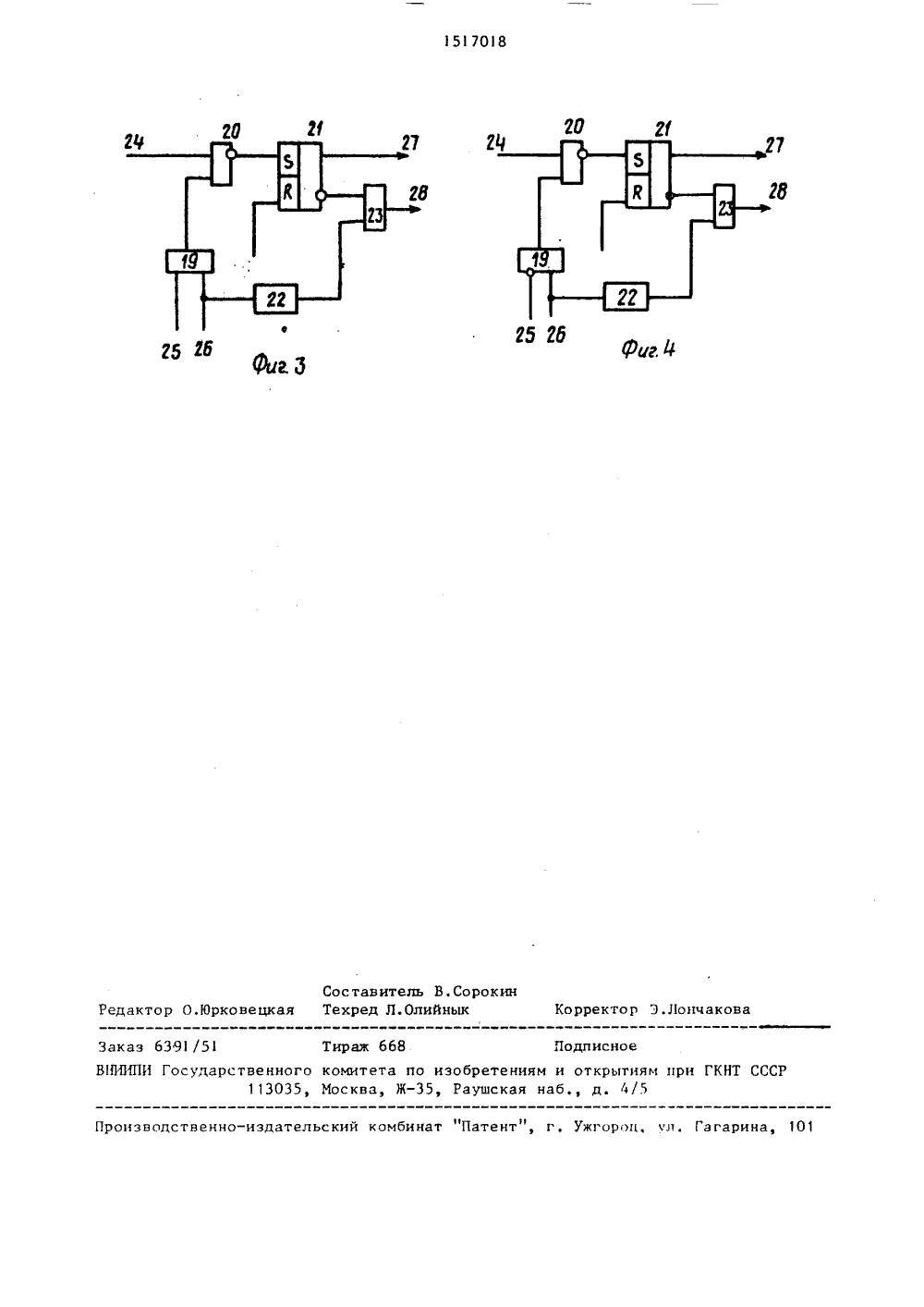

(54) УСТРОЙСТВО ДЛЯ ВЪВЫХ ФУНКЦИЙ(57) Изобретение отнотике и вычислительной ЧИСЛЕН 1 И БУЛ тся к автомаехнике и пред о для вычисле Цель иэобрет эводительност назначенфункцийние про ния - повышеустроиства.ия булевыхливающий сум т вычисления снимареноса накапливающеога. Реэул во для вычисл оис ций тся с выход о сумматора держит нака лок памяти онстант 2, бл9 мато СУДАРСТВЕННЫЙ КОМИТЕТИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМИ П(НТ СССР А ВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторскоек, клАвторское свР 1315965, кл . управления 3, элемент ИСКЛЮЧАЮЩЕЕИЛИ 4, преобразователь 5 параллельного кода в последовательньп и элементзапрета 6. В блок памяти констант последовательно записываются значениязнаков и весов переменных, а такжезначение кода порога. Каждьп такт работы устройства в зависимости от ко -да знака и значения входно. переменной формируется сигнал, поступающийчерез элемент ИСКЛЮЧАЮТЕЕ ИЛИ на входразрешения суммирования накапливаюше -го сумматора, на информационные входы которого подается значение весапеременной. В последнем такте работыустройства из полученной суммы значе- аний весов вычитается значение кодаИзобретение относится к автоматике и вычислительной технике и предназначено для вычисления булевыхФск ций.елсо изобретения является повышение производительности устройства.Нд Фиг.приведена структурнаясхема устройства для вычисления бу -леньх Функпси, на фиг. 2 - пример 1 Осхемы преобразователя параллельногокода н последовательный; на фиг. 3и 4 - варианты реализации блока управления.Устройство для сьчисения булевых 15Функций (Фиг. 1) содержит накапливающий сумматор 1, блок 2 памяти констант, блок 3 управления, элемент ИСКПОЧЛЮ 1 ЕЕ ИЛИ 4, преобразователь 5пдрдл.е:ьного кодд в последовдтель -нысс, э;сомест б запретатактовьдс вход7, группу нходон 8 аргумента, ииформдциосссый выход 9, выход 10 признакак 01 ссд ботыыход1 признака ковцд прсобрдэовдния и выход2 рдэресдессс сброса,Преобрд овдтсль 5 сдралегсьогосодв последвдтельпьдс (фиг. 2) содержит элемент ОП3, первую группуэ;семестон И4. - 14,п+ (п - число30серс сесссьсх реалсэуемой функции), вторус группу элемсстон И 15,- 15.п+1,групу элеместон И-НЕ 16.1 - 1 б.п+1,группу Р.Б-трсггеров 7. - 17.п+ игруспу распределителей 8. - 18.п+импульсон.Блок 3 управления (фиг. 3 и 4) содержит элемент И 1 91 элемент 1 ПИ 20,КБ-трссггер 21, элемент 22 задержки,элеме И 23, второй 24, первый 25 40и троспс 2 б входы, первый 27 и второй 28 вьсходы.Б.сок 3 управления реализуется всоответствии с фиг. 3, если вычисляемая функция представлена в пороговодсзъюпктсвсей форме, и в соответствии с Фсг. 4, если она представленан порогоно-коньюнктивной форме.Ред;изуемдя функция представляется в порогово - дизъюнктивной форме:у =Бдп ы;сх, - А;3 =- порог;- множество номеров переменной с отрицательными весагде ".8 п А1ми;- множество номеров переменных с положительными весапредстдвлена в порогоно-конъюнктивной Форме: сУ= А Бцпсх, - АГ 1и4 8 дпЕ. сд х, +,11- А, +,сс;1= А Ваап, с, х. +С1 Г + , 1 с,;хс - А. (2)ГПри этом запись информации в блок 2 памяти констант осуществляется в том же порядке.Разрядность блока 2 памяти констант определяется в соответствии с формулой г = 1 о 8 К+ (3) где К = дах. 1 ы; , АУс трой ство при реал из ации функ циипо ее порогово-дизъюнктинному представлению работает следующим образомВ исходном состоянии накапливающий сумматор 1, преобразователь 5параллельного кода в последовательный и блок 3 управления обнулены,при этом на выходе 10 признака концаработы устройства формируется сигнал11 11логического 0 , р а з решающий п р охожми;щ - разрядность накапливающегосуьдчатора .При этом в блок 2 памяти констант устройства последовательно записываются значения весов переменных сс, с 1, ь и значение кода порогатА = 2 - АПричем в аэряльс ячеекЭ,1значенсся веса блока 2 памяти констант записывается двоичньдс код веса соответствующей входной переменной, а в разряд значения знака блока 2 памяти констант - признак знака веса: 011 для положительного веса идля отрицательного, После записи вссов всех переменных записывается дноичньпс кодспорога Л с признаком эсака, равным 11011Реализуемая Функцья может бытьдение тактовых ипульсов с тактового входа 7 через элемент 6 запрета на вход разрешения преобразования преобразователя 5 параллельного кода н по 5 следовательный и на вход разрешения чтения блока 2 памяти констант. Входная информация с группь входов 8 аргумента через преобразователь 5 параллельного кода в последовательный по одному разряду поступает каждый такт работы устройства на первьп вход элемента ИСКЛ 10 ЧАЮ 1 ЕЕ ИЛИ 4. Одновременно из 1-й ячейки блока 2 памяти констант считывается код веса 1-й 15 переменной ( = 1, и). Если вес данной переменной положительньп, то на выходе значения знака блока 2 памяти констант, соединенного с входом элемента ИСКЛЮЧАЮЦЕЕ ИЛИ 4, формируется 20 сигнал нулевого уровня. Сигнал с выхода преобразователя 5 параллельного кода в последовательный поступает на вход разрешения суммирования накапливающего сумматора 1 через элемент 25 ИСКЛЮЧАЫЦЕЕ ИЛИ 4. К содержимому накапливающего сумматорапри этом прибавляется код веса д-й переменной. Если вес 1-й переменной положительный, а на информационном выходе пре образонателя 5 параллельного кода в последовательньп - сигнал нулевого уровня, то в накапливающем сумматоре 1 действий не производится. Если вес данной переменной отрицательный на выходе значения знака блока 2 памяти констант формируется единичный сигал), а на информационном выходе преобразователя 5 параллельного кодаФ в последовательный - сигнал нулевого 40 уровня, то к содержимому накапливающего сумматора 1 прибавляется абсолютное значение веса .-й переменной, а если на информационном выходе преобразователя 5 параллельного кода в 45 последовательный - сигнал единичного уровня (при этом на обоих входах элемента ИСК 1 ПОЧАЩЕЕ ИЛИ 4 присутствует, сигнал единичного уровня), то в накапливающем сумматоредействий не производится. При поступлении (и+1) - го тактового импульса на выходе преобразователя 5 параллельного кода в последовательный формируется сигнал единичного уровня, разрешающий прохождение двоичного кода порога А с выхода блока 2 памяти констант на накапливающий сумматор 1. При этом, если входной код удовлетворяет условию юА(4) то на ныходе переносаакаплваюпего сумматораформируется сигнал единичного уровня, поступаюпи на первый вход блока 3 управления, одновременно на его третий вход поступает ецинич - ньй импульс с выхода 11 признака конца преобразования.Если входной код не удовлетворяет условию (4), то на выходе переноса накапливающего сумматора 1 н момент поступления (и+1) -го тактового импульса формируется сигнал нулевого уровня. При этом сигнал с выхода 11 признака конца преобразования преоб - разователя 5 параллельного кода в последовательньп поступает на трет вход блока 3 управления, на выходе 12 разрешения сброса которого вырабатынается сигнал, обнуляющвп накапливающий сумматор 1. При этом преобразователь 5 лараллельного кода в последовательньп после поступления (и+1) -го импульса принимает исходное состояние . Далее начинается очередной цикл работы устройства, при котором н течение (и+1)-го такта проверяется реализация второго элемента порогонодизъюнктивного представления функции. Если при проверке всех элементон по- рого-дизъюнктивного представления Функции ни для одного из них нс выполняется условие (4), то по окончании опроса блока 2 памяти констант на выходе признака конца опроса появляется единичньп сигнал, которьп: поступает на второй вход блока 3 управления, что вызывает формирование еди - ничного сигнала на выходе 10 прзна - ка конца работы устройства. Сднонременно этот сигнал блокирует дальнейшее прохождение тактовых импульсов через элемент 6 запрета.В случае реализации Функц по ее порогово-конъюнктивному представлению функционирование устройства происходит в том же порядке, Разница заключается в том, что если при окончании очередного цикла работы результат вычисления какого-либо элементапорогово-конъюнктивного представления оказывается нулевым, т.е. на выходе переноса накапливающего сумматораформируется нулевой сигнал, то при поступлении сигнала с выхода 11 признака конца преобразования на третий вход блока 3 управления Формируетсяединичный сигнал на выходе 1 О признака конца работы, блокирующий прохож-, дение тактовых импульсов через элемент 6 запрета и свидетельствующий об окончании вычисления функции. Нулевой результат снимается с информационного выхода 9.Таким образом, вычисление значения булевой функции в устройстве про исходит не более, чем за Н (п+1) тактов.Учитывая, что БР, гДе Р - число простых импликант, устройство обеспечивает повышение производительности 15 при вычислении булевых функций, при этом наибольший эффект достигается при вычислении пороговых функций, имеющих достаточно сложные дизъюнктивиые нормальные формы с большим 20 числом импликант.формулаизобретенияУстройство для вычисления булевых 25 функций, содержащее элемент ИСКЛЮЧАЮПЕЕ ИЛИ и блок памяти констант, о т л и ч а ю щ е е с я тем, что, с целью повышения производительности, оно содержит блок управления, накап ливающий сумматор, преобразователь параллельного кода в последовательный и элемент запрета, причем тактовый вход устройства соединен с первым входом элемента запрета, выход которого соединен с входом разрешения считывания блока памяти констант и входом разрешения преобразованияпреобразователя параллельного кода впоследовательный, информационные входы которого соединены с группой входов аргумента устройства, информационный выход преобразователя параллельного кода в последовательный соединен с первым входом элемента ИСКЛЮЧАЮЦЕЕ ИЛИ, второй вход которого соединен с выходом разряда значения знака блока памяти констант, выходы разрядов значения веса которого соединены с соответствующими информационными входами накапливающего сумматора, выход переноса которого соединенс информационным выходом устройстваи входом признака результата блокауправления, вход признака конца преобразования которого соединен с выходом признака конца преобразованияпреобразователя параллельного кода впоследовательный, выход признака конца опроса блока памяти констант соединен с входом признака конца опросаблока управления, выход управлениясбросом которого соединен с входомразрешения сброса преобразователя параллельного кода в последовательныйи входом разрешения сброса накапливающего сумматора, вход разрешениясуммирования которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход признака конца работы блока управления соединен с вторым входомэлемента запрета и выходом признакаконца работы устройства.15 7018 го 24 21 20 Составитель В. СорокинТехред Л.Олийнык Корректор Э.Лоичако Редактор О.Юрковецк КНТ СССР Производственно в издательск комбинат "Патент", г, Ужгород, ул. Гагарина, 10 аказ 639 /511 ИИПИ Государственног113035 Тираж бб 8комитета по иМосква, Ж,Подписноебретениям и открытиямаушская наб., д, 4/5

СмотретьЗаявка

4392202, 14.03.1988

ВОЙСКОВАЯ ЧАСТЬ 31303

МУЗЫЧЕНКО ОЛЕГ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: булевых, вычисления, функций

Опубликовано: 23.10.1989

Код ссылки

<a href="https://patents.su/6-1517018-ustrojjstvo-dlya-vychisleniya-bulevykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления булевых функций</a>

Предыдущий патент: Устройство для вычисления симметрических булевых функций

Следующий патент: Устройство для вычисления булевых функций

Случайный патент: Устройство для обработки кости