Устройство для обнаружения и исправления ошибок в блоках памяти

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

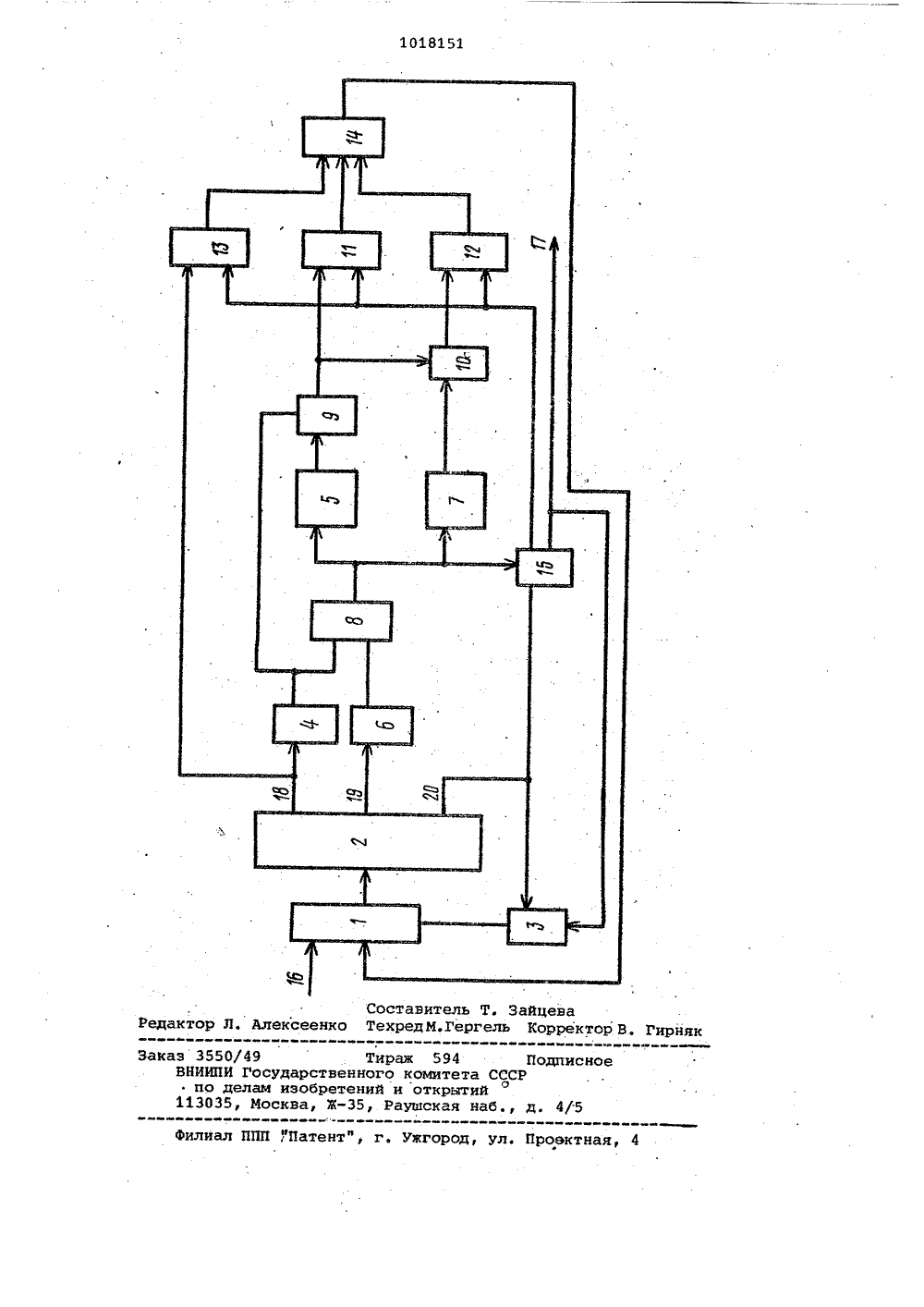

аЕ ИВ11 : ГОСУДАРСТВЕННЫЙ КОМИТЕТ СОИ ГФ ДЕЛАМ ИЗО 6 РЕТ 94 ИЙ,И ОТМЕПЮ ОПИСАНИЕ Н 800 (21) 3354581/18-.24 .дешиФратаров подключены соответствен- (22) 20,11.81 .,но к:одним из вкодов элементов ИЛИ, . (46) 15,05.83.: Бюл.918 о тл и ч а ю.щ е е с я тем, что, (72) А.В. Иаркарян и Л.М. Чахоян с целью повиаения быстродействия 53); б 81.327(088.8)устройства, в него"введены.третий (6) 1. патент (ъж В. 4064483,и четвертыйпреобразователи кодов, кл. 340-14 б.1 А, опублик. 1977, третий дешиФратор и сумматоры, причем2. Патент ОНА В 40300 б 7, кл.340- . . входн Третьего преобразователя: кодов 14 б.1 АЬ,:опублик.1977 (прототип)соединены с другими вйходами ФормнроЗ,Берлекзмп. З.,Апгебраическаятеорйя-. 1 вателя контрольных сигналов, одинкрдирования, И., фйирф, 1971, с.134,,из выходов которого является управ- . 135,156,151.,:ляющим, выходы третьего преобразова 4. мак-Вйльямс Теория кодов, ис- - теля кодов-щщключены к одним из вхоправляющих саибки. И., "Связь", 1979, дов первого.сумматора,.другие входы с.91,. .которого соединены.с выходами первого (54)(57) УСТРОЙСТВО.:ДЛЯ ОБНАРУЖЕНИИ преобразователя кодов и одними из И .ИСПУАЮЗЕНИй ОЫНВОК: В БЛОКАХ ПАИЯти, Входов втоРого сУиматоРа, дРУгие Я . содержашее блок управления, блок кор- аноды которого подключены к выходам рекций, формирователь контрольных второго преобразователя кодов, а высигнаяов,:первый и второй предобра-" . ходы - к одним из входов первого зователи кодов,:дешйФраторы, .элемен- дешнФратора и третьего.сумматора, выты ИЛИ и:элемейты .И, причем одни из ходы которого саедииены с одним нз .входов блока коррекции являются входов второго дешнФратора, а дру- о входаин устройства, другие входыгие входы - с выходами четвертого блока, коррекции подключены соответст- преобразонателя кодов, входы которог венно к выходу блока управления и к соединены с выходами первого сумма- выходам элементов ИЛИ, а выходы - - , тора, входащ второГо преобразоватек входам Формирователя .контрольных " . ля кодов .и другии входами элементов сигналов, одни из выходов которогоИ,.другой выход которых подключен соединены соответственно с входами :к другим входам первого и второго первого преобразователя кодов и .сдешифраторов и одним йз входов, третье-" однйми из входов элементов И, один йз го дешнФратора, другие входы кото- выходов которых. соединей с входом:рого соединены с входами первого блока управления и является выходом . преобразователя кодов, а выходы - устройства; выходы первого и второго с другими входами"элементов или, 1018151Изобретение относится к запоминающим устройствам и может быть использовано для контроля оперативных и постоянных запоминающих устройств.Известно устройство для обнаружения и исправления ошибок в блокахпамяти, в котором используется блоквозведения в куб для коррекции двойных ошибок и принцип последовательного перебора со сравнением соответствующих значений для обнаруженияместа ошибочного бита информации ЦНедостатком этого устройства является,низкое быстродействие.Наиболее блиэкйм к изобретениюявляется устройство для.обнаружения 15исправления ошибок в блоках памяти, содержащее блок управления,регистр информации, генератор контрольного сигнала, два блока умножения,два преобразователя кода, два дешиф- рратора, элементы ИЛИ и И, причемпервые входы регистра информацииподключены к входам устройства, вторые - к выходам элемента ИЛИ, третийвход - к выходу блока управления, 2а выходы - к входам генератора контрольного сигнала, первые выходы которого подключены к входам первогопреобразователя кода, третий выход -к входу элемента И, первый выходкоторого йодключен к первому входублока управления и к выходу устройства, выходы первого и второго дешифраторов подключены к входам элемента ИЛИ 21.Недостатком этого устройства является низкое быстродействие вследствие того, что время исправления одиночных и двойных ошибок в регистреинформации одинаково,а скоростьисправления двойных и обнаружения 40тройных ошибок обусловлейа использованием двух медленно действующихблоков умножения. Цель изобретения - повышение 45 быстродействия устройства.Поставленная цель достигается тем, что в устройство для обнаружения и исправления ошибок в блоках памяти, содержащее блок управления, блок коррекции, формирователь контрольных сигналов, первыйи второй преобразователи кодов, дешифраторы, элементы ИЛИ и элементы И, причем одни из входов блока коррекции являются входами устройетва, другие входы блока коррекции подключены соответственно к выходу блока управления и к выходам элементов ИЛИ, а выходы - к входам формирователя контрольных сигналов, одни из выходов бО которого соединены соответственно с входами первого преобразователя кодов и с одними из входов элементов И, один из выходов которых соединен с входом блока управления и у является выходом устройства, выходыпервого и второго дешифраторовподключены соответственно к однимнз входов элементов ИЛИ, введенытретий и четвертый преобразователикодов, третий дешифратор и сумматоры,причем входы третьего преобразователя кодов соединены с другими выходамиформирователя контрольных сигналов,один из выходов которого являетсяуправляющим, выходы третьего преобразователя кодов подключены к одним извходов первого сумматора, другие вхо-ды которого соединены с выходами первого преобразователя кодов и однимииэ входов второго сумматора, другиевходы которого подключены к выходамвторого преобразователя кодов, а выходы - к одним из входов первогодешифратора и третьего сумматора,выходы которого соединены с однимиз входов второго дешифратора, адругие входы - с выходами четвертого преобразователя кодов, входы которого соединены с выходами первогосумматора, входами второго преобразователя кодов и другими входамиэлементов И, другой выход которыхподключен к другим входам первогои второго дешифраторов и одним извходов третьего дешифратора, другиевходы которого соединены с входамипервого преобразователя кодов, а выходы - с другими входами элементовИЛИ,На чертеже изображена функциональная схема предложенного устройства,устройство содержит блок 1 коррекции, формирователь 2 контрольных сигналов, блок 3 управления,первый 4 второй 5, третий 6 и четвертый 7 нреобразователи кодов, первый 8, второй 9 и третий 10 сумматоры, первый 11, второй 12 и третий13 дешифраторы, элементы ИЛИ 14 иэлементы И 15. На чертеже обозначены входы 16 и один из выходов 17устройства, выходы 18, 19 и 20 формирователя контрольных сигналов.Устройство работает следующимобразом.С входа 16 поступает К +1) -разрядный код (где К - целое числов параллельной форме на запись вблок 1, с выхода которого этот кодпоступает в формирователь 2,В случае одиночной ошибки в К+1)- разрядном коде на выходах 18 формирователя 2 вырабатывается код коррекцииошибки 5, а на выходе 20 - сигналнечетной ошибки, который поступаетна второй вход блока 3. Код коррекции ошибки поступает на первые входыдешифратора 13, который через элементы Ю 1 И 14 на входы блока 1 выдаеткод, указыванзций неисправный разряд в блоке 1, одновременно с выходаблока 3 на вход блока 1 поступаетсигнал, разрешающий коррекцию. В результате в блоке 1 корректируется .поступивший в него код.В случае двойной ошибки в К +1)- разрядном коде на Выходах 18 и 19формирователя вырабатываются соответственно коды коррекции ошибок5 и , а на выходе 20 сигнал.не-.четной ошибки отсутствует. Коды Б;,исоответственно поступают навходы преобразователей 4 и б. Преобразователь 4 выдает на входы сумматоров 8 и 9 Ьр(к+1)- разрядный код Ра преобразователь б выдаетна другие входы сумматора 8 й 3 к+1)- разрядный код . . С выхода сумматора 8 на входы преобразователей 5 и 7и элементов И 15 поступает результатсуммцр+)МО по мод К . При(р+)Ф 0и отсутствии сигнала нечетной ошибки на выходе 20 с выходов элементовИ 15 на вход дешифратора 13 выдается сигнал блокировки, а на входы дешифраторов 11 .и 12 - сигналы разблокировки:. Преобразователь 5.выдаетна другйе входи суьвиатора.:9 ФЦВ 1)- разрядный код. С выходов сумматора 9код и поступает: на, одни иэ входовдешифратора-и на входы сумматора 10,на другие входы которого поступает0 ОЩк+12- разрядный, код Х. Реэультагсложения этих кодов с выходов суякатора 10 поступает на одни из выходов дешйФратора 12. Дешифраторы 11 и 12 через элементы ИЛИ 14 .на входы блока1 выдают код, указывающий неисправные разряды в блоке 1, на вход которого с вйхода блока 3 одновременнопоступает сигнал, разрешающий коррекцию. В результате код в блоке 1 кор,ректируется.В случае тройной ошибки в(К+Ц-40разрядном коде на входе 1 б в отличиеот двойной приор+) ФО и наличии сиг нала нечетной ошибки на выходе 20формирователя 2 на вцход 17 элементов И 15 и на первый вход блока 3выдается сигнал тройной ошибки, а сдругих .выходов элементов И 15 на входдешифратора 13 поступает сигнал раэблокировки, а на входы дешифраторов11 и 12 - сигнал блокировки.При этом. коррекция информации вблоке 1 производится дважды: сначалапо сигналу нечетной ошибкив соответ.ствии с кодом Я осуществляетсякоррекция в блоке 1 так же, как ир случае одиночной ошибки в поступив-.шем на вход 16 коде, а затем блок3 по сигналу тройной ошибки, выдаетсигнал, разрешающий коррекцию такжев соответствии с кодом. Такимобразом, информация в блоке 1 вос.станавливается, а на выход 17 выдается сигнал тройной ошибкн.В случае отсутствия ошибки в пос-тупившем на вход 16 коде Формирователем 2 вырабатываются нулевые кодыЯ. и 3,. а сигнал нечетной ошибкиотсутствует. В результате информацияв блоке 1 остается без изменения,Коррекция информации.в блоке 1осуществляется в соответствии с алгоритмами 3) и 43.Таким образам, в предложенномустройстве в отличие от прототипавместо медленно действующих блоковумножения использованы быстродействующие сумматоры, а коррекция одиночной ошибки производится по максимально укороченному пути, что позволяетзначительно сократйть время коррекции,одиночных, двойных и обнаружения тройных ошибок,Технико-экономическое преимущест-.во предложенного устройства заключается в его более высоком быстро"действии по сравнению с прототипом.Составитель Т. Зайцеваактор Л. Алексеенко ТехредМ.Гергель Корректновае т ня ПодписноеР ву Де Филиал ППП,"Патент", г. Ужгород, ул. Проектная, 4 Заказ 3550/49 ВНИИПИ Государственн по делам изобретен 113035, Москва, 3-35

СмотретьЗаявка

3354581, 20.11.1981

ПРЕДПРИЯТИЕ ПЯ А-7390

МАРКАРЯН АШОТ ВАГАНОВИЧ, ЧАХОЯН ЛЕОНИД МИКАЕЛОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: блоках, исправления, обнаружения, ошибок, памяти

Опубликовано: 15.05.1983

Код ссылки

<a href="https://patents.su/4-1018151-ustrojjstvo-dlya-obnaruzheniya-i-ispravleniya-oshibok-v-blokakh-pamyati.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и исправления ошибок в блоках памяти</a>

Предыдущий патент: Запоминающее устройство

Следующий патент: Резервированное запоминающее устройство

Случайный патент: Способ буксировки тел и устройство для его осуществления