Устройство для обнаружения ошибок в двухступенчатом модулярном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

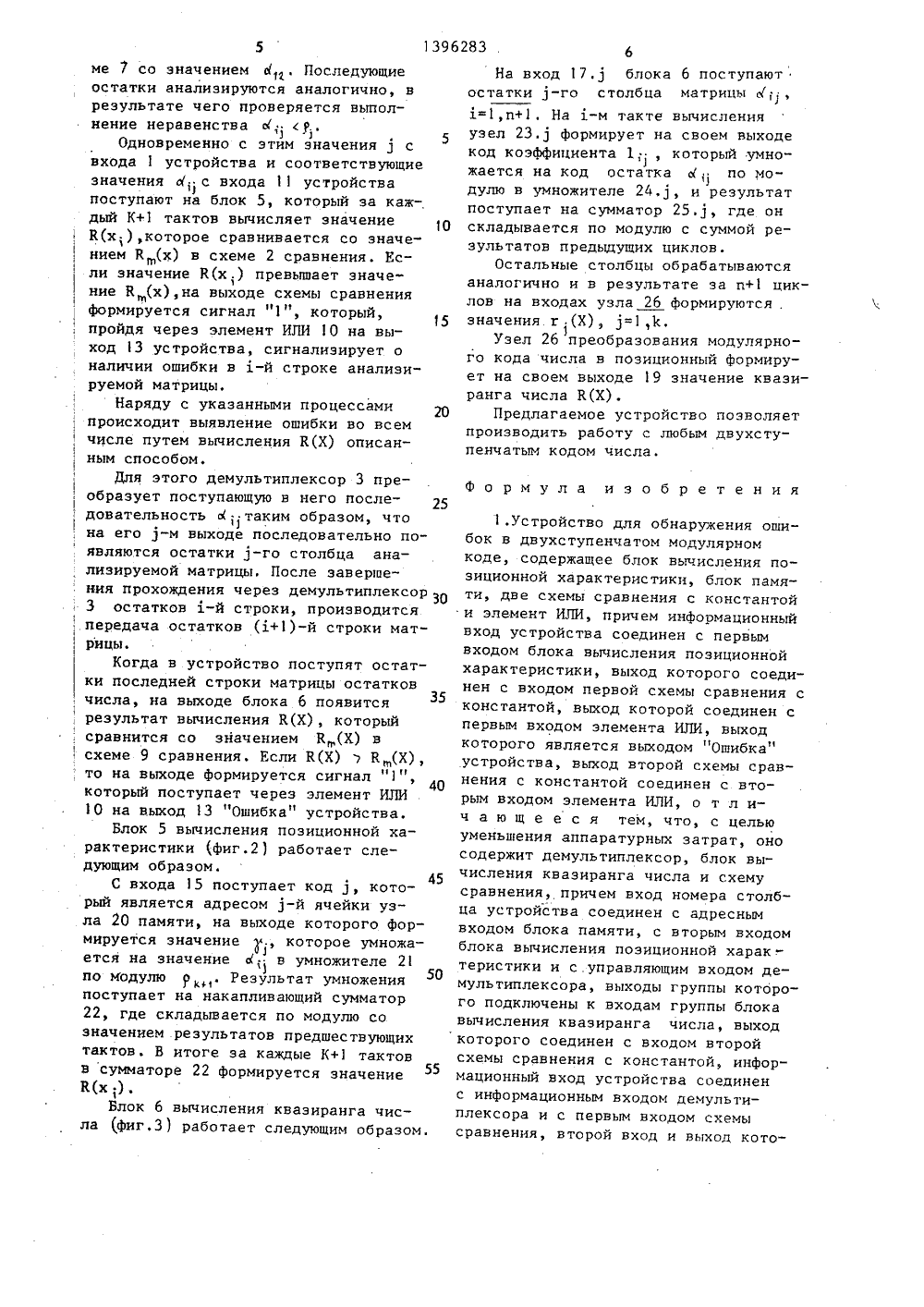

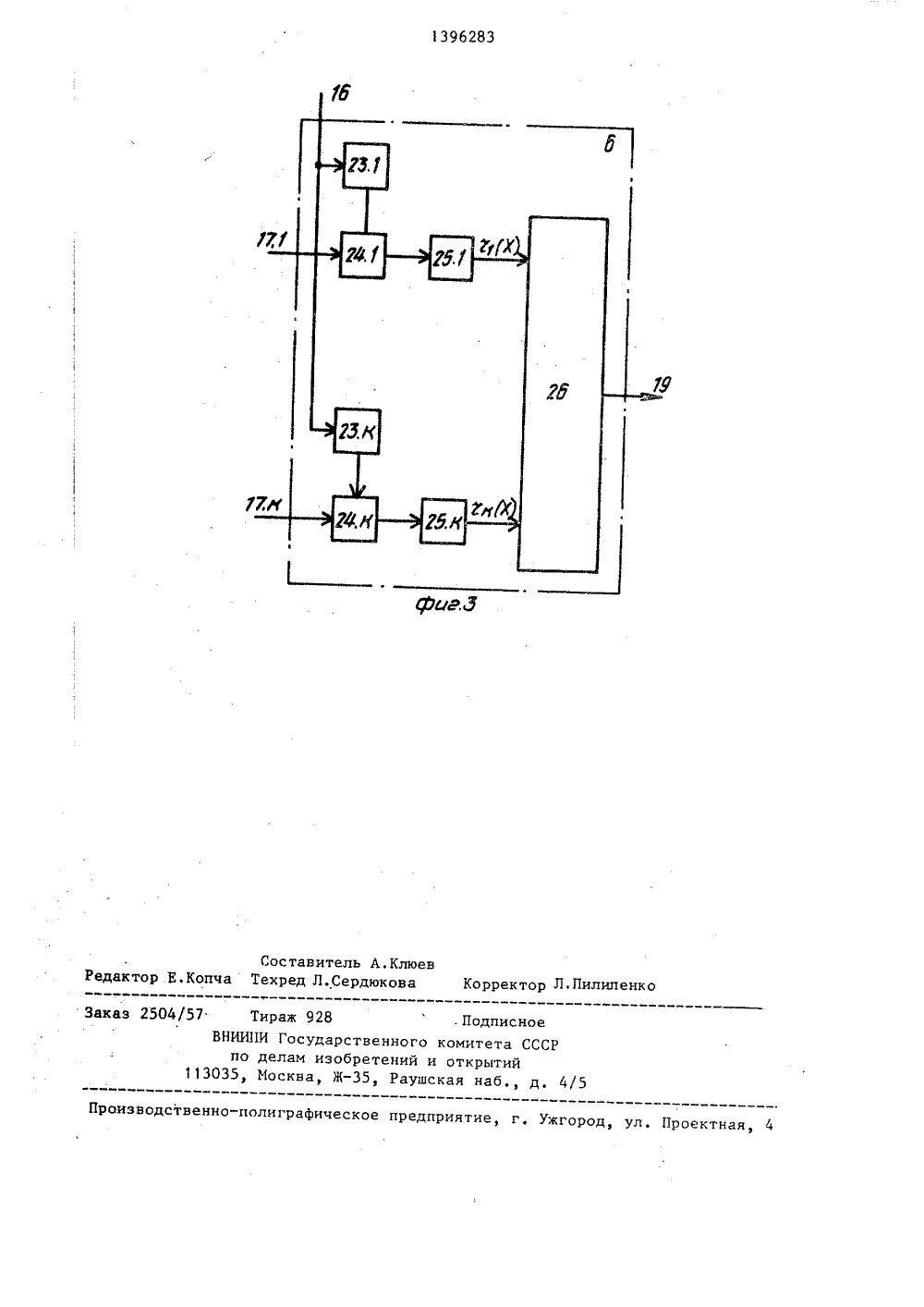

СОЮЗ СОВЕТСКИСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК Н 03 М 13/ ОПИСАНИЕ ИЗОБРЕТЕН ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ Н АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство СССР У 1238078, кл.С 06 Р 11/08, 1984.Авторское свидетельство СССР В 862143, кл. Н 03 М 13/00, 1979. (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК В ДВУХСТУПЕНЧАТОМ МОДУЛЯРНОМ КОДЕ(57) Изобретение относится к области вычислительной техники и может быть использовано для контроля в вычислительных устройствах, функционирующих в системе остаточных классов, атакже для обнаружения ошибок в системах передачи информации, представленной модулярными кодами. Цельюизобретения является уменьшение аппаратурных затрат. Поставленная целдостигается тем что устройство дляобнаружения ошибок в двухступенчатомодулярном коде, содержащее блок 4памяти, блок 5 вычисления позиционной характеристики, две схемы 8,9сравнения с константой и элементИЛИ 1 О, содержит демультиплексор 3,блок 6 вычисления квазиранга числасхему 7 сравнения с соответствующимсвязями. 2 з,п. ф-лы, 3 ил.В своей работе устройство (фиг,1) использует следующее.Представим число Х из диапазонасовокупностью остатков х .Х 1 р, по взаимно простым основани 1 иямР;, где х = 1,п+1, а У=П Р,.55 Таким образом, в рассматриваемом коде основание Р ь, является избыточ-. ным. Пусть выбранная система оснований упорядочена, т.е,50 Изобретение относится к вычислительной технике и может быть использовано для контроля в вычислительных устройствах, функционирующих в системе остаточных классов, а также в сис 5 темах передачи информации, представленной модулярными кодами.Целью изобретения является уменьшение аппаратурных затрат.На фиг.1 приведена схема устройства для обнаружения ошибок в двухступенчатом модулярном коде; на фиг.2 - схема блока вычисления позиционной характеристики; на фиг.З схема блока вычисления кваэиранга числа.Устройство (фиг.1) содержит входы 1 и 2 номера столбца и номера строки устройства, демультиплексор 3, блок 4 памяти, блок 5 вычисления позиционной характеристики, блок 6 вычисления квазиранга числа, схему 7 сравнения, схемы 8 и 9 сравнения с константой, элемент ИЛИ 1 О, информа ционный вход 11 устройства, первый вход 12 схемы 7 сравнения, выход 13 "Ошибка" устройства, второй вход 14 схемы 7 сравнения, вход 15 блока 5 вычисления позиционной характеоисти ки, вход 16 блока 6 вычисления квази- ранга числа, группу входов 17,1-17.К блока 6 вычисления квазиранга числа, выход 18 блока 5 вычисления позиционной характеристики и выход 19 блока 6 вычисления квазиранга числа.Блок 5 вычисления позиционной характеристики (фиг.2) содержит узел 20 памяти, умножитель 21 по модулю и сумматор 22 по модулю. 40Блок 6 вычисления квазиранга числа (фиг.З) содержит группу узлов 23.1-23.К памяти, группу умножителей 24.1-24.К по модулю, группу сумматоров 25.1-25.К по модулю и узел 26 45 преобразования модулярного кода в позиционный код. Каждый остаток х;,ь =1,и+1, представим системой остатков и = х .1 Р по взаимно простым основаниям Р3 где 1 = 1,1 с+1. Система оснований второй ступени так же упорядоченная, а основаниеь избыточное, т,е, Р, сП Р.=Уиь 1В результате имеем двухступенчатый модулярный код числа Х, который можно представить в виде матрицы остатков.Х=Остатки анализируемого числа Х поступают на вход устройства последовательно, по строкам.Процесс контроля ошибок в принимаемой совокупности остатков1 состоит из трех этапов, Необходимо определить меньше ли принятый остаток ; основания Р Если да, то процесс контроля можно продолжать дальше, если нет, то делаем вывод о возникновении ошибки. Необходимо проверить принадлежность совокупности остатков ; ь;, разрешенной кодовой комбинации. Если анализируемое число правильно, то оно принадлежит нулевому пространству избыточного модулярного кода (в данном случаеф ) и значение квазирангакэтого чйсла К(х,) лежит в пределах О,К (х) . Если произойдет ошибка, то искаженное число выйдет за пределы указанного диапазона и его квази- ранг К(х ) превысит некоторое гранич - ное значение К (х), Это свойство функции квазиранг позволяет обнаруживать ошибки в избыточном модуляр ном коде. Значение квазиранга строки определяется какКь 1К(х,) =Р КЬ 1где коэффициенты у. определяются3следующим образом для1где щ веса базисных чисел системы основа- "ний р второйступенид К()х Необходимо, располагая совокупностью остатков х;, д=1 и+1, проверить принадлежность числа Х к диапазону),Р , и только в этом случаеего можно считать правильным. 20В общем случае контроль указанной совокупности остатков Х; не отличается от описанного процесса контроля совокупности остатков Ы;,Для упрощения технической реализации квазиранг определяется по формуле г (Х)В к гХХ)В;(р 130 кПр,1=( р э) М т) ) базисные числа системы оснований1-1 второй ступени;45 веса базисных чиселсистемы основанийР;, =1-и первойступени; 50 ее 1;1= 11.;(1-К,(Х): (Р -1) 100% для первой ступени; Процент обнаруживаемых ошибок определяется по формуле 55второй ступени.1Систему оснований необходимо подбирать таким образом, чтобы гранич " ное значение квазиранга было как можно меньше избыточного основания.Демультиплексор 3 распределяет остатки Ы; входа 1 на К своих выходов в зависимости от значенияна входе 1.Все блоки памяти, используемые в устройстве, представляют собой постоянные запоминающие устройства, в ячейки которых записаны нужные коэффициенты, и адресом к ним является состояние соответствующего входа 1 и 2 устройства.Схема 7 сравнения формирует сигнал "1" на своем выходе, когда код на выходе блока 4 бОльше, чем на входе 11.Схемы 8 и 9 сравнения выдают сигнал, если их входной код превысит значения К;(х) и К,(Х) соответственно.В блоке 5 вычисления позиционной характеристики умножитель 21 и накапливающий сумматор 22 выполнены по модулю 9В блоке б вычисления квазиранга числа умножители 24.3 и накапливающие сумматоры 25. выполнены по модулю 1)Устройство (фиг.1) работает следующим образом.В исходном состоянии все сумматоры обнулены, узел 26 преобразования модулярного кода в позиционный готов к преобразованию, на входах 1 и 2 устройства - "1".Работа устройства начинается в момент появления на входе 11 кода первого остатка Ы(, величина которого сравнивается схемой 7 со значением кода основания р установленного на выходе блока 4 памяти, и, если первое значение превьппает второе, на выходе схемы 7 формируется сигнал "1", который проходит через элемент ИЛИ 10 на выход 13 устройства, что означает наличие ошибки в анализируемом остатке, Далее на вход 11 подается код следующего остаткасопровождаемый значением два на входе 1 устройства, что вызывает формирование на выходе блока 4 значе ния р, которое сравнивается в схе 1396283ме У со значением Ы . Последующие остатки анализируются аналогично, в результате чего проверяется выполнение неравенства с; су35Одновременно с этим значения 1 с входа 1 устройства и соответствующие значения ," с входа 11 устройства1)поступают на блок 5, который за каждый К+ тактов вычисляет значение К(х;),которое сравнивается со значением К (х) в схеме 2 сравнения. Есйли значение К(х.) превышает эначение К (х),на выходе схемы сравнения формируется сигнал "1", который, пройдя через элемент ИЛИ 1 О на выход 13 устройства, сигнализирует о наличии ошибки в х-й строке анализируемой матрицы.Наряду с указанными процессами происходит выявление ошибки во всем числе путем вычисления К(Х) описанным способом.Для этого демультиплексор 3 преобразует поступающую в него после 11довательность Ы таким образом, что на его 1-м выходе последовательно появляются остатки 1-го столбца анализируемой матрицы. После завершения прохождения через демультиплексор З 0 Э остатков 1-й строки, производитсяпередача остатков (+1)-й строки матрицы.Когда в устройство поступят остатки последней строки матрицы остатков35 числа, на выходе блока 6 появитсярезультат вычисления К(Х), который сравнится со значением К (Х) всхеме 9 сравнения. Если К(Х) ) К (Х),то на выходе формируется сигнал, 40 который поступает через элемент ИЛИ1 0 на выход 13 "Ошибка" устройства,Блок 5 вычисления позиционной характеристики 1,фиг.2) работает следующим образом.45С входа 15 поступает код 1, который является адресом 1-й ячейки узла 20 памяти, на выходе которого формируется значение ., которое умножается на значение Ы; в умножителе 21по модулю 0 ,. Результат умножения50поступает на накапливающий сумматор22, где складывается по модулю созначением результатов предшествующихтактов . В итоге за каждые К+1 тактовв сумматоре 22 формируется значениеК(х;) .Блок 6 вычисления кваэиранга числа (фиг,3 работает следующим образом. На вход 17.1 блока 6 поступают остатки 1-го столбца матрицы,п+1. На 1-м такте вычисления узел 23.3 формирует на своем выходе код коэффициента 1; , который умножается на код остатка Ы, по модулю в умножителе 24,1, и результат поступает на сумматор 25.1, где он складывается по модулю с суммой результатов предыдущих циклов.Остальные столбцы обрабатываются аналогично и в результате за и+ циклов на входах узла 26 формируются . значения г (Х), 1=1,1 с,Узел 26 преобразования модулярного кода числа в позиционный формирует на своем выходе 19 значение квази- ранга числа К(Х).Предлагаемое устройство позволяет производить работу с любым двухступенчатым кодом числа. Формула изобретения1.Устройство для обнаружения ошибок в двухступенчатом модулярном коде, содержащее блок вычисления позиционной характеристики, блок памяти, две схемы сравнения с константой и элемент ИЛИ, причем информационный вход устройства соединен с первым входом блока вычисления позиционной характеристики, выход которого соединен с входом первой схемы сравнения с константой, выход которой соединен с первым входом элемента ИЛИ, выход которого является выходом "Ошибка" устройства, выход второй схемы сравнения с константой соединен с вторым входом элемента ИЛИ, о т л ич а ю щ е е с я тем, что, с целью уменьшения аппаратурных затрат, оно содержит демультиплексор, блок вычисления квазиранга числа и схему сравнения, причем вход номера столбца устройства соединен с адресным входом блока памяти, с вторым входом блока вычисления позиционной харак.- теристики и с,управляющим входом демультиплексора, выходы группы которого подключены к входам группы блока вычисления кваэиранга числа, выход которого соединен с входом второй схемы сравнения с константой, информационный вход устройства соединен с информационным входом демультиплексора и с первым входом схемы сравнения, второй вход и выход кото 1396283рой соединены соответственно с выходом блока памяти и с третьим входомэлемента ИЛИ, вход номера строкиустройства соединен с входом блокавычисления квазиранга числа. 2. Устройство по и.1, о т л и - ч а ю щ е е с я тем, что блок вычисления позиционной характеристики содержит узел памяти, умножитель по модулю и сумматор по модулю, причем первый и второй входы блока вычисления позиционной характеристики соединены соответственно с входом пер вого сомножителя умножителя по модулю и с адресным входом узла памяти, выход которого соединен с входом второго сомножителя умножителя по модулю, выход которого соединен с входом сумматора по модулю, выход которого является выходом блока вычисления позиционной характеристики. 3. Устройство по п.1, о т л и - ч а ю щ е е с я тем, что блок вычисления кназиранга числа содержит группу узлов памяти, группу умножителей по модулю, группу сумматоров по модулю и узел преобразования модулярного кода в позиционный код, причем вход блока вычисления кваэиранга числа соединен с адресными входами узлов памяти группы, выходы которых соединены с входами первых сомножителей соответствующих умножителей по модулю группы, выходы которых соединены с входами соответствующих сумматоров по модулю группы, выходы которых соединены с соответствующими входами узла преобразования модулярного кода в позиционный код, выход которого является выходом блока, входы группы которого соединены с входами вторых сомножителей соответствующих умножителей группы.1396283 Заказ 2504/ Тираж 92 ВНИИПИ Госуд по делам и 035, Москва, Подписное арственного комитета СССРзобретений и открытий Ж, Раушская наб д,Производственно-полиграфическое предприятие, г, Ужгород, ул. тная Составитель А.Клюеведактор Е,Копча Техред Л.Сердюкова Корректор Л.Пилипенко

СмотретьЗаявка

4176891, 21.11.1986

СТАВРОПОЛЬСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. 60-ЛЕТИЯ ВЕЛИКОГО ОКТЯБРЯ

АКУЛИНЧЕВ АНДРЕЙ БОРИСОВИЧ, ХЛЕВНОЙ СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: H03M 7/18

Метки: двухступенчатом, коде, модулярном, обнаружения, ошибок

Опубликовано: 15.05.1988

Код ссылки

<a href="https://patents.su/6-1396283-ustrojjstvo-dlya-obnaruzheniya-oshibok-v-dvukhstupenchatom-modulyarnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок в двухступенчатом модулярном коде</a>

Предыдущий патент: Вероятностный мажоритарный декодер

Следующий патент: Устройство коррекции частотных характеристик

Случайный патент: Уборочная машина