Модуль программируемого коммутатора

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

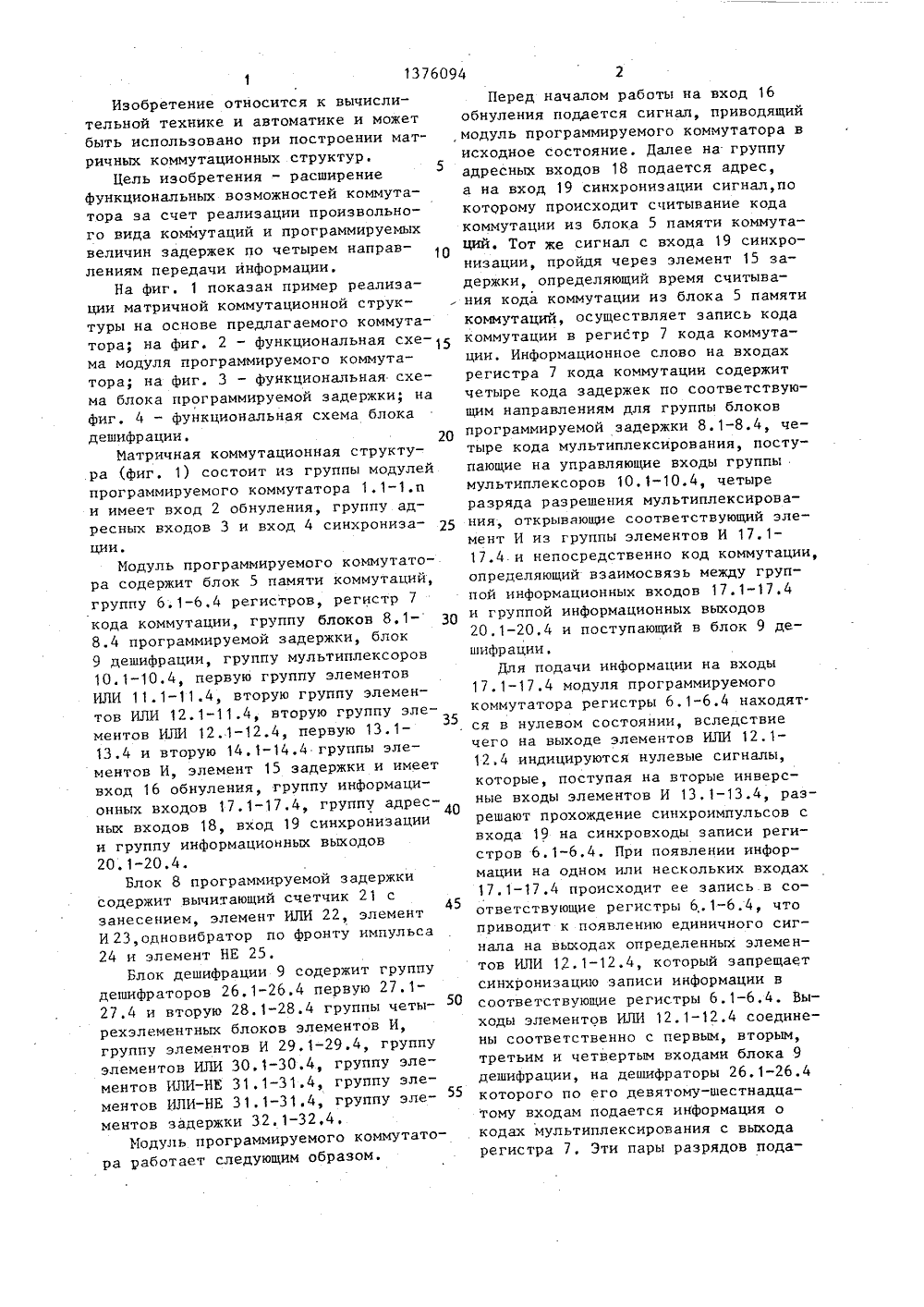

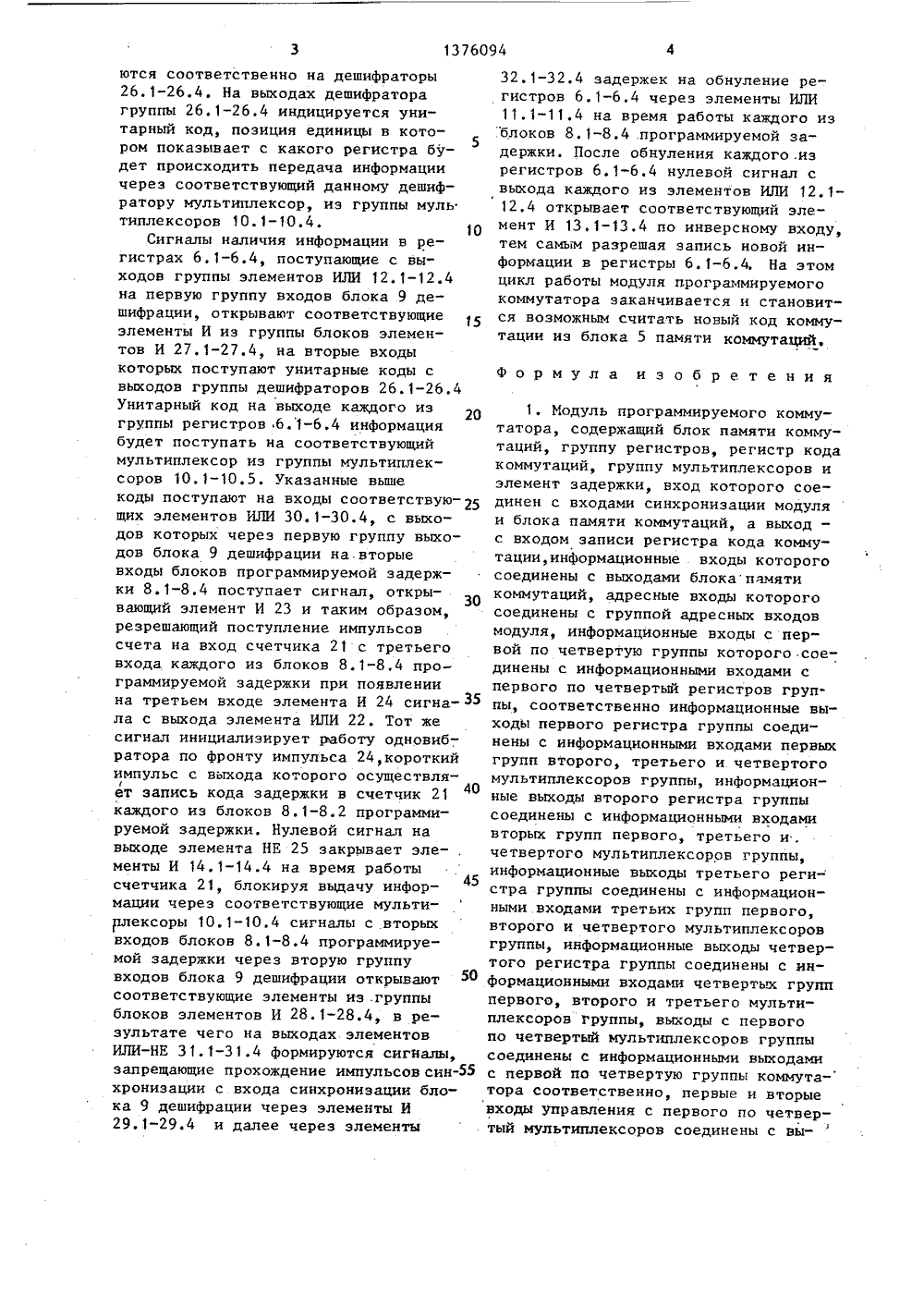

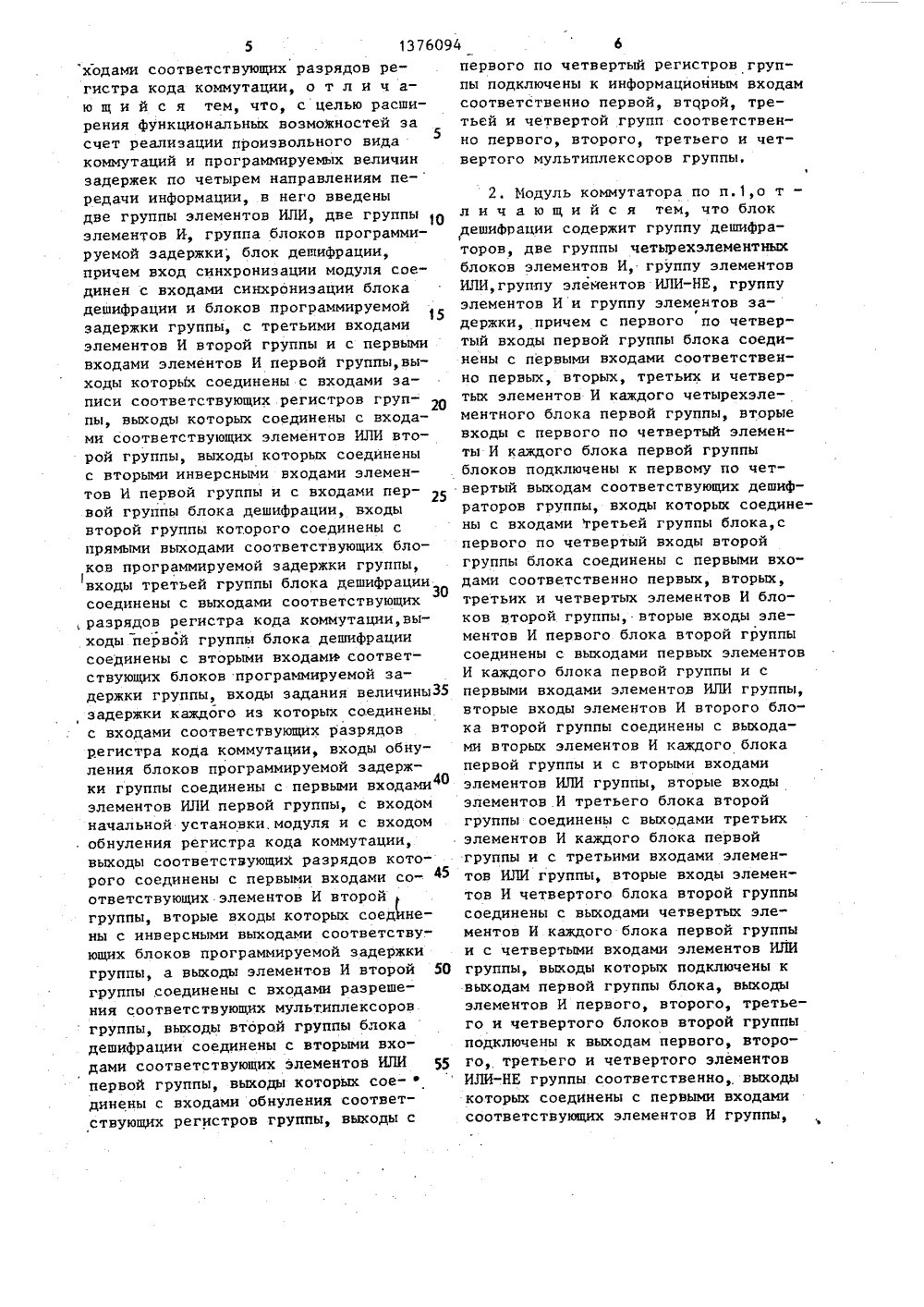

(57) Изобретелительной техможет быть ис ие относится квычисике и автоматике и ользовано при пост Ж С) ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ(56) Авторское свидетельство СССРВ 1121778, кл. С 06 Р 7/00, 1983.Авторское свидетельство СССРВ 1280596, кл . 6 06 Г 1/00, 985.,ЯО 326094 А 1 ении матричных коммутаторов информации, а также в системах коммутацииданных многопроцессорных вычислительных структурЦелью изобретенияявляется расширение функциональныхвозможностей модуля программируемогокоммутатора, а именно реализация произвольных коммутаций типа "с любоговхода - на любой выход" при условиинесмешивания информации с разных входов. Кроме того, реализована возможность создания программируемой задержки на каждом маршруте прохождения информации. Поставленная цельдостигнута за счет дополнительноговведения двух групп элементов ИЛИ,двух групп элементов И, группы блоков программируемой задержки и блокадешифрации 1 з.п. ф-лы, 4 ил, 1376094Изобретение относится к вычислительной технике и автоматике и можетбыть использовано при построении матричных коммутационных структур,Цель изобретения - расширениефункциональных возможностей коммутатора за счет реализации произвольного вида коммутаций и программируемыхвеличин задержек по четырем направлениям передачи информации.На фиг. 1 показан пример реализации матричной коммутационной структуры на основе предлагаемого коммутатора; на фиг. 2 - функциональная схема модуля программируемого коммутатора; на фиг. 3 - функциональная схема блока программируемой задержки; нафиг. 4 - функциональная схема блокадешифрации.20Матричная коммутационная структура (фиг. 1) состоит из группы модулейпрограммируемого коммутатора 1.1-1,пи имеет вход 2 обнуления, группу адресных входов 3 и вход 4 синхронизации.Модуль программируемого коммутатора содержит блок 5 памяти коммутаций,группу 6.1-6,4 регистров, регистр 7кода коммутации, группу блоков 8.1- 308.4 программируемой задержки, блок9 дешифрации, группу мультиплексоров10.1-10,4, первую группу элементовИЛИ 11.1-11,4, вторую группу элементов ИЛИ 12. 1-11,4 вторую группу зле е )35ментов ИЛИ 12.1-12,4, первую 13.1 -13.4 и вторую 14,1-14.4 группы элементов И, элемент 15 задержки и имеетвход 16 обнуления, группу информационных входов 17,1-17.4 группу адресных входов 18, вход 19 синхронизациии группу информационных выходов20.1-20.4.Блок 8 программируемой задержкисодержит вычитающий счетчик 21 с45занесением, элемент ИЛИ 22, элементИ 23,одновибратор по фронту импульса24 и элемент НЕ 25.Блок дешифрации 9 содержит группудешифраторов 26.1-26.4 первую 27,127.4 и вторую 28.1-28.4 группы четырехэлементных блоков элементов И,группу элементов И 29,1-29,4, группуэлементов ИЛИ 30,1-30.4, группу элементов ИЛИ-НЕ 31.1-31,4, группу элементов ИЛИ-НЕ 31.1-31,4, группу элементов задержки 32.1-32,4,Модуль программируемого коммутатора работает следующим образом. Перед началом работы на вход 16 обнуления подается сигнал, приводящий модуль программируемого коммутатора в исходное состояние, Далее на группу адресных входов 18 подается адрес, а на вход 19 синхронизации сигнал,по которому происходит считывание кода коммутации из блока 5 памяти коммутаций. Тот же сигнал с входа 19 синхронизации, пройдя через элемент 15 задержки, определяющий время считывания кода коммутации из блока 5 памяти коммутаций, осуществляет запись кода коммутации в регистр 7 кода коммутации. Информационное слово на входах регистра 7 кода коммутации содержит четыре кода задержек по соответствующим направлениям для группы блоков программируемой задержки 8,1-8.4, четыре кода мультиплексирования, поступающие на управляющие входы группы мультиплексоров 10.1-10.4, четыре разряда разрешения мультиплексирования, открывающие соответствующий элемент И из группы элементов И 17.1- 17.4.и непосредственно код коммутации, определяющий взаимосвязь между группой информационных входов 17.1-17,4 и группой информационных выходов 20.1-20.4 и поступающий в блок 9 дешифрацииДля подачи информации на входы 17,1-17.4 модуля программируемого коммутатора регистры 6,1-6.4 находят. ся в нулевом состоянии, вследствие чего на выходе элементов ИЛИ 12.1- 12.4 индицируются нулевые сигналы, которые, поступая на вторые инверсные входы элементов И 13,1-13.4, разрешают прохождение синхроимпульсов с входа 19 на синхровходы записи регистров 6. 1-6,4. При появлении информации на одном или нескольких входах 17.1-17.4 происходит ее запись в соответствующие регистры 6.1-6.4, что приводит к появлению единичного сигнала на выходах определенных элементов ИЛИ 12.1-12.4, который запрещает синхронизацию записи информации в соответствующие регистры 6.1-6,4. Выходы элементов ИЛИ 12,1-12.4 соединены соответственно с первым, вторым, третьим и четвертым входами блока 9 дешифрации, на дешифраторы 26,1-26,4 которого по его девятому-шестнадцатому входам подается информация о кодах мультиплексирования с выхода регистра 7. Эти пары разрядов пода 1376094ются соответственно на дешифраторы 26, 1-26.4, На выкодах дешифратора группы 26,1-26.4 индицируется унитарный код, позиция единицы в котором показывает с какого регистра бу 5 дет происходить передача информации через соответствующий данному дешифратору мультиплексор, из группы муль типлексоров 10.1-10.4.Сигналы наличия информации в регистрах 6,1-6.4, поступающие с выходов группы элементов ИЛИ 12. 1-12.4 на первую группу входов блока 9 дешифрации, открывают соответствующие элементы И из группы блоков элементов И 27. 1-27.4, на вторые входы которых поступают унитарные коды с выкодов группы дешифраторов 26.1-26.4 Унитарный код на выходе каждого из группы регистров 6.1-6.4 информация будет поступать на соответствующий мультиплексор из группы мультиплексоров 10.1-10.5. Указанные выше коды поступают на входы соответствую 25 щих элементов ИЛИ 30. 1-30,4, с выходов которых через первую группу выходов блока 9 дешифрации на.вторые входы блоков программируемой задержки 8.1-8.4 поступает сигнал открыУ 30 вающий элемент И 23 и таким образом, резрешающий поступление импульсов счета на вход счетчика 21 с третьего входа каждого из блоков 8.1-8,4 программируемой задержки при появлении на третьем входе элемента И 24 сигна ла с выхода элемента ИЛИ 22. Тот же сигнал инициализирует работу одновибратора по фронту импульса 24,короткий импульс с выхода которого осуществля/ет запись кода задержки в счетчик 21 каждого из блоков 8.1-8.2 программируемой задержки, Нулевой сигнал на выходе элемента НЕ 25 закрывает эле-, менты И 14. 1-14.4 на время работы счетчика 21, блокируя выдачу информации через соответствующие мультирлексоры 10.1-10,4 сигналы с вторых входов блоков 8. 1-8.4 программируемой задержки через вторую группу входов блока 9 дешифрации открывают соответствующие элементы из .группы блоков элементов И 28.1-28,4, в результате чего на выходах элементов ИЛИ-НЕ 3 1.1-31.4 формируются сигналы, запрещающие прохождение импульсов синхронизации с входа синхронизации блока 9 дешифрации через элементы И 29,1-29.4 и далее через элементы 32.1-32,4 задержек на обнуление регистров 6,1-6,4 через элементы ИЛИ 11.1-11,4 на время работы каждого из блоков 8.1-8,4 .программируемой задержки. После обнуления каждого .из регистров 6.1-6,4 нулевой сигнал с выхода каждого из элементов ИЛИ 12. 1- 12,4 открывает соответствующий элемент И 13.1-13.4 по инверсному входу, тем самым разрешая запись новой информации в регистры 6,1-6.4. На этом цикл работы модуля программируемого коммутатора заканчивается и становится возможным считать новый код коммутации из блока 5 памяти коммутаций.формула изобретения1. Модуль программируемого коммутатора, содержащий блок памяти коммутаций, группу регистров, регистр кода коммутаций, группу мультиплексоров и элемент задержки, вход которого соединен с входами синхронизации модуля и блока памяти коммутаций, а выход - с входом записи регистра кода коммутации,информационные входы которого соединены с выходами блокапамяти коммутаций, адресные входы которого соединены с группой адресных входов модуля, информационные входы с первой по четвертую группы которого соединены с информационными входами с первого по четвертый регистров группы, соответственно информационные выходы первого регистра группы соединены с информационными входами первых групп второго, третьего и четвертого мультиплексоров группы, информационные выходы второго регистра группы соединены с информационными входами вторых групп первого, третьего и, четвертого мультиплексоров группы, информационные выходы третьего регистра группы соединены с информационными. входами третьих групп первого, второго и четвертого мультиплексоров группы, информационные выходы четвертого регистра группы соединены с информационными входами четвертых групп первого, второго и третьего мультиплексоров Группы, выходы с первого по четвертый мультиплексоров группы соединены с информационными выходами с первой по четвертую группы коммутатора соответственно, первые и вторые входы управления с первого по четвертый мультиплексоров соединены с вы137 б 094 6первого по четвертый регистров группы подключены к информационным входам и- соответственно первой, второй, треза тьей и четвертой групп соответствен 5но первого, второго, третьего и чети вертого мультиплексоров группы,ходами соответствующих разрядов регистра кода коммутации, о т л и ч а ю щ и й с я тем, что, с целью расш рения функциональных возможностей счет реализации произвольного вида коммутаций и программируемых величи задержек по четырем направлениям пе-редачи информации, в него введены две группы элементов ИЛИ, две группы элементов И, группа блоков программируемой задержки, блок дешифрации, причем вход синхронизации модуля соединен с входами синхронизации блока дешифрации и блоков программируемой задержки группы, с третьими входами элементов И второй группы и с первыми входами элементов И первой группы,выходы которьйс соединены с входами записи соответствующих регистров группы, выходы которых соединены с входами соответствующих элементов ИЛИ второй группы, выходы которых соединены с вторыми инверсными входами элементов И первой группы и с входами пер 25 вой группы блока дешифрации, входы второй группы которого соединены с прямыми выходами соответствующих блоков программируемой задержки группы, входы третьей группы блока дешифрации соединены с выходами соответствующих , разрядов регистра кода коммутации,выходы первой группы блока дешифрации соединены с вторыми входами соответствующих блоков программируемой задержки группы, входы задания величины 35 задержки каждого из которых соединены.с входами соответствующих разрядов регистра кода коммутации, входы обну" ления блоков программируемой задержки группы соединены с первыми входами элементов ИЛИ первой группы, с входом начальной установки, модуля и с входом . обнуления регистра кода коммутации, выходы соответствующих разрядов которого соединены с первыми входами со ответствующих элементов И второйгруппы, вторые входы которых соедйнены с инверсными выходами соответствующих блоков программируемой задержки группы, а выходы элементов И второй 50 группы соединены с входами разрешения соответствующих мультиплексоров группы, выходы второй группы блока дешифрации соединены с вторыми входами соответствующих элементов ИЛИ 55 первой группы, выходы которых сое-динены с входами обнуления соответствующих регистров группы, выходы с 2. Модуль коммутатора по п.1,о т - л и ч а ю щ и й с я тем, что блок дешифрации содержит группу дешифраторов, две группы четырехэлементных блоков элементов И, группу элементов ИЛИ,группу элементов ИЛИ-НЕ, группу элементов И и группу элементов задержки, причем с первого по четвертый входы первой группы блока соединены с первыми входами соответственно первых, вторых, третьих и четвертых элементов И каждого четырехэлементного блока первой группы, вторые входы с первого по четвертый элементы И каждого блока первой группы блоков подключены к первому по четвертый выходам соответствующих дешифраторов группы, входы которых соединены с входами третьей группы блока,с первого по четвертый входы второй группы блока соединены с первыми входами соответственно первых, вторых, третьих и четвертых элементов И блоков второй группы, вторые входы элементов И первого блока второй группы соединены с выходами первых элементов И каждого блока первой группы и с первыми входами элементов ИЛИ группы, вторые входы элементов И второго блока второй группы соединены с выходами вторых элементов И каждого блока первой группы и с вторыми входами элементов ИЛИ группы, вторые входы элементов И третьего блока второй группы соединены с выходами третьих элементов И каждого блока первой группы и с третьими входами элементов ИЛИ группы, вторые входы элементов И четвертого блока второй группы соединены с выходами четвертых элементов И каждого блока первой группы и с четвертыми входами элементов ИЛИ группы, выходы которых подключены к выходам первой группы блока, выходы элементов И первого, второго, третьего и четвертого блоков второй группы подключены к выходам первого, второго, третьего и четвертого элементов ИЛИ-НЕ группы соответственно, выходы которых соединены с первыми входами соответствующих элементов И группы, 1376094вторые входы которых соединены свходом синхронизации блока, а выходы - соединены с входами соответствующих элементов задержки группы,выходы которых подключены к выходамвторой группы блока,

СмотретьЗаявка

4085019, 27.05.1986

ЛЕНИНГРАДСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. М. И. КАЛИНИНА

САМОШИН ВЛАДИМИР НИКОЛАЕВИЧ, ЕФРЕМОВ ВЛАДИМИР ДМИТРИЕВИЧ, НИКОНОВ ВАЛЕНТИН ВЯЧЕСЛАВОВИЧ, МЕЛЬНИКОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, САМОШИН СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 15/177

Метки: коммутатора, модуль, программируемого

Опубликовано: 23.02.1988

Код ссылки

<a href="https://patents.su/6-1376094-modul-programmiruemogo-kommutatora.html" target="_blank" rel="follow" title="База патентов СССР">Модуль программируемого коммутатора</a>

Предыдущий патент: Устройство для связи микропроцессорных модулей с магистралью

Следующий патент: Устройство для сопряжения эвм

Случайный патент: Устройство для очистки ковша экскаватора