Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

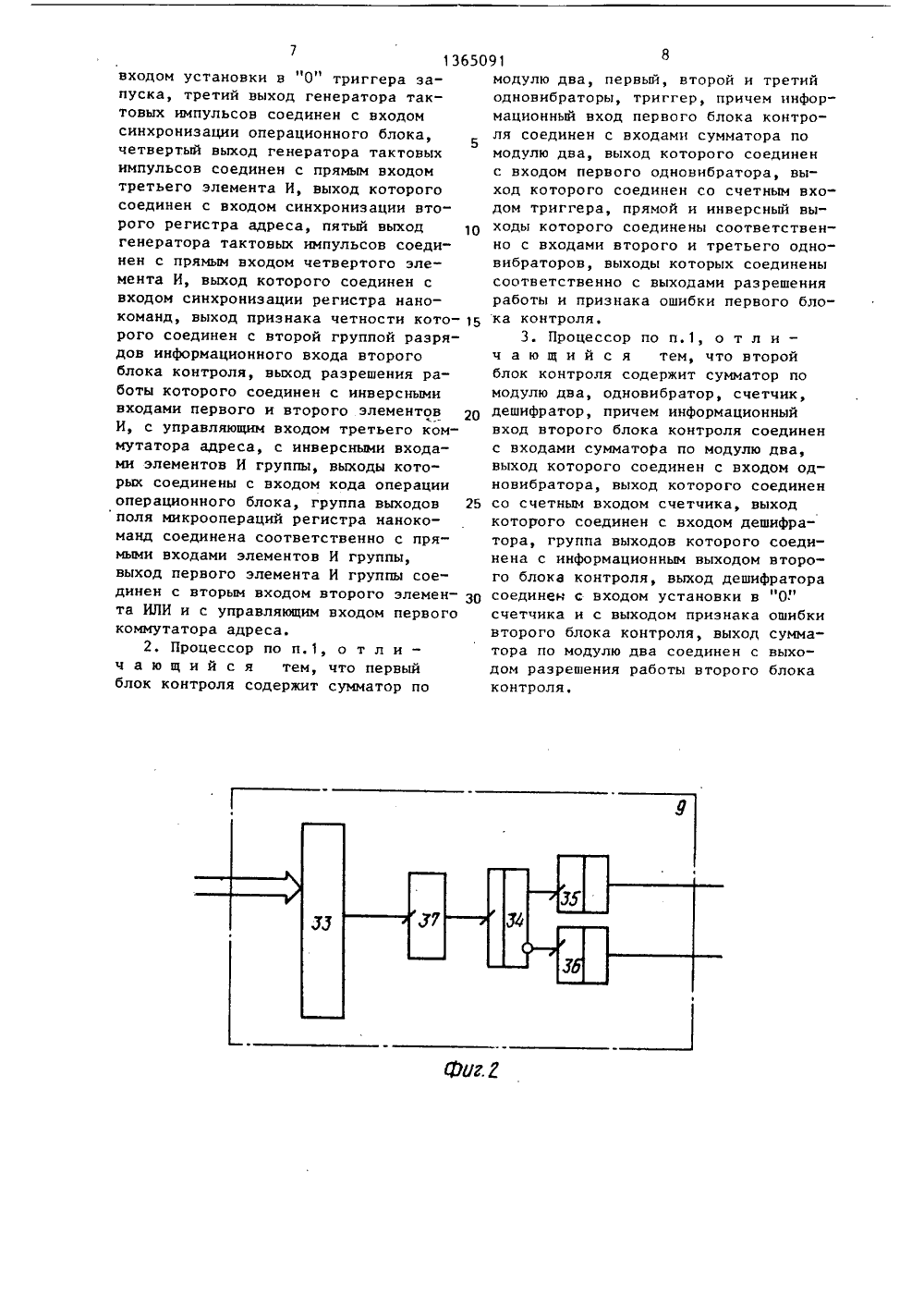

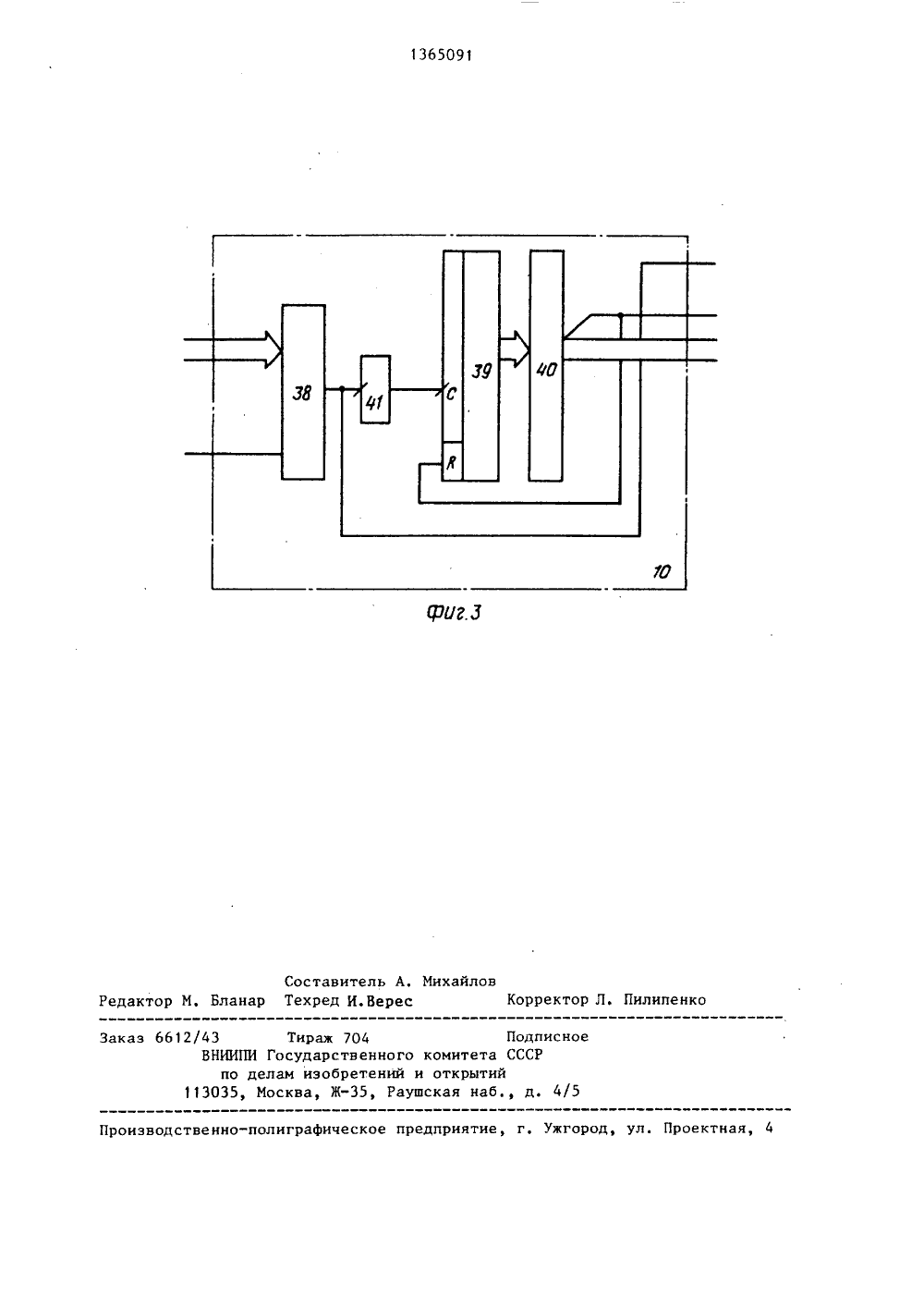

(57) Изобретение относится к вычислительной технике и может быть исМе ербауправния -онипользован в микроп емах. Це остоверн ляющи повыш си ие оиства.памят 2,-2 ассоци ровани держит группу манд, регист о СССР 1981 СССР 1982нд ок блок 1 блоковблок 3р 4 ком льст 15/О яти, тр 5 ство 15/О анд, первыи рег ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ВТОРСНОМУ СВИДЕТЕЛЬСТ(56) Авторское свидетеУ 1024927, кл. С 06 РАвторское свидетельВ 1037264, кл. С 06 Р оцессорныхь изобретсти функциУстройствмикрокомпамяти нативной пам1365091 адреса, регистр 6 микрокоманд, второй регистр 7 адреса, регистр 8 нанокоманд, первый блок 9 контроля, второй блок 10 контроля, коммутатор 11,первый коммутатор 12 адреса, второйкоммутатор 13 адреса, третий коммутатор 14 адреса, мультиплексор 15 логических условий, группу элементовИ 16, триггер 17 запуска, триггер Изобретение относится к вычислительной технике и может найти широкое применение в информационных, управляющих и вычислительных системах, в частности в микропроцессорных уп равляющих системах.Цель изобретения - повышение достоверности функционирования процессора.На фиг. 1 представлена функцио 10 нальная схема микропрограммного процессора; на фиг. 2 - функциональная схема первого блока контроля; на фиг. 3 - функциональная схема второ 15 го блока контроля.Микропрограммный процессор (фиг.1) содержит блок 1 памяти микрокоманд, группу блоков 2.1-2.п памяти нано- команд, блок 3 ассоциативной памяти, регистр 4 команд, первый регистр 5 адреса, регистр 6 мчкрокоманд с полями: полем 6.1 проверяемого логического условия, полем 6.2 модифицированного разряда адреса, полем 6.3 немодифицируемых разрядов адреса, полем 6.4 адреса нанокоманды и полем 6.5 признака четности информации, второй регистр 7 адреса, регистр 8 нанокоманд, первый 9 и второй 10 блоки контроля, коммутатор 11, первый 12, второй 13 и третий 14 коммутаторы адреса, мультиплексор 15 логических .условий, группу элементов И 16, триггер 17 запуска, триггер 18 отказа, генератор 19 тактовых импульсов, группу элементов НЕ 20, первый 21, второй 22, третий 23 и четвертый 24 элементы И, второй элемент ИЛИ 25, первый элемент ИЛИ 26, адновибратор40 27, операционный блок 28, вход 29 кода команды, управляющий вход 30,18 отказа, генератор 19 тактовых импульсов, группу элементов НЕ 20, первый 21, второй 22, третий 23, четвертый 24 элементы И, второй 25, первый26 элементы ИЛИ, одновибратор 27,операционный блок 28. Указаннаяцель достигается с помощью вышеуказанной совокупности признаков. 2 з,п.ф-лы, 3 ил. вход 31 данных и выход 32 процессора(результата).Первый блок 9 контроля (фиг. 2)содержит сумматор 33 по модулю два,счетный триггер 34, первый 35, второй 36 и третий 37 одновибраторы,Второй блок 10 контроля (фиг3)содержит сумматор 38 по модулю два,счетчик 39, дешифратор 40, одновибратор 41.Микропрограммный процессор работает следующим образом,В исходном состоянии элементы памяти устройства находятся в нулевомсостоянии (за исключением триггерарегистра 8 нанокоманд, определяющегоокончание выдачи управляющего слована операционный блок 28).Работа процессора начинается путемподачи на вход 29 процессора кодавыполняемой команды, Данный код заносится в регистр 4 команд. При поступлении на вход 30 процессора сигнала на начало работы триггер 17 запуска устанавливается в единичноесостояние и разрешает тем самым формирование тактовых импульсов с выходов генератора 19 для синхронизацииработы процессора. Так как признакошибки по операционному каналу отсутствует, то по первому тактовому импульсу с выхода генератора 19, поступающему через элемент И 21 на синхронизирующий вход регистра 5, код команды с выхода регистра 4 команд че"реэ коммутаторы адреса 12 и 13 занесен в регистр 5 адреса. Код командыопределяет адрес первой микрокомандысоответствующей микрокоманды, По второму тактовому импульсу с выхода генератора 19 сосчитанная иэ блока па3 13650 мяти 1 микрокоманда заносится в регистр 6.Если адрес очередной микрокоманды 91 55 1. Микропрограммный процессор,содержащий блок памяти микрокоманд,операционный блок, первый регистрадреса, первый коммутатор адреса,зависит от некоторого условия, то вполе 6,1 регистра 6 заносится кодпроверяемого условия, определяющегоход дальнейшего процесса выборки микрокоманд,При записи микрокоманды в регистр 106 осуществляется ее контроль блоком9 на четность (фиг. 2). При отсутствии ошибки в микрокоманде код адреса нанокоманды с поля 6.4 регистра 6через коммутатор 14 адреса по очередному тактовому импульсу заносится врегистр 7 адреса. Поля регистра 7адреса определяют коды адресов слогов нанокоманды, хранимых в группеблоков 2.1-2.п памяти, 20При обнаружении ошибки блоком 9контроля происходит блокировка операционного канала путем запрещенияпоступления тактовых импульсов насинхрониэирующие входы регистра 7 адреса и регистр 8 нанокоманд и черезкоммутатор 13 адреса разрешается обращение к блоку 1 памяти микрокомандпо инверсному адресу. Если в выбранной по инверсному адресу микрокоманде 30обнаружена ошибка, то блок 9 контроля (фиг, 2) при переходе триггера34 в нулевое состояние формируетпризнак отказа адресного канала. Этотпризнак с выхода блока 9 контроля через элемент ИЛИ 26 (фиг. 1) устанавливает триггер 18 отказа в единичноесостояние, На выходе одновибратора27 формируется импульс, который через элемент ИЛИ 25 устанавливает 40триггер 17 запрета в нулевое состояние и процессор прекращает на этомсвою работу.Если ошибки в адресном канале непроизошло, то после записи информации в регистр 7 адреса происходитвыборка слогов нанокоманды иэ блоков 2.1-2.п памяти. Выбранные слогинанокоманды по очередному тактовому импульсу заносятся в регистр 8 нанокоманд. Так как с выхода блока 3ассоциативной памяти на управляющийвход блока 11 коммутации поступаетнулевой код, то перестроения (реконструкции) слогов нанокоманды непроисходит,Если блок 1 О контроля при проверке информации на четкость ошибки необнаруживает, то с выхода регистра 8 нанокоманда через группу элементовИ 16 поступает на вход управленияоперационным блоком 28 (например,арифметико-логическим блоком),Если в нанокоманде блок 10 контроля (фиг. 3) обнаруживает ошибку,то блокируется выдача нанокомандына вход управления операционным блоком 28, блокируется адресный каналпутем запрета подачи тактовых импульсов на синхронизирукицие входы регистра 5 адреса и регистра 6 и черезкоммутатор 14 адреса разрешаетсяпрохождение нового адреса с выходаблока 3 ассоциативной памяти.Блок 3 ассоциативной памяти с учетом выявленной ошибки формирует двакода. Первый код определяет адресочередной (новой) нанокоманды, а второй код определяет вариант перестроения отдельных слогов блоком 11 коммутации при формировании управляющего слова (нанокоманды). При обнаружении блоком 10 контроля новой ошибкиблок 3 ассоциативной памяти формирует два очередных кода. При достижении числа ошибок блок 1 О контроляформирует признак отказа операционного канала. Этот признак с выхода блока 10 контроля через элемент ИЛИ 26устанавливает триггер 18 отказа вединичное состояние. На выходе одновибратора 27 формируется импульс,который через элемент ИЛИ 25 устанавливает триггер 17 запуска в нулевоесостояние. На этом процессор заканчивает свою работу.Если в очередном такте работы устройства в сформированной нанокомандеошибка не обнаружена, то процессорпродолжает функционирование аналогично описанному.При выдаче последней микрокомандымикропрограммы выдается признак окончания работы. Этот признак через элемент ИЛИ 25 устанавливает триггер 17запуска в нулевое состояние, а такжеразрешает запись очередной командыиз регистра 4 команд на регистр 5 адреса для выдачи очередной микропрограммы. Формула изобретения50 регистр микрокоманд, мультиплексор логических условий, триггер запуска, генератор тактовых импульсов, коммутатор, первый и второй элементы И, причем вход кода операции процессора соединен с первым информационным входом первого коммутатора адреса, вход пуска процессора соединен с входом установки в 1триггера за пуска, выход которого соединен с входом запуска генератора тактовых импульсов, первый выход которого соединен с прямым входом первого элемента И, выход которого соединен с вхо дом синхронизации первого регистра адреса, выход которого соединен с адресным входом блока памяти микро- команд, выход которого соединен с информационным входом регистра микроко манд, выход поля логических условий которого соединен с управляющим входом мультиплексора логических условий, вход данных процессора соединен с входом данных операционного блока, 25 выход данных которого соединен с выходом процессора, выход поля модифицируемых разрядов адреса регистра микрокоманд соединен с первым информационным входом мультиплексора ло гических условий, выход поля немодифицируемых разрядов адреса регистра микрокоманд соединен с вторым информационным входом первого коммутатора адреса, выход признаков результата35 операционного блока соединен с вторым информационным входом мулЬтиплексора логических условий, выход которого соединеН с вторым информационным входом первого коммутатора 40 адреса, второй выход генератора тактовых импульсов соединен с прямым входом второго элемента И, выход которого соединен с входом синхронизации регистра микрокоманд, о т л и - 45 ч а ю щ и й с я тем, что, с целью повышения достоверности функционирования, процессор содержит группыблоков памяти нанокоманд, блок ассоциативной памяти, первый и второй блоки контроля, второй и третий коммутаторы адреса, группу элементов И, второй регистр адреса, регистр нано- команд, триггер отказа, одновибратор, коммутатор, третий четвертый элементы И, первый и второй элементы ИЛИ, группу элементов НЕ, причем выход поля немодифицированных разрядов адреса регистра микрокоманд соединен с первой группой разрядов информационного входа первого блока контроля, выходы поля логических условий и поля адреса нанокоманды регистра микро- команд соединены соответственно с второй и третьей группами разрядов информационного входа первого блока контроля, выход поля признака четности регистра микрокоманд соединен с четвертой группой разрядов информационного входа первого блока контроля, выход разрешения работы которого соединен с управляющим входом второго коммутатора адреса и с инверсными входами третьего и четвертого элементов И, выход первого коммутатора адреса соединен с входом элементов НЕ группы и первым информационным входом второго коммутатора адреса, выходы элементов НЕ группы соединены с вторым информационным входом второго коммутатора адреса, выход которого соединен с информационным входом первого регистра адреса, выход поля адреса нанокоманды регистра микрокоманд соединен с первым информационным входом третьего коммутатора адреса и с первым адресным входом блока ассоциативной памяти, выход которого соединен с вторым информационным входом третьего коммутатора адреса, выход которого соединен с информационным входом второго регистра адреса, выходы полей адреса которого соединены с адресными входами соответствующих блоков памяти нанокоманд группы, выходы которых соединены соответственно с информационными входами коммутатора, выходы которого соединены с информационными входами регистра наноксманд, выход поля микроопераций которого соединен с первой группой разрядов информационного входа второго блока контроля, информационный выход которого соединен с вторым адресным входом блока ассоциативной памяти, выход которого соединен с управляющим входом коммутатора, выход признака ошибки первого блока контроля и выход признака ошибки второго блока контроля соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с входом установки в "1" триггера отказа, выход которого соединен с входом одновибратора, выход которого соецинен с первым входом второго элемента ИПЙ, выход которого соединен с13650 входом установки в 0 триггера запуска, третий выход генератора тактовых импульсов соединен с входом синхронизации операционного блока,5 четвертый выход генератора тактовых импульсов соединен с прямым входом третьего элемента И, выход которого соединен с входом синхронизации второго регистра адреса, пятый выход генератора тактовых импульсов соединен с прямым входом четвертого элемента И, выход которого соединен с входом синхронизации регистра нано- команд, выход признака четности кото рого соединен с второй группой разрядов информационного входа второго блока контроля, выход разрешения работы которого соединен с инверсными входами первого и второго элементов И, с управляющим входом третьего коммутатора адреса, с инверсными входами элементов И группы, выходы которых соединены с входом кода операции операционного блока, группа выходов 25 поля микроопераций регистра нанокоманд соединена соответственно с прямыми входами элементов И группы, выход первого элемента И группы соединен с вторым входом второго элемен- ЗО та ИЛИ и с управляющим входом первого коммутатора адреса.2, Процессор по п.1, о т л и - ч а ю щ и й с я тем, что первый блок контроля содержит сумматор по 918модулю два, первый, второй и третий одновибраторы, триггер, причем информационный вход первого блока контроля соединен с входами сумматора по модулю два, выход которого соединен с входом первого одновибратора, выход которого соединен со счетным входом триггера, прямой и инверсный выходы которого соединены соответственно с входами второго и третьего одновибраторов, выходы которых соединены соответственно с выходами разрешения работы и признака ошибки первого блока контроля.3. Процессор по п.1, о т л и - ч а ю щ и й с я тем, что второй блок контроля содержит сумматор по модулю два, одновибратор, счетчик, дешифратор, причем информационный вход второго блока контроля соединен с входами сумматоРа по модулю два, выход которого соединен с входом одновибратора, выход которого соединен со счетным входом счетчика, выход которого соединен с входом дешифратора, группа выходов которого соединена с информационным выходом второго блока контроля, выход дешифратора соединем с входом установки в "0" счетчика и с выходом признака ошибки второго блока контроля, выход сумматора по модулю два соединен с выходом разрешения работы второго блока контроля.1365091Составитель А. Михайлов Редактор М, Бланар Техред И.Верес Корректор Л. Пилипенко Заказ 6612/43 Тираж 704 Подписное ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб д, 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

4083713, 16.05.1986

ПРЕДПРИЯТИЕ ПЯ Г-4149

ДАНИЛИН НИКОЛАЙ СЕМЕНОВИЧ, МЕЛЬНИКОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, ПОНОМАРЕВ ВЛАДИМИР АЛЕКСЕЕВИЧ, ЩЕРБАК ВИКТОР ИОСИФОВИЧ, ПЕРЕСЫПКО МАРИНА ВИКТОРОВНА

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, процессор

Опубликовано: 07.01.1988

Код ссылки

<a href="https://patents.su/6-1365091-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Устройство для сопряжения микроэвм с общей магистралью

Следующий патент: Устройство для моделирования ошибок программного обеспечения

Случайный патент: Реактивная катушка