Устройство для формирования признаков распознаваемых образов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1328830

Авторы: Ковалерова, Ляшев, Петров

Текст

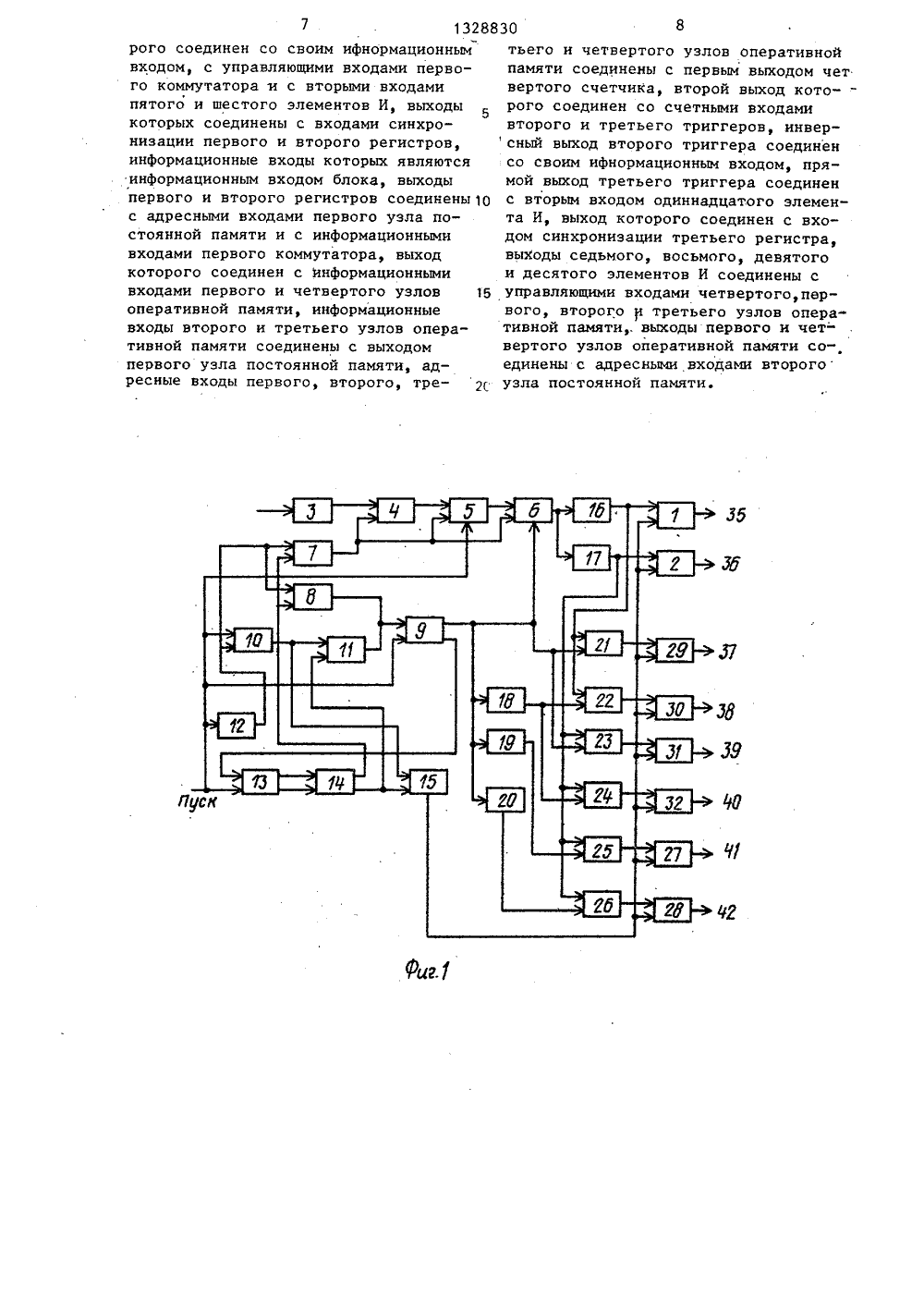

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9) (И)ц 4006 К 93 6 ОПИСАНИЕ ИЗОБРЕТЕНИК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ. ть распоГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ(54) УСТРОЙСТВО ДЛЯ ФОРМИР ЗНАКОВ РАСПОЗНАВАЕМЫХ ОВРА (57) Изобретение относится автоматики и вычислительно и может использоваться для ки изображений. Введение в во блока вычисления модуля позволяет повысить надежно знавания образов, 2 ил,ВАНИЯ ПРИ ОВ к областитехники обработ- устройст- разности30 35 Изобретение относится к автомати,ке и вычислительной технике и можетбыть использовано для обработки изображений,5Цель изобретения - повышение надежности устройства,На Фиг.1 представлена блок-схемаустройства; на Фиг,2 - схема блокавычисления модуля разности, 10Устройство содержит первый и второй интеграторы 1 и 2, Формирователь3 сигнала, аналого-циФровой преобразователь 4, блок 5 вычисления модуляразности, первый блок 6 памяти, первый и второй элементы И 7 и 8, третийсчетчик 9,первый счетчик 10, третийэлемент И 11, генератор 12 импульсов, второй счетчик 13, дешифратор14, четвертый элемент И 15, второй и 2 Отретин блоки 16 и 17 памяти первойгруппы, четвертый, пятый и шестойблоки 18-20 памяти второй группы,первый, второй и третий умножители21-ЙЗ первой группы, четвертый, пятый 25и шестой умножители 24-26 второй группы, первый и второй интеграторы 1и 2 первой группы, седьмой и восьмойинтеграторы 27 и 28 второй группы,третий - шестой интеграторы 29-32второй группы,Блок вычисления модуля разностисодержит пятый и шестой элементы И33 и 34, первый триггер 35, первыйи второй регистры 36 и 37, первыйкоммутатор 38, первый элемент 39 задержки, первый узел 40 постоянной памяти, четвертый счетчик 41, второйтриггер 42, третий триггер 43, седьмой-десятый элементы И 44-47, первый,второй, третий и четвертый узлы 48-51оперативной памяти, второй коммутатор 52, второй узел 53 постоянной памяти, второй элемент 54 задержки,сумматор 55, третий регистр 56, одиннадцатый элемент И 57,Устройство работает следующим образом,По сигналу "Пуск" устанавливаютсяв исходное состояние счетчики 9 и 13; 5 ОПри поступлении сигналаНачало строки" на первый вход счетчика 13 генератором импульсов вырабатывается последовательность импульсов, котораяпроходит через элемент И 7 на управляющие входы аналого-цифрового преобразователя (АЦП), блока 5 и блока6. В,блоке вычисления модуля разности последовательно для всех точекизображения осуществляется в заданных направлениях сканирования длякаждых двух соседних элементов разложения как по строкам, так и по столбцам, вычисление модуля разности поФормуле+)2,; -г;1,К - ( 2; - 2;+ где 2 - значение яркости элемента разложения изображения;- номер строки;- номер столбца,Это значение записывается в блоке 6 памяти по адресу, который формируется счетчиком 9 при поступлениина его вход через элемент И 8 импульсов. После перебора всех значений адреса с выхода счетчика 9 появляетсясигнал переноса, который поступаетна вход счетчика 13 режимов, изменяет его состояние на 01 и переводитработу устройства во второй цикл,При этом активируется единичный выходдешифратора 14, который разрешает прохождение импульсов со счетчика 10 через третий элемент И на третий счетчик и через четвертый элемент И напервые входы интеграторов для управления записью информации, Работа АЦПи блока вычисления модуля разностиблокируется, блок 6 памяти работаетв режиме считывания. С его выходавыдается последовательность значений координат, которые поступают навходы блоков 16 и 17 памяти, на выходах которых Формируются квадрат (блок16 памяти) и куб (блок 17 памятй)значений модуля разности сигналов,Значения кодов из счетчика 9 поступают на входы блоков 18-20 памяти,на выходах которых формируются квадрат (блок 18 памяти), куб (блок 19памяти) и четвертая степень (блок 20памяти) значений координаты каждого,элемента разложения, С выхода блока16 памяти коды поступают на первыевходы .умножителей 21 и 22 и на первый вход интегратора 1, С выхода блока 17 памяти коды поступают на первыевходы умножителей 23-26 и на первыйвход интегратора 2, Коды,с второговыхода счетчика 9 поступают на вторые входы умножителей 21 и 23, С выходов блока 18 памяти коды поступают на вторые входы умножителей 22 и24. С выхода блока 19 памяти коды поступают на второй вход умножителя 27, з 13288 После проведения всех тактов суммирования на выходах интеграторов формируются, значения признаков иэображения.Блок вычисления модуля разности работает следующим образом.При поступлении на третий вход блока сигнала "Пуск" устанавливаются в исходное состояние первый, второй и третий триггеры, первый и второй регистры, четвертый счетчик и третий регистр, При этом на инверсном выходе первого триггера устанавливается логическая единица, а на прямых выходах второго и третьего триггеров логиче ский ноль,. Содержимое первого и второго регистров, четвертого счетчика и третьего регистра становится равным нулю. Логическая единица с инверсного выхода первого, триггера посту пает на вход пятого элемента И, и на вход запрета шестого элемента И.Затем информация поступает на информационные входы первого и второго регистров, На второй вход блока поступает 25 сигнал стробирования. На выходе элемента И 33 формируется импульс, который, поступая на счетный вход первого регистра, записывает в него информацию. Импульс стробирования поступает также и на второй вход элемента И 34, но информация не заносится во второй регистр. Содержимое первого и второго регистров поступает на первый и четвертый входы первого35 коммутатора ввиду того, что на его второй вход и третий вход запрета поступает логический ноль, а на его выходной шине появится содержимое первого регистра. Кроме этого, содер жимое первого и второго регистров поступает на адресные входы первого узла постоянной памяти, в результате чего на выходной шине последнего формируется модуль разности двух чисел.Стробирующий сигнал, поступив на счетный вход счетчика 41, Формирует на его выходе первый адрес, который поступает на адресные Входы всех че 50 тырех узлов оперативной памяти, Выходная информация первого коммутатора поступает на информационные входы первого и четвертого узлов оперативной памяти, а информация модуля разности из первого узла постоянной памяти поступает на информационные входы второго и третьего узлов 7 оперативной памяти, Стробирующий сигнал 30с выхода первого элемента задержки поступает на первые входы элементов И 44-47, но только на выходе элементов И 44 и 46 формируется импульс, который, поступая на третьи входы вто. рого и четвертого узлов оперативной памяти, запишет информацию, По окончании записи второй и четвертый узлы оперативной памяти установятся в режим считывания по адресу записи. Считанная информация первого и четвертого узлов оперативной памяти поступает на адресные входы второго узла постоянной памяти, а считанная информация второго и третьего узлов оперативной памяти поступает на первый и четвертый входы второго коммутатора, так как на прямом выходе второго триггера присутствует логический ноль, который поступает на второй и третий входы запрета второго коммутатора, а на его выходе формируется выходной код третьего узла оперативной памяти. На выходе второго узла постоянной памяти формируется модуль разности двух точек по столбцам, а во второй узел памяти запишется модуль разности двух точек по строке (нечетной). С выхода второго узла постоянной памяти и второго коммутатора информация поступает на входы сумматора, а на его выходе формируется сумма модуля разности двух точек по строкам и модуля разности двух точек по столбцам. Сумма этих двух модулей разности поступает на вход регистра 56. На выходе второго элемента задержки формируется импульс, который поступает на первый вход элемента И 57, но ввиду того, что на пря - мом выходе третьего триггера присутствует логический ноль, который поступает на второй вход элемента И 57, то на счетном входе регистра 56 разрешения записи не появится. Так как до окончания первой, строки и начала второй третий триггер будет иметь ,на прямом выходе логический ноль, то информация, поступающая на информационный вход регистра 56, не фиксируется. Импульс с выхода второго элемента задержки поступит на счетный вход первого триггера и по заднему фронту переведет его в единичное состояние. В этом случае вторая (четная) информация записывается во второй регистрр.П ервый коммутатор пропустит на свой выход информацию второго регистра5 1328830Формула из о бр ет ения 1. Устройство для формирования признаков распознаваемых образов, содержащее формирователь сигналов, вход которого является информационным вхо" дом устройства, а выход соединен с информационным входом аналого-цифро- ВОГО преобразователя, четыре элеменюя И, три счетчика, дешифратор, гене ратор импульсов, шесть блоков памяти, шесть умножителей, и восемь интеграторов. управляющие входы которых соединены с выходом четвертого элемеРГта И, первые входы первого и вто Оогс умножителей и информационный лд первого интегратора соединены с :,х;ОДОМ 1 второго блока памяти, первые :Ходю ч ретьего, четвертого, пятого 1., шестого умнОжителей Й информацион ный вход второго интегратора соединены с выходом третьего блока памяти, 1 ходы Ргнтеграторов являются выхода и устройствя Рнформсционные ВхОды торого и третьего блоков памяти со единены с вьгходом первого блока памяти, вторые входы первого и третьего умножителей и адресные входы первого, четвертого, пятого и шестого блоков памяти соединены с первым выхо ДОМ ТРЕТЬЕГО СЧЕТЧИКЯ ВЫХОД ЧЕТВЕР- того бпока памяти соединен с вторыми зходами Второго и четвертого умножи:елей, выход пятого блока памяти соединен с Вторь входом пятого умножителя, выход шестого блока памяти со:.динен с в "орым входом шестого умно- :кителя,. Выходы первого, второго,третьего, четвертого, пятого и шестого умножителей соединены с информацион Впи входами третьего, четвертого, .ятого, шестого, седьмого и восьмого интеграторов, выход первого элемента И соединен с управляющими входами аналого-циФрового преобразователя и 45 первого блока памяти, первые входы в .ервого и второго элементов И и информационный вход первого счетчика соедине ь с выходом генератора им: ульсо:з,. управляюшие входы первого и 50 1:т 1 э 1 ОГ 1 ю счетчиков и Генеряторя имнуль-111.-В зляются входом Пуск устроист:ю. ВЮО,.1 ЬЕ В.,"ОДЫ ПЕРВОГО И ВТОРОГО 1 е;1 Н 1 юов И соединены с первым выхошифратора., первые входы тре ";его и четвертого элементов И соеди,;ь: с выходом первого счетчика, втоВходы третьего и четвертого зле;:,:.Нтов И соедцнены с вторым выходом дешифратора, информационный вход третьего счетчика соединен с выходамивторого и третьего элементов И, второй вход третьего счетчика соединенс входом Пуск" устройства, второйвыход третьего счетчика соединен суправляющим входом второго счетчикапервый выход которого соединен с первым входом дешифратора, второй входкоторого соединен с вторым выходомвторого счетчика, О т л и ч а ю щ ее с я тем, что, с целью повышениянадежности устройства, в него введенблок вычисления модуля разности, информационный вход которого соединенс выходом аналого-цифрового преобразователя вход "Стробирование" соединен с выходом первого элемента И, авыход соединен с ифнормационным входом первого блока памяти,2. Устройство пс п.1, о т л и ч аю щ е е с я тем, что блок вычислениямодуля разности содержит пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый элементы И, трирегистра, три триггера, два коммутатора, двя узла постоянной памяти,четыре узла оперативной памяти,дваэлемента задержки, сумматор и четвертый счетчик, входы установки первого, второго и третьего триггеров,первого, второго и третьего. регистров ичетвертого счетчика соединены с входом"Пуск" блока, выход третьего регист -ра является выходом блока,информаци-онный вход третьего регистра соединен с выходом сумматора, первый ивторой входы которого соединены соответственно с выходами второго узлапостоянной памяти и второго коммутатора, прямой выход второго триггерасоединен с первыми входами седьмого,восьмого, девятого и десятого элементов И и с входами управления второго коммутатора, первый и второй информационные входы которого соединеныс выходами второго и третьего узловоперативной памяти, первые входы пятого и шестого элементов И, вход первого элемента задержки и счетный входчетвертого счетчика являются входом"Стробирование" блока, выход первогоэлемента задержки соединен с вторымивходами седьмого, восьмого, девятогои десятого элементов И и с входомвторого элемента задержки, выход которого соединен с первым входом одиннядцатого элемента И и со счетнымвходом первого триггера, выход кото 7 . 13288 рого соединен со своим ифнормационным входом, с управляющими входами первого коммутатора и с вторыми входами пятОГО и шестого элементоВ И, Выходы 5 которых соединены с входами синхронизации первого и второго регистров, информационные входы которых являются информационным входом блока, выходы первого и второго регистров соединены 10 с адресными входами первого узла постоянной памяти и с информационными входами первого коммутатора, выход которого соединен с информационными входами первого и четвертого узлов 15 оперативной памяти, информационные входы второго и третьего узлов оперативной памяти соединены с выходом первого узла постоянной памяти, адресные входы первого, второго, тре 30тьего и четвертого узлов оперативнойпамяти соединены с первым выходом четвертого счетчика, второй выход кото рого соединен со счетными входамивторого и третьего триггеров, инвер сный выход второго триггера соединенсо своим ифнормационным входом, прямой выход третьего триггера соединенс вторым входом одиннадцатого элемента И, выход которого соединен с входом синхронизации третьего регистра,выходы седьмого, восьмого, девятогои десятого элементов И соединены суправляющими входами четвертого,первого, второго и третьего узлов оперативной памяти,. выходы первого и чет-вертого узлов оперативной памяти со-,единены с адресными входами второгоузла постоянной памяти,1328830 Составитель Л.Г Техред И.Попов то ктор В,Патруше Корректор Л.БескЗаказ 3489 д,4/5 Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная,4 ВНИИПИпо113035 Тираж 672 осударственного ком елам изобретений и о Москва, Ж, Раушс

СмотретьЗаявка

4066001, 27.03.1986

ПРЕДПРИЯТИЕ ПЯ В-2144

ПЕТРОВ ЛЕВ ВАСИЛЬЕВИЧ, ЛЯШЕВ ВИТАЛИЙ ПАВЛОВИЧ, КОВАЛЕРОВА ИРИНА НИКОЛАЕВНА

МПК / Метки

МПК: G06K 9/36

Метки: образов, признаков, распознаваемых, формирования

Опубликовано: 07.08.1987

Код ссылки

<a href="https://patents.su/6-1328830-ustrojjstvo-dlya-formirovaniya-priznakov-raspoznavaemykh-obrazov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования признаков распознаваемых образов</a>

Предыдущий патент: Устройство для распознавания радиосигналов

Следующий патент: Устройство для фильтрации бинарного изображения

Случайный патент: Бетонная смесь