Модуль процессора цифровой фильтрации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

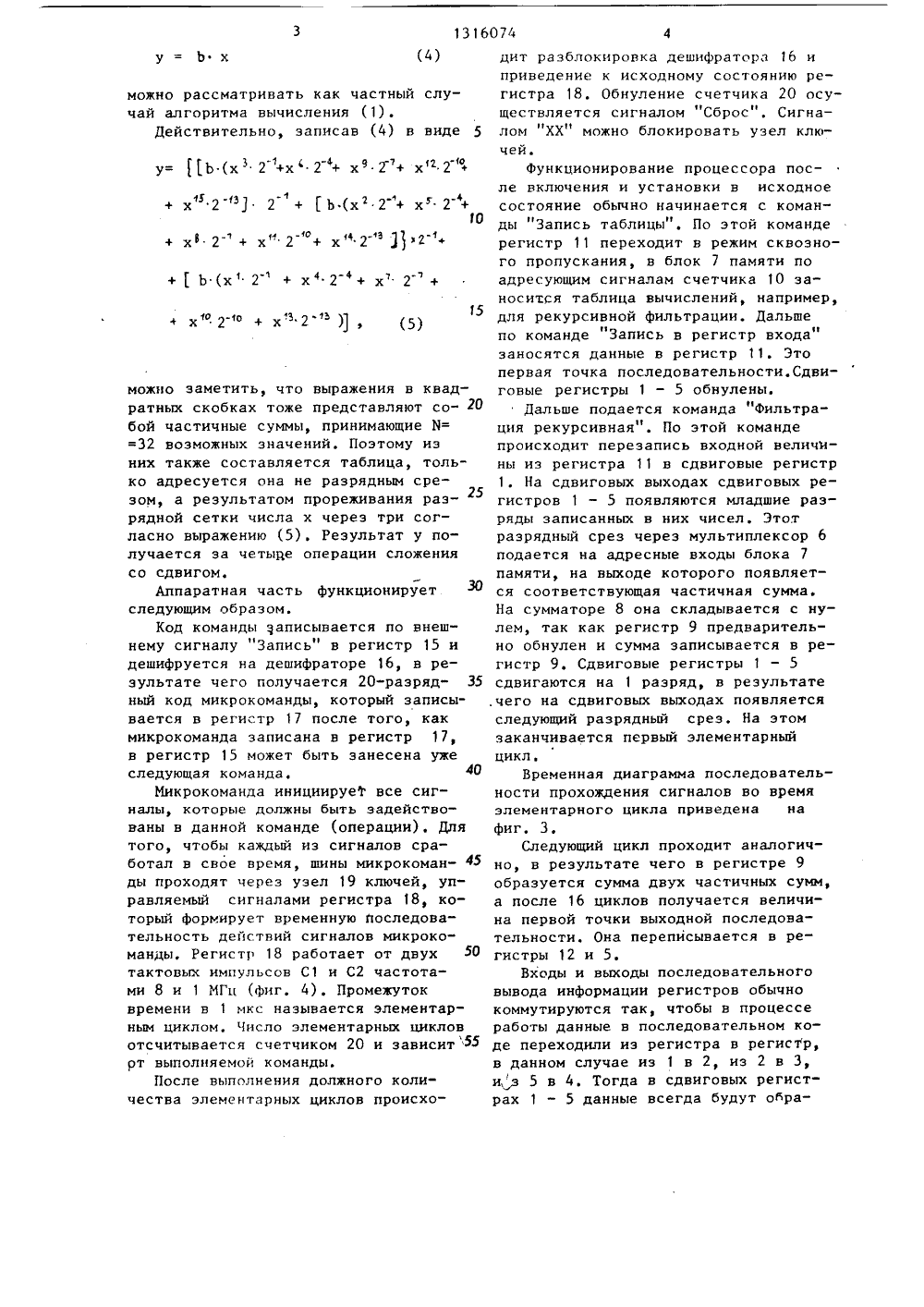

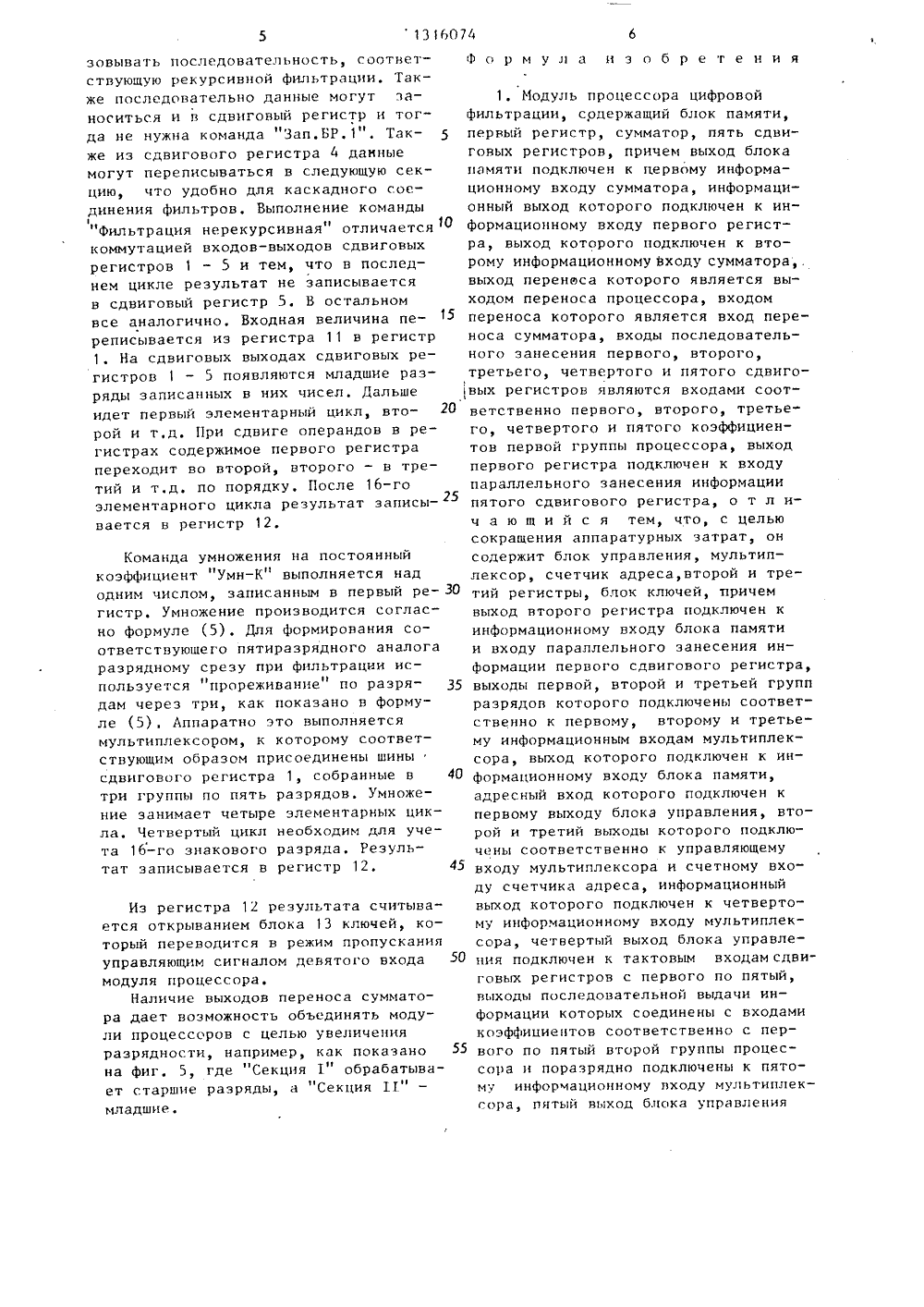

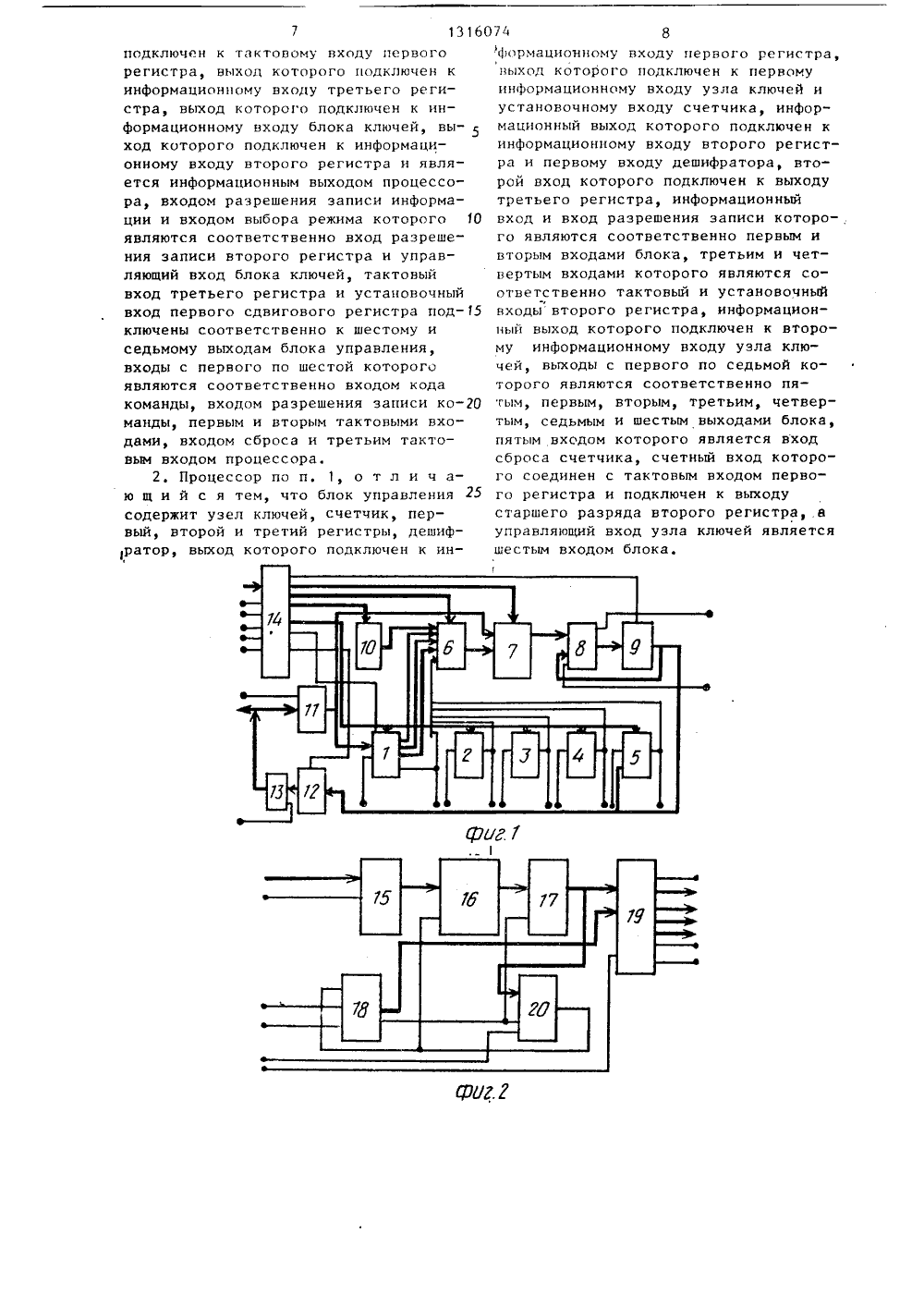

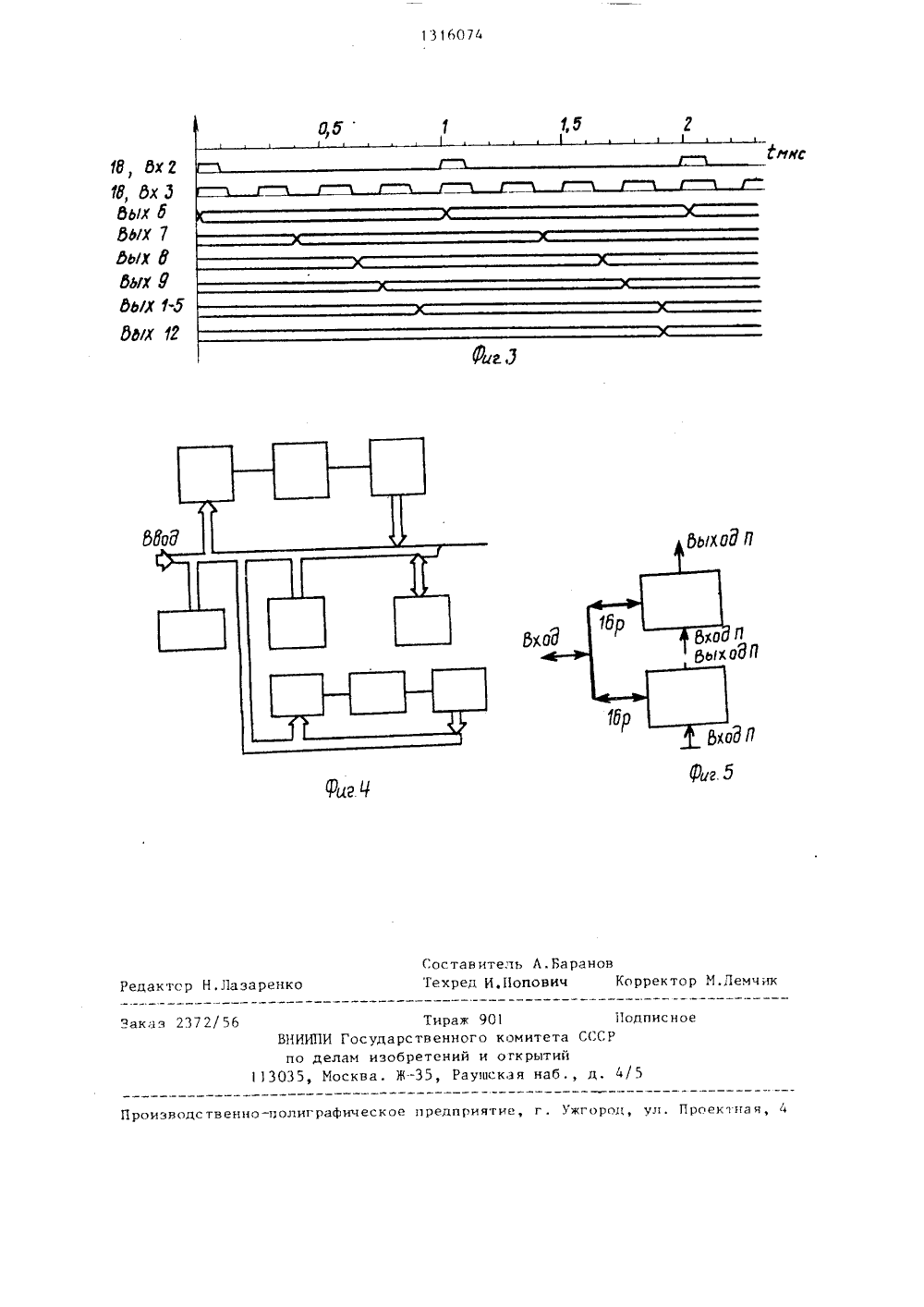

СОЮЗ СО 8 ЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 6074 03 Р 15 3 ННЫЙ КОМИТЕТ ССОБРЕТЕНИЙ И ОТНРЫ ГОСУДАРС ПО ДЕЛАМлФ. БРЕТ ий Теорияаботки с ыех в ОПИСАНИ К А ВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Рабинер Л., Гоулд Бприменение цифровой обрлов.-М,: Мир, 1978,Гольденберг Л.М, и др, Цифрустройства на интегральных схетехнике связи.-М.: Связь, 1979с. 161, рис. 5,31.(54) МОДУЛЬ ПРОЦЕССОРА ЦИФРОВОЙФИЛЬТРАЦИИ(57) Изобретение относится к областивычислительной техники и предназначено для использования в распределенных микропроцессорных системах цифровой обработки речевых и акустическихсигналов. Цель изобретения - сокращение аппаратурных затрат. Для достижения поставленной цели в состав модуля процессора входят сдвиговые ре-,гистры, мультиплексор, блок памяти,сумматор, регистр, счетчик адреса,регистры, блок ключей и блок управления, Наличие выходов переноса сумматора дает возможность объединять модули процессоров с целью увеличенияразрядности. 1 з.п. ф-лы, 5 ил.) 2 35 40 45 50 Изобретение относится к вычислительной технике и предназначено для использования в распределенных микропроцессорных системах цифровой обработки речевых и акустических сигналов.Цель изобретения - сокращение аппаратурных затрат.На фиг, 1 представлена схема модуля процессора цифровой фильтрации; на фиг, 2 - структура блока управления; на Фиг, Э - временные диаграммы, поясняющие функционйрование процессора; на фиг, 4 - структурное представление многопроцессорной системы; на фиг. 5 - структурная схема,поясняющая воэможности повышения разрядности обрабатываемых данных.Модуль процессора цифровой фильтрации содержит сдвиговый регистр 1,сдвиговые регистры 2 - 5, мультиплексор 6, блок 7 памяти, сумматор 8, регистр 9, счетчик 10 адреса, регистры 11 и 12, блок 13 ключей, блок 14 управления,Блок 14 управления (фиг. 2) содержит регистр (команд) 15, дешифратор (микрокоманд 16), регистр (микрокоманд) 17, регистр 18, узел 19 ключей и счетчик 20 циклов.Иоудль процессора цифровой фильтрации выполняет линейные операции табличными методами вычислений. Особенность функционирования предлагаемого устройства в многопроцессорной системе (фиг, 4) характеризуется тем, что перед началом работыцифрового фильтра, образованного изпоследовательно соединенных секций,производится вычисление таблиц частичных произведений одним из специализированных процессоров системы иих загрузка в накопители модуля процессоров цифровой фильтрации, Содержимое накопителей соответственно меняется при изменении коэффициентовфильтра. Управление модулем процессора микропрограммное, Процессор оперирует 16-разрядными числами с фиксированной запятой, Ввод и вывод данных производится по одной двунаправленной шине.Устройство работает следующим образом. Проводя алгоритм вычислений, рассмотрим подробно вычисление процессором Фильтра набора операций, Операциирекурсивной и нерекурсивной фильтрации сводятся к вычислению линейной комбинации нида 5 у =, а,х т 1+Ь У +Ь бНиУпН ф где а - постоянные коэффициенты; х, - данные; у - результат вычислений, Все числа представлены в дополнительном двоичном коде с фиксированной запятой, Выражение (1) можно привести к виду5у=(а,х,)2 + . а;х)2 +1 с 1:1 Суммы, стоящие в круглых скобках, и представляющие собой выражения видаГу = Е х, (3) назовем частичными суммами, Величины 1х. являются 3-ми двоичными разрядами переменной х Очевидно,что любая1частичная сумма у 1 является при известных (а 1,а ,аз,а ,а) некоторой комбинацией иэ этих коэфФициентов; число комбинаций равно И = 2 =32, т.е. любое у может принять одно иэ 32 возможных значений. Вычисляя предварительно эти значения, получаем таблицу, из которой можно выбратьсоответствующее значение у". Совокупностьх,х ,х ,х ,х ) в выражении(3) назовем разрядным срезом, Каждомуразрядному срезу соответствует у 1 -частичная сумма, которая выбираетсяиз таблицы. Складывая частичные суммы, начиная с младших разрядов сосдвигом вправо, соответственно выражению (2) получаем значение у в результате 16 операций сложения,Таблица записывается в накопительемкостью 16 разрядов32 слова такимобразом, что каждая, частичная сумманаходится в ячейке с адресом, равнымсоответствующему разрядному срезу,Адресуя оперативный накопитель разрядным срезом, получаем на его выходе нужную частичную сумму.Вычисление произведения на постоянный коэффициент вида+ о 2-то + ха 2 " ), (5) можно рассматривать как частный случай алгоритма вычисления (1),Действительно, записав (4) в виде 5 у Ь.(х .2 +х .2 + х 9,2.+ хп 22 ++Ь (х 2" + х 4,2 ф+ х 2+ можно заметить, что выражения в квадратных скобках тоже представляют собой частичные суммы, принимающие М==32 возможных значений. Поэтому изних также составляется таблица, только адресуется она не разрядным срезом, а результатом прореживания разрядной сетки числа х через три согласно выражению (5), Результат у получается за четыпе операции сложениясо сдвигом.Аппаратная часть функционируетследующим образом.Код команды записывается по внешнему сигналу "Запись" в регистр 15 идешифруется на дешифраторе 16, в результате чего получается 20-разрядный код микрокоманды, который записывается в регистр 17 после того, какмикрокоманда записана в регистр 17,в регистр 15 может быть занесена ужеследующая команда,40Микрокоманда инициируеТ все сигналы, которые должны быть задействованы в данной команде (операции). Длятого, чтобы каждый из сигналов сработал в свое время, шины микрокоманды проходят через узел 19 ключей, управляемый сигналами регистра 18, который формирует временную Последовательность действий сигналов микрокоманды. Регистр 18 работает от двух 50тактовых импульсов С и С 2 частотами 8 и 1 МГц (фиг. 4). Промежутоквремени в 1 мкс называется элементарным циклом, Число элементарных цикловотсчитывается счетчиком 20 и зависит 55 рт выполняемой команды. После выполнения должного количества элементарных циклов происходит разблокировка дешифратора 16 иприведение к исходному состоянию регистра 18. Обнуление счетчика 20 осуществляется сигналом "Сброс", Сигналом "ХХ" можно блокировать узел ключей.Функционирование процессора после включения и установки в исходноесостояние обычно начинается с команды "Запись таблицы", По этой командерегистр 11 переходит в режим сквозного пропускания, в блок 7 памяти поадресующим сигналам счетчика 10 заносится таблица вычислений, например,для рекурсивной фильтрации, Дальшепо команде Запись в регистр входа"заносятся данные в регистр 11. Этопервая точка последовательности.Сдвиговые регистры 1 - 5 обнулены,Дальше подается команда "Фильтрация рекурсивная". По этой командепроисходит перезапись входной величИны из регистра 11 в сдвиговые регистр1. На сдвиговых выходах сдвиговых регистров 1 - 5 появляются младшие разряды записанных в них чисел. Этотразрядный срез через мультиплексор 6подается на адресные входы блока 7памяти, на выходе которого появляется соответствующая частичная сумма.На сумматоре 8 она складывается с нулем, так как регистр 9 предварительно обнулен и сумма записывается в регистр 9. Сдвиговые регистры 1 - 5сдвигаются на 1 разряд, в результате,чего на сдвиговых выходах появляетсяследующий разрядный срез. На этомзаканчивается первый элементарныйцикл,Временная диаграмма последовательности прохождения сигналов во времяэлементарного цикла приведена нафиг. 3.Следующий цикл проходит аналогично, в результате чего в регистре 9образуется сумма двух частичных сумм,а после 16 циклов получается величина первой точки выходной последовательности, Она переписывается в регистры 12 и 5.Входы и выходы последовательноговывода информации регистров обычнокоммутируются так, чтобы в процессеработы данные в последовательном коде переходили из регистра в регистр,в данном случае из 1 в 2, из 2 в 3,и,з 5 в 4. Тогда в сдвиговых регистрах 1 - 5 данные всегда будут обра 131 Г)074зовывать последовательность, соответствующую рекурсивной фильтрации, Также последовательно данные могут заноситься и в сдвиговый регистр и тогда не нужна команда "Зап,БР,1", Также из сдвигового регистра 4 данные могут переписываться в следующую секцию, что удобно для каскадного соединения фильтров, Выполнение команды "Фильтрация нерекурсивная" отличается коммутацией входов-выходов сдвиговых регистров 1 - 5 и тем, что в последнем цикле результат не записывается в сдвиговый регистр 5. В остальном все аналогично. Входная величина переписывается из регистра 11 в регистр 1. На сдвиговых выходах сдвиговых регистров 1 - 5 появляются младшие разряды записанных в них чисел. Дальше идет первый элементарный цикл, второй и т.д. При сдвиге операндов в регистрах содержимое первого регистра переходит во второй, второго - в третий и т.д. по порядку. После 16-го элементарного цикла результат записывается в регистр 12.Команда умножения на постоянныйкоэффициент нУмн-К" выполняется над одним числом, записанным в первый регистр, Умножение производится согласно формуле (5), Для формирования соответствующего пятиразрядного аналога разрядному срезу при фильтрации используется прореживание по разрядам через три, как показано в формуле (5), Лппаратно это выполняется мультиплексором, к которому соответствующим образом присоединены шины сдвигового регистра 1, собранные в три группы по пять разрядов. Умножение занимает четыре элементарных цикла, Четвертый цикл необходим для учета 1 б-го знакового разряда. Результат записывается в регистр 12.Из регистра 12 результата считывается открыванием блока 13 ключей, который переводится в режим пропусканияуправляющим сигналом девятого входамодуля процессораНаличие выходов переноса сумматора дает возможность объединять модули процессоров с целью увеличенияразрядности, например, как показанона фиг, 5, где "Секция 1" обрабатывает старшие разряды, а "Секция 11" младшие, 1. Модуль процессора цифровойфильтрации, содержащий блок памяти, 5 первый регистр, сумматор, пять сдвиговых регистров, причем выход блокапамяти подключен к первому информационному входу сумматора, информационный выход которого подключен к ин формационному входу первого регистра, выход которого подключен к второму информационному входу сумматора,.выход переноса которого является выходом переноса процессора, входом 15 переноса которого является вход переноса сумматора, входы последовательного занесения первого, второго,третьего, четвертого и пятого сдвиговых регистров являются входами соответственно первого, второго, третьего, четвертого и пятого коэффициентов первой группы процессора, выходпервого регистра подключен к входупараллельного занесения информациипятого сдвигового регистра, о т л ич а ю щ и й с я тем, что с цельюсокращения аппаратурных затрат, онсодержит блок управления, мультиплексор, счетчик адреса, второй и третий регистры, блок ключей, причемвыход второго регистра подключен кинформационному входу блока памятии входу параллельного занесения информации первого сдвигового регистра,выходы первой, второй и третьей группразрядов которого подключены соответственно к первому, второму и третьему информационным входам мультиплексора, выход которого подключен к информационному входу блока памяти,адресный вход которого подключен кпервому выходу блока управления, второй и третий выходы которого подключены соответственно к управляющемувходу мультиплексора и счетному входу счетчика адреса, информационныйвыход которого подключен к четвертому информационному входу мультиплексора, четвертый выход блока управления подключен к тактовым входам сдвиговых регистров с первого по пятый,выходы последовательной выдачи информации которых соединены с входамикоэффициентов соответственно с первого по пятый второй группы процессора и поразрядно подключены к пятому информационному входу мультиплексора, пятый выход блока управления 20 25 30 35 40 45 50 55 Формула изобретения1316подключен к тактовому входу первого регистра, выход которого подключен к информационному входу третьего регистра, выход которого подключен к информационному входу блока ключей, вы ход которого подключен к информационному входу второго регистра и является информационным выходом процессора, входом разрешения записи информации и входом выбора режима которого 1 О являются соответственно вход разрешения записи второго регистра и управляющий вход блока ключей, тактовый вход третьего регистра и установочный вход первого сдвигового регистра под ключены соответственно к шестому и седьмому выходам блока управления, входы с первого по шестой которого являются соответственно входом кода команды, входом разрешения записи команды, первым и вторым тактовыми входами, входом сброса и третьим тактовым входом процессора.2. Процессор по п. 1, о т л и ч аю щ и й с я тем, что блок управления 25 содержит узел ключей, счетчик, первый, второй и третий регистры, дешиф 1 ратор, выход которого подключен к инои Яформационному входу первого регистра,выход которого подключен к первомуинформационному входу узла ключей иустановочному входу счетчика, информационный выход которого подключен к информационному входу второго регистра и первому входу дешифратора, второй вход которого подключен к выходу третьего регистра, информационный вход и вход разрешения записи которого являются соответственно первым и вторым входами блока, третьим и четвертым входами которого являются соответственно тактовый и установочный входы второго регистра, информационный выход которого подключен к второму информационному входу узла ключей, выходы с первого по седьмой которого являются соответственно пягым, первым, вторым, третьим, четвертым, седьмым и шестым выходами блока, пятым входом которого является вход сброса счетчика, счетный вход которого соединен с тактовым входом первого регистра и подключен к выходу старшего разряда второго регистра,.а управляющий вход узла ключей является шестым входом блока.1 юкс 1 В, бх 2 в, ,ь.з 6 ЫХ б дых 7 Юь/х У ЮЫХ У дык 1-5 ддх 1 Я Диг 5 оставитель Л.Бараноехред И,Попович Редактор Н,Лазаренко орректор М.Демчик Заказ 2372 Тираж 90 ИПИ Государственного делам изобретений и Москва. Ж, Раушсодписное ВНИ комитета гк рытий зя наб. д, 4/5 1 303 л Проектна роизводственно - полиграфическое предприятие,

СмотретьЗаявка

4026000, 24.02.1986

МОСКОВСКИЙ ИНЖЕНЕРНО-ФИЗИЧЕСКИЙ ИНСТИТУТ

ВОРОБЬЕВ КОНСТАНТИН ВЛАДИМИРОВИЧ, МЫНКИН СЕРГЕЙ СЕМЕНОВИЧ, ФИРСТОВ ЮРИЙ ПЕТРОВИЧ

МПК / Метки

МПК: G06F 17/17, H03H 17/04

Метки: модуль, процессора, фильтрации, цифровой

Опубликовано: 07.06.1987

Код ссылки

<a href="https://patents.su/6-1316074-modul-processora-cifrovojj-filtracii.html" target="_blank" rel="follow" title="База патентов СССР">Модуль процессора цифровой фильтрации</a>

Предыдущий патент: Операционный усилитель на мдп-транзисторах

Следующий патент: Управляемый генератор

Случайный патент: Пробоотборник