Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1305781

Автор: Бородин

Текст

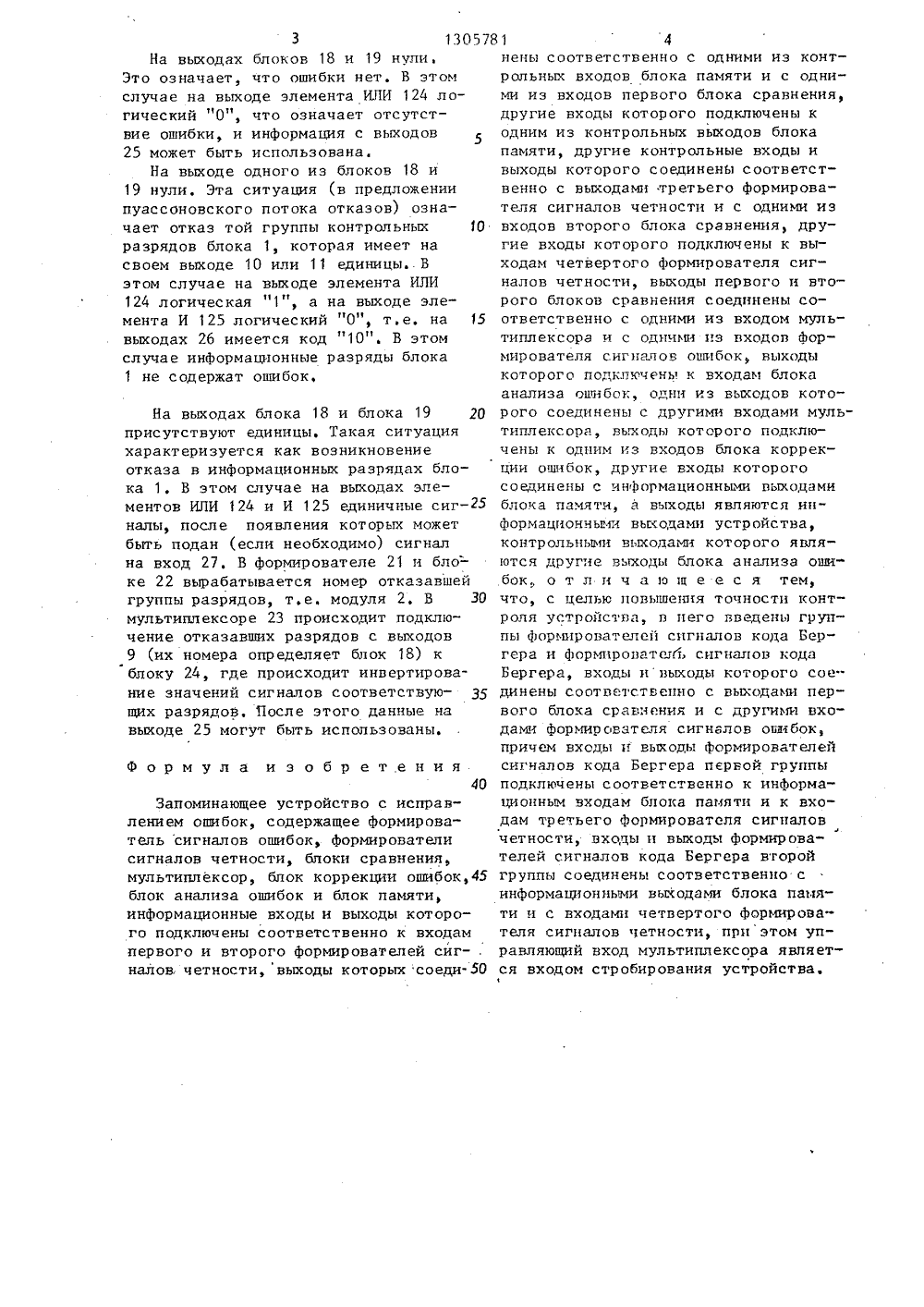

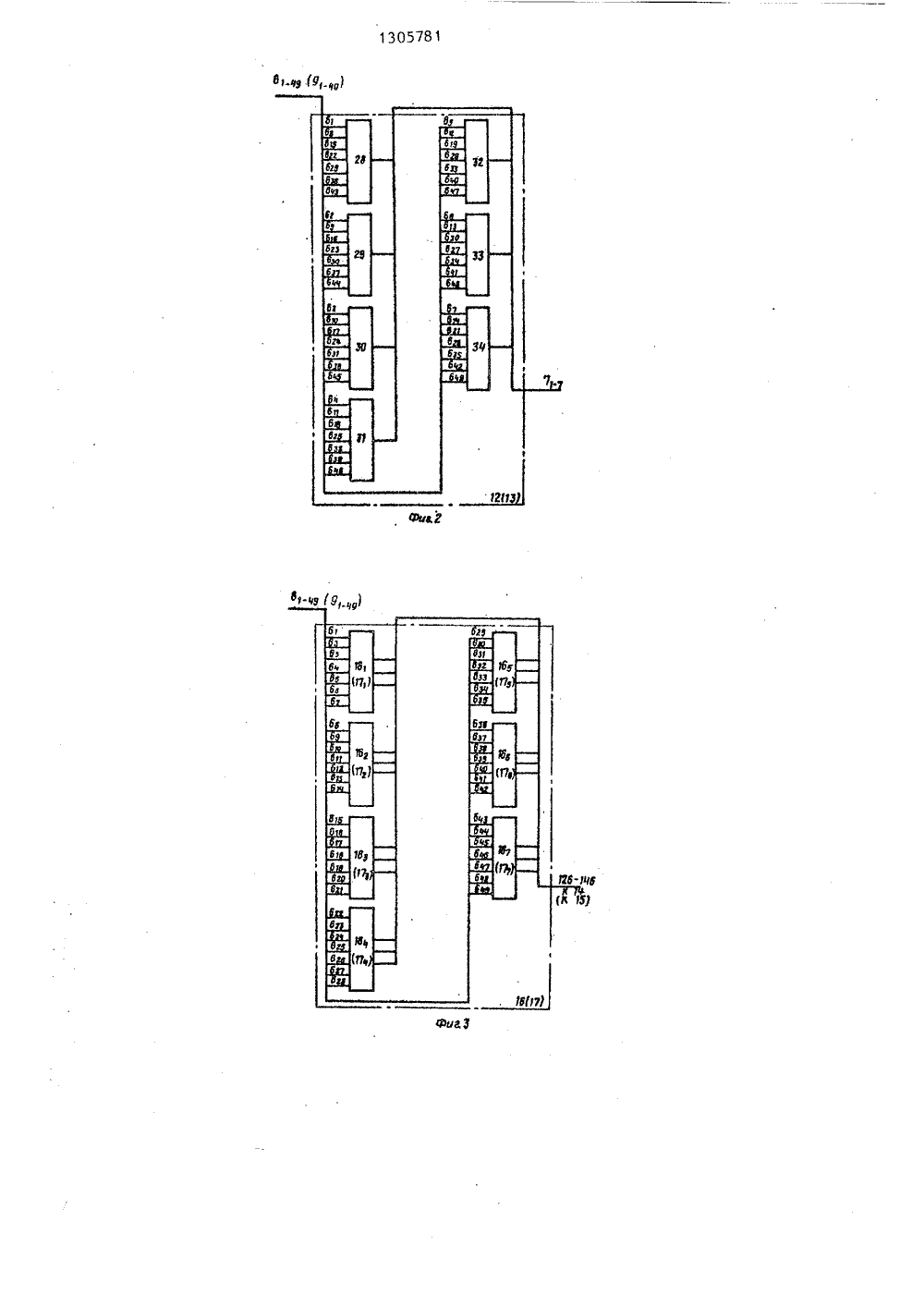

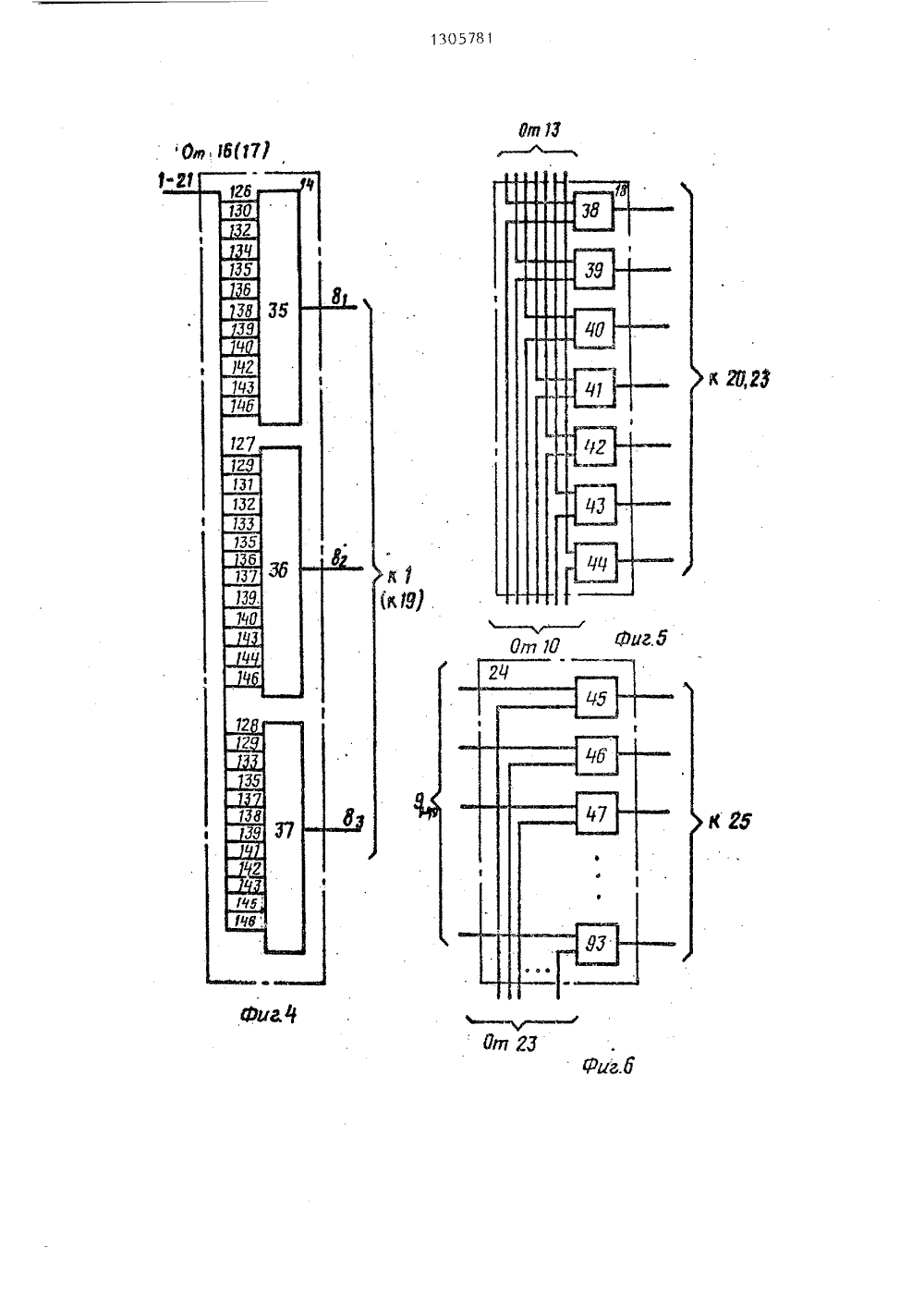

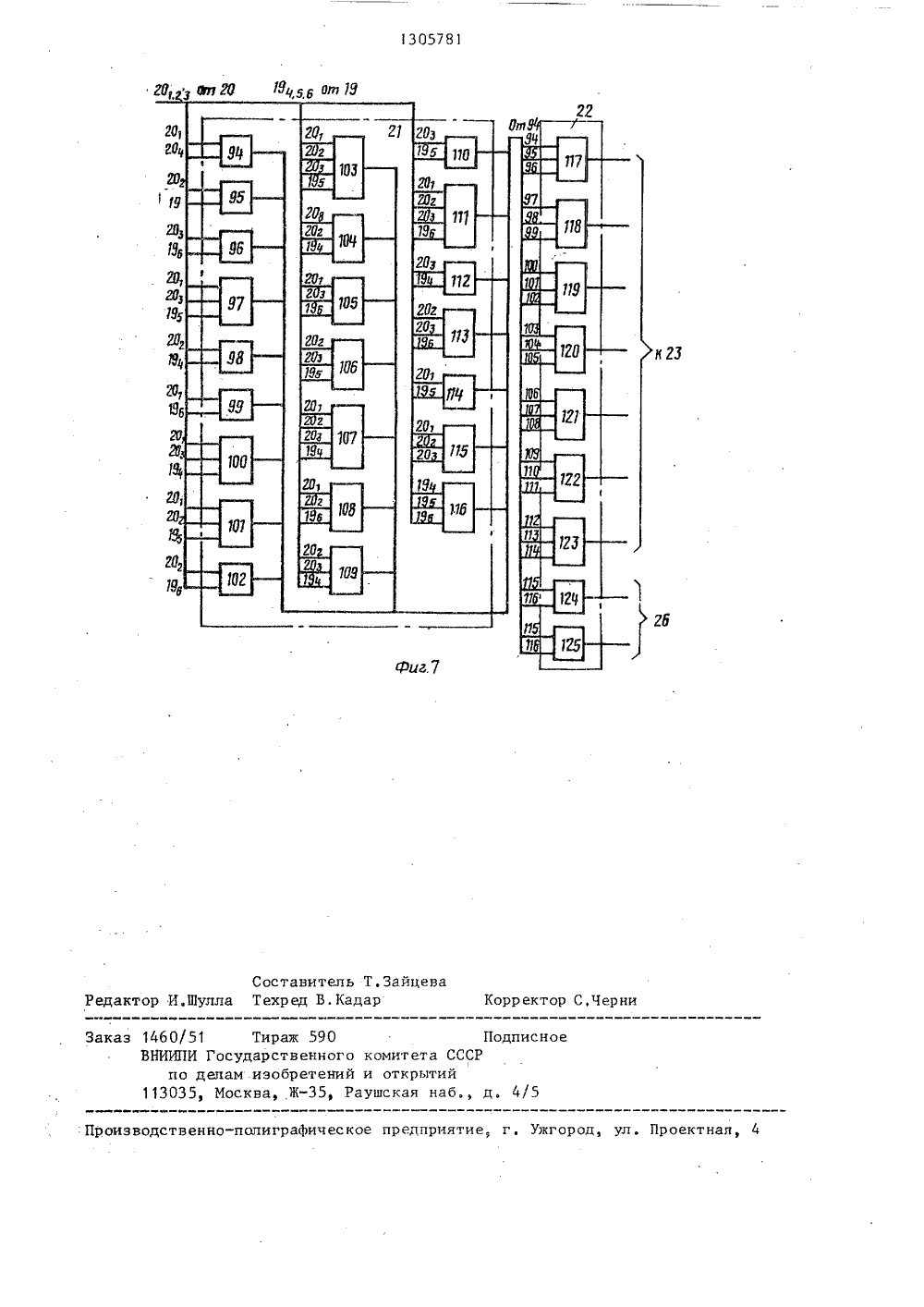

.8)видетельство СС11 С 29/00, 198еатсЬ апй Йече 1р. 402-408. СРО.оршеп 970 зГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ Н АВТОРСКОМУ СВИ(57) Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, выполненнымиз интегральных микросхем памяти,Целью изобретения является повышениеточности контроля устройства, Устройство содержит блок 1 памяти, выполненный из конструктивных модулей2 памяти, например из интегральных микросхем памяти, четыре формирователя 12-15 сигналов четности, две группы формирователей 16 и 17 сигналовкода Бергера, два блока 18 и 19 сравнения, формирователь 20 сигналов када Берг ера, формир оват ель 21 сиг налов ошибок, блок 22 анализа ошибок,мультиплексор 23 и блок 24 коррекцииошибок, В устройстве выполняется самоконтроль путем формирования контрольного кода при записи и считывании информации с помощью формирователей сигналов четности и формирователей сигналов кода Бергера и сравнение этих контрольных кодов в блокахсравнения при считывании информации.Формирователь сигналов ошибок и блоканализа ошибок служат для определения номера отказывающего модуля памяти, В блоке коррекции ошибок выполняется исправление групповых однонаправленных ошибок длиной до семи рарядов в модуле памяти. 7 ил.1 130578Изобретение относится к вьиислительной технике, в частности к запоминающим устройствам, выполненным из интегральных микросхем памяти.Целью изобретения является повышение точности контроля устройства.На фиг. 1 представлена структурная схема предлагаемого устройствами на фиг. 2 и 3 - схемы соединения информационных входов (или выходов) блока 10 памяти соответственно с первым (или вторым) Формирователем сигналов четности и с формирователями сигналов кода Бергера первой (второй) группы, на Фиг. 4 - схема соединения Формирова телей сигналов кода Бергера с третьим и четвертым формирователями сигналов четности; на фиг. 5 - схема соединения блоков сравнения с формирователями сигналов четности, на фиг. б - 20 структурная схема блока коррекции ошибок, на Фиг. 7 - структурная схема формирователя сигналов ошибки и ,блока анализа ошибок.25Устройство (Фиг. 1) содержит блок 1 памяти, выполненный из конструктив-. ных модулей 2, например интегральных микросхем памяти, управляющими 3 и 4, адресными 5, информационными 6, и 30 контрольными 7 и 8 входами, информационными 9, и контрольными 10 и 11 выходами, формирователи 12-15 сигналов четности с первого по четвертый, первая 16 и вторая 17 группы формирователей сигналов кода Бергера, первый 18 и второй 19 блоки сравнения, формирователь 20 сигналов кода Бергера, Формирователь 21 сигналов . ошибок, блок 22 анализа ошибок, муль типлексор 23 и блок 24 коррекции ошибок, а также информационные 25 и контрольные 26 выходы и вход 27 стробиро" вания устройства. Первый 12 и второй 13 формирователи сигналов четности содержат каждый (фиг. 2) сумматоры 28- 34 по модулю два. На фиг. 3 обозначены формирователи 16-16 (17, -17 ) сигналов кода Бергера первой (второй) группы. 50Третий 14 и четвертый 15 формирователи сигналов четности содержат каждый (фиг, 4) сумматоры 35-37 по модулю два, Блок 18 сравнения содержит (фиг, 5) элементы 38-44 неравнознач ности. Блок 24 коррекции ошибок содержит (Фиг, 6) сумматоры 45-93 по модулю два. Формирователь 21 сигналов ошибки содержит (фиг. 7) элемен 1 2ты И 94-114 и элементы ИЛИ 115 и 116, блок 22 анализа. ошибок (фиг. 7) элементы ИЛИ 117-124 и элемент И 125. Формирователи 16(17) сигналов кода Бергера имеют выходы 126-146 с первого по двадцать первый (фиг. 3 и 4)Предлагаемое устройствоработает следующим образом.Устройство обеспечивает с помощью десяти контрольных разрядов исправление групповых однонаправленных ошибок длиной до семи разрядов в слове длиной сорок девять разрядов или исправление ошибок длиной до шести разрядов в слове длиной девяносто разрядов.В режиме записи информации на вход 3 подают сигнал управления записью, например "Лог0", На входы 5 подают адрес ячейки, в которую необходимо раписать число, поступающее по входу б . На вход 4 подают сигнал обращения, например Лог, 0", длительность кото рого должна быть больше задержки в блоке 1 и других блоках устройства.В формирователе 12 Формируются зна. чения первой группы контрольных сигналов, они записываются по входам 7, а в формирователях 16 и 14 формируется вторая группа контрольных сигна- . лов, которые записываются по входам 8.Кодирование по коду Бергера в простейшем случае заключается в том, что в качестве контрольного кода (в трех разрядах) используется число, в двоичной Форме указывающее количество единиц в разрядах одного модуля 2, состоящего, например, из семи информационных разрядов.В режиме считывания на вход 3 подают сигнал считывания, например "Лог, 1", На входы 5 подают адрес ячейки, информация которой необходима, на вход 4 - сигнал обращения, например "Лог, О", При необходимости после получения сигналов исправляемой ошибки на выходах 26 может быть введено стробирование по входу 27.Как и при кодировании, в формирователях 13, 15 и 17 происходит выработка значений контрольных сигналов двух групп, которые в блоках 18 и 19 сравниваются поразрядно со значениями контрольных сигналов, считанных из блока 1 по выходам 10 и 11.При этом возможны следующие ситуа- цииь3 13057На выходах блоков 18 и 19 нули, Это означает, что ошибки нет. В этом случае на выходе элемента ИЛИ 124 логический 0, что означает отсутствие ошибки, и информация с выходов 25 может быть использована.На выходе одного из блоков 18 и 19 нули. Эта ситуация (в предложении пуассоновского потока отказов) означает отказ той группы контрольных 10 разрядов блока 1, которая имеет на своем выходе 10 или 11 единицы В этом случае на выходе элемента ИЛИ 124 логическая "1", а на выходе элемента И 125 логический "0", т, е. на 15 выходах 26 имеется код "10". В этом случае информационные разряды блока 1 не содержат ошибок.На выходах блока 18 и блока 19 20 присутствуют единицы, Такая ситуация характеризуется как возникновение отказа в информационных разрядах блока 1, В этом случае на выходах элементов ИЛИ 124 и И 125 единичные сигналы, после появления которых может быть подан (если необходимо) сигнал на вход 27, В формирователе 21 н блоке 22 вырабатывается номер отказавшей группы разрядов, т.е, модуля 2. В 30 мультиплексоре 23 происходит подключение отказавших разрядов с выходов 9 (их номера определяет блок 18) к блоку 24, где происходит инвертирование значений сигналов соответствующих разрядов, После этого данные на выходе 25 могут быть использованы.Формула изобретения40Запоминающее устройство с исправлением ошибок, содержащее формирователь сигналов ошибок, формирователи сигналов четности, блоки сравнения, мультиплексор, блок коррекции ошибок,45 блок анализа ошибок и блок памяти, информационные входы и выходы которого подключены соответственно к входам первого и второго формирователей сиг- . налов четности,выходы которых соединены с оотв етств енно с одними из контрольных входов блока памяти и с одними из входов первого блока сравнения,другие входы которого подключены кодним из контрольных выходов блокапамяти, другие контрольные входы ивыходы которого соединены соответственно с выходами третьего формирователя сигналов четности и с одними извходов второго блока сравнения, другие входы которого подключены к выходам четвертого Формирователя сигналов четности, выходы первого и второго блоков сравнения соединены соответственно с одними из входом мультиплексора и с одними из входов формирователя сигналов ошибок, выходыкоторого подключены к входам блокаанализа ошибок, одни из выходов которого соединены с другими входами мультиплексора, выходы которого подключены к одним из входов блока коррекции ошибок, другие входы которогосоединены с лнформационньии выходамиблока памяти, а выходь 1 являются информационныи вькодами устройства,контрольными выходами которого являются другие выходы блока анализа ошибок о т л и ч а ю щ е е с я тем,что, с целью повышения точности контроля устройства, в пего введены группы формирователей сигналов кода Бергера и Формирователь сигналов кодаБергера, входы и выходы которого соединены соответственно с выходами первого блока сравнения и с другими входами формирователя сигналов ошибок,причем входы и выходы Формирователейсигналов кода Бергера первой группыподключены соответственно к информационным входам блока памяти и к входам третьего формирователя сигналовчетности, входы и выходы формирователей сигналов кода Бергера второйгруппы соединены соответственно синформационными вькодами блока памяти и с входами четвертого формирователя сигналов четности, при этом управляющий вход мультиплексора является входом стробирования устройства.11305781 рректор С,Черн Подписноеа СССР ий янаб д,Производственн Составитель Т. Зайцеваактор И.Булла Техред В. Кадар каз 1460/51 Тираж 590 ВНИИПИ Государственного коми по делам изобретений и от 113035, МоскваЖ, Раушск

СмотретьЗаявка

3997906, 30.12.1985

МОСКОВСКИЙ ЭНЕРГЕТИЧЕСКИЙ ИНСТИТУТ

БОРОДИН ГЕННАДИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 23.04.1987

Код ссылки

<a href="https://patents.su/6-1305781-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Аналоговое запоминающее устройство

Следующий патент: Гибкий электрический кабель

Случайный патент: Устройство для отделения листовых заготовок от стопы и подачи их в пресс