Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

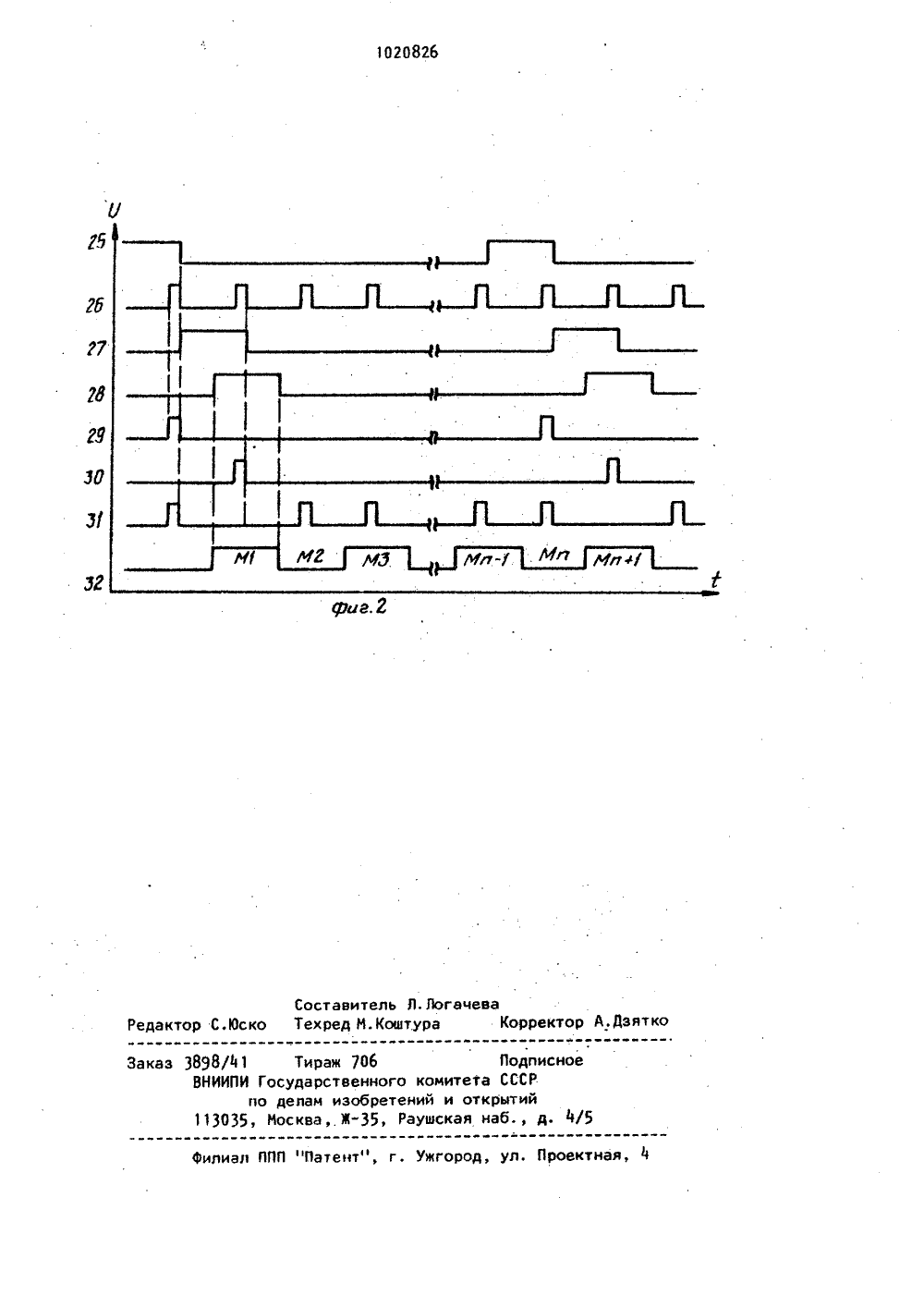

%З 4Г ЕНИЯ вх вх ко со фе р- Ф ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ ОЛИСАНИЕ ИЭОБР К АВТОРСКОМУ СВИДЕТЕЛЬСТ(56) 1. Нвторское свидетельство СССР Нф 763898, кл. О 06 Р 9/22, 1980.2, Авторское свидетельство СССР й 703811, кл. 6 06 Г 9/22, 1979 .(прототип).(5 Ц)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВО , УПРАВЛЕНИЯ, содержащее первый и второй блоки памяти, регистр адреса, бу-. ферный регистр, регистр логических условий, счетчик адреса, счетчик микрокоманд, первую и вторую группы элементов И, группу элементов ИЛИ, первый, второй, третий и четвертый элементы И, элемент НЕ, элемент задержки и генератор тактовых импульсов, причем выход числа микрокоманд первого блока памяти соединен с информационным входом счетчика микрокоманд, выход которого через первый элемент И соединен с первым входом второго элемента И, второй вход которого соединен с первыми входами третьего и четвертого элементов И и с выходом генератора тактовых импульсов, адресный выход первого блока памяти соединен с информационным входом счетчика адреса, выход которого соединен с адресным входом второго блока памяти, выход логических условий .первого блока памяти соединен с информационным входом регистра логических" условий, выход которого соединен с первыми входами элементов И первой группы, вторые входы которыхсоединены с входом условий устройства, а выходы соединены с первыми.одами элементов ИЛИ группы, вторыеоды которых соединены с входомда операций устройства, а выходыединены с установочным входом бу-.рного регистра, выход которого соединен с информационным входом регист" ра адреса, выход которого соединен с адресным входом первого блока па-.мяти, выход косвенного адреса которого соединен с информационным вхо-. дом буферного регистра, выход :второго элемента И соединен с входом занесения регистра адреса, выход третьего элемента И соединен с входами занесения счетчика адреса буфе ного регистра и регистра логических .;условий, о т л и ч"а ю щ е е с я тем, что, с целью повышения производительности, в него введены третья группа элементов И, вторая группа элемейтов ;ИЛИ и триггер, информационный вход которого соединен с выходом первого ,элемента И, вход занесения - с выходом генератора тактовых импульсов,а прямой выход - с вторым входом третьего элемента И и с входом элемента задержки, выход которого .соединен с первыми входами элементов И второй группы и через элемент НЕ соединен с первыми входами элементов И третьей .группы, вторые входы .которых соединены с выходом второго блока памяти, а выходы - с первымивходами элементов ИЛИ второй группы, выходы которых являются опера:ционным выходом устройства, вторыевходы элементов ИЛИ второй группысоединены с выходами элементов Ивторой группы, вторые входы которыхсоединены с операционным выходомгого 826 10 15 20 30 35 40 первого блока памяти, выход третьего элемента И соединен с входом занеч сения счетчика микрокоманд, счетныи вход которого соединен со счетным входом счетчика адреса и выходом четвертого элемента И, вход которо 1,Изобретение относится к вычислительной технике и может бытьиспользовано при построении цифровых вычислительных машин.Известно микропрограммное устройство управления, содержащее дваблока памяти, два дешифратора, регистр адреса и счетчик адреса, бу-ферный регистр, регистр логических.условий, счетчик микрокоманд, шифра".тор, элементы И и элементы задержки ггпу.Недостатком данного устройстваявляется низкая производительность,обусловленная тем, что при каждомпереходе от одной последовательностимикрокоманд к другой непроизводительно используется микрокомандныйцикл. Наиболее близким к предлагаемому по технической сущности является микропрограммное устройство управ"ления, содержащее первую группу элементов И, выходы которых соединены с первыми входами буферного регистра, выходом соединенного с первыми входами элементов И второй группы, выходы которых соединены с первыми входами регистра адреса, Выход регистра адреса подключен к первому входу. первого дешифратора, выходом соединенного с адресным входом первого блока памяти, первый выход которого соединен с вторым входом буферного регистра, а второй выход - с первым входом счетчика микрокоманд. Выход счетчика микрокоманд через первый элемент И соединен с первым входом второго элемента И, выход которого соединен с вторыми входами элементов И второй группы. Третий выход первого блока го соединен с инверсным выходомтриггера, вход начальйой установки устройства соединен с входами сброса счетчика микрокоманд, триггера, регистра логическихусловий . и буферного реги стра. 2,памяти подключен к первому входу счетчика адреса, выход которого через второй дешифратор соединен с адресным входом второго блока памяти,первый выход которого является выходом устройства, а второй выходсоединен с вторым входом счетчикамикрокоманд и вторым входом счетчика адреса, .вход установки нуля которого соединен с вторым входом первого дешифратора, входом установкинуля буферного регистра и выходомтретьего элемента И, первый входкоторого подключен к выходу первогоэлемента И и через элемент НЕ кпервому входу четвертого элементаИ,: при этом второй вход второго элемента И соединен через элемент задержки с вторым входом третьего элемента И и выходом второго элементазадержки, вход которого подключенк выходу генератора тактовых импульсов и второму входу четвертого элемента И, выходом соединенного с вторым входом второго дешифратора. Четвертый выход первого блока памятисоединен с входом установки нулярегистра .адреса, второй вход которо, го является входом кода операцийустройства, первые входы элементовИ первой группы являются входамилогйческих условий устройства. Входустановки в нульрегистра логических условий соединен с выходом третьего элемента И, информационный входс выходом дешифратора логическихусловий, входы которого соединены,с вторым и третьим выходами первого блока памяти, при этом выходы ре гистра логических условий соединеныс вторыми входами элементов И первойгрупйы 21 .826 3 1020Недостатком известного устройства является низкая производитель.ность. Это обусловлено тем, что при каждом переходе от одной последовательности выполнения микрокоманд к другой производится перезапись управляющих слов из первого блока памяти в регистры и счетчики устройства. При этом каждый раз. непроизводительно расходуется микрокомандный Оцикл. Цель изобретения - повышение производительности устройства.Поставленная .цель достигается15 тем, что в микропрограммное устрой". ство управления, содержащее первый и второй. блоки памяти, регистр адре-. са, буФерный регистр, регистр логических условий, счетчик адреса сцет-.20 чик микрокоманд, первую и вторую группы элементов И, группу элементов ИЛИ, первый, второй, третий и .четвертый элементы И, элемент НЕ, элемент задержки и генератор такто 25 вых .импульсов, причем выход числа микрокоманд первого блока памяти соединен с информационным входом счетчика микрокоманд, выход которого через первый элемент И соединен с первым входом второго элемента И,30 второй .вход которого соединен с первыми входами третьего и четвертогоэлементов И и с выходом генератора тактовых импульсов, адресный выход первого блока памяти соединен с информационным входом счетчика адреса., выход которого соединен с.адресным входом второго блока памяти, выход логических условий первого блока памяти соединен с информационным входом . . регистра логических условий, выход .которого соединен с первыми входами элементов И первой группы, вторые . входы которых соединены с входом условий устройства, а выходы соеди" иены с первыми входами элементов ИЛИ группы, вторые входы которых соединены с входом кода операций устройства, а выходы соединены с установочным входом буферного регистра, выход которого соединен с информационным входом регистра адреса, выход которого соединен с адресным входом первого блока памяти, выход косвенного адреса которого соединен с информационным 55 входом буферного регистра, выход второго элемента И соединен с входом занесения регистра адреса, выход третьего элемента И соединен с входами занесения счетчика адреса, буферного регистра и регистра логических условий, дополнительно введены третья группа элементов И, вторая группа элементов ИЛИ и триггер,инФормационный вход которого соединен с выходом первого элемента И, вход занесения - с выходом генератора тактовых импульсов, а прямой выход - с вторым входом третьего элемента И и с входом элемента задержки, выход которого соединен с первыми входами элементов И второй группы. и через элемент НЕ соединен с первыми вхо" дами элементов И третьей группы,вторые входы которых соединены с выходом второго блока памяти, а выходыс первыми входами элементов ИЛИ второй группы, выходы которых являются операционным выходом устройства,вторые входы элементов ИЛИ второй группы, соединены с выходами элементов И. второй группы, вторые входы которых соединены с операционным выходом первого блока памяти, выход третьего элемента И соединен с входом занесе-ния счетчика микрокоманд, счетный вход которого соединен со счетным входом счетчика адреса и выходом четвертого элемента И, вход которого соединен с инверсным. выходом триггера, вход начальной установки. устройства соединен с входами сброса счетчика микрокоманд, триггера, регистра логических условий и буферного регистра.На фиг.1 представлена схема устройства; на фиг. 2 - временная диа" грамма работы устройства.Микропрограммное устройство управления содержит регистр 1 логических условий, группу элементов И 2, вход 3 которой является вхвдом условий устройства, группу элементов ИЛИ М, вход.5 которой является входом кода операций устройства, буферный регистр б,регистр 7 адреса, блок 8 памяти, группу элементов И 9, группу злементов ИЛИ 10, выход 11 которой является операционным ввходом устройства, элемент 12 задержки, элемент НЕ 13, группу элементов И 14, счет- чик 15 микрокоманд, элементы И 16- 19, счетчик 20 адреса, блок 21 памяти, триггер 22, генератор. 23 импульсов и вход 21 начальной установки.На фиг.2 показана временная диаграмма работы устройства, где 25/ сигнал на выходе элемента И 16; 26- импульсы на выходе генератора 23 импульсов; 27 - сигнал на выходе триггера 22; 28 - сигнал на выходе элемента 12 задержки; 29 - импульсы на выходе элемента И 17; 30импуль- сы на выходе элемента И 18 31 - имУ1 пульсы на выходе элемента И 19; 32- коды микрокоманд на выходе 11 устройства.10Устройство работает следующим образом.Для приведения устройства в исходное состояние на вход 24 подается сигнал начальной установки, по кото 15 рому буферный регистр 6 регистрлогических условий, счетчик 19 микрокоманд и триггер 22 устанавливаются в нуль.На вход 5 устройства подается код операции, который поступает через группу элементов ИЛИ 4 на установочный вход буферного регистра 6 и за" дает начальный адрес микропрограммы. Так как содержимое счетчика 15 микрокоманд равно нулю, сигнал 25 имеет единичное значение.Генератор 23 импульсов вырабатывает импульс 26, по которому вырабатываются импульсы 29 и 31,а триггер 22 приединичном значении сигнала 25 устанавливается в единицу все действия в устройстве выполняются по задним фронтам импульсов), Сигнал 27 принимает единичное значение. 35По импульсу 31 производится уменьшение на единицу содержимого счетчика 15 микрокоманд, в результате чего сигнал 25 принимает нулевое значение.По импульсу 29 начальный адрес из 40 буферного регистра 6 переписывается, в регистр 7 адреса, однако микрокоманда" на выходе блока 8 памяти появляется через время с ,определяемое временем выборки из памяти. Че рез это же время на выходе элемента 12 задержки вырабатывается единичный сигнал 28, по которому открывается группа элементов И 9 Группа элементов И 14 закрывается нудевым . 50 сигналом с выхода элемента НЕ 13.С первого выхода блока 8 памяти на информационный вход счетчика 15 микрокоманд поступает код, значенив которого на единицу меньше числа 55 микрокоманд в текущей последовательности, С второго выхода блока 8 памяти на информационный вход с,четчика 20 адреса поступает адрес второй микро- команды текущей последовательности; С третьего выхода блока 8 памяти на информационный вход регистра 1 ло,гических условий поступает код логических условий, проверяемых при реализации текущей последовательности, С четвертого выхода блока 8 памяти на информационный вход буферного регистра 6 поступает косвенный адрес первой микрокоманды следующей последовательности, С пятого выхода блока 8 памяти через группы элементов И 9 и ИЛИ 10 на выход 11 устройства поступает операционная часть первой микрокоманды М, текущей после довательности 1 поз.321. В операционной части микрокоманды кодируются микроприказы, осуществляющие воздействие на управляемую микропрограммным устройствам систему,По следующему импульсу 26 выра.- батывается импульс 30, а триггер 22 устанавливается в нуль. По импульсу 30 управляющие слова:с выходов блока 8 памяти переписываются в регистры и счетчики устройства, Через время с в соответствии. с нулевым значением сигнала 27 сигнал 28 также принимает нулевое значение, в результате чего группа элементов И 9 закрывается, а группа элементов И 14 открывается. По содержимому счетчика 20 адреса из блока 21 памяти выбирается операционная часть второй микрокоманды М 2 текущей последовательности, Код операционной части микрокоманды М 2 через группы элементов И 14 и ИЛИ 10 поступает на вход 11 устройства(поз.32).При поступлении каждого следующего импульса 26 вырабатывается импульс 31, по которому производится изменение на единицу содержимого счетчика 15 микрокоманд и счетчика 20 ад" реса. В соответствии со значением адреса в счетчике 20 адреса из блока 21 памяти считывается следующая микрокоманда и поступает на выход 11 устройства, В процессе выполнения текущей последовательности микрокоманд на вход 3 устройства из управ-. ляемой системы поступают сигналы логических условий. Сигналами с выхода регистра 1 логических условий открываются соответствующие элементы И группы элементов И 2, сигналы с выходов которой через группу элемен20 7 10208 тов ИЛИ 1 изменяют адрес. на буферном регистре 6.Если при поступлении очередного импульса 31 содержимое счетчика 15 микрокоманд оказывается равным нулю, 5 то сигнал 25 принимает единичное значение. При этом по содержимому счетчика 20 адреса из блоха 21 памя ти считывается и поступает на выход 11 устройства последняя микрокоманда текущей последовательности(поз.321,При поступлении следующего импульса 26 триггер 22 устанавливается в единицу, а по импульсу 29 адрес из буферного регистра 6 переписывается 15 в регистр 7 адреса. По этому адресу из блока 8 памяти считывается управляющее слово и поступает на информационные входы регистров и счетчиков устройства. По единичному значению сигнала 28 открывается группа элементов И 9.и на выход 11 устройства передается операционная часть первой микрокоманды спедующей последовательности с пятого выхода блока 8 памяти. В дальнейшем работа устройства выполняется аналогично вышеописанной,Таким образом, предлагаемое устройство позволяет осуществлять переходы от одной последовательности микрокоманд к другой без потери времени на перезапись управляющих слов в регистры и счетчики устройства, в отличие от протртипа, где при этом. каждый раз непроизводительно расходуется микрокоманднцй цикл.Предлагаемое устройство позволяет осуществлять переходы от одной последовательности выполнения микро- команд к другой без потерь времени на перезапись управляющих слов, не- обходимых для выполнения новой последовательности микрокоманд.иал ОРП "Патент", г. Ужгород, ул. Проектн Тираж 706 Государственного к о делам изобретени Москва, Ж, Рау Подписноемитета СССРи открытийская наб., д. 4/

СмотретьЗаявка

3397647, 17.02.1982

ОСОБОЕ КОНСТРУКТОРСКОЕ БЮРО ЮЖНОГО ГОЛОВНОГО МОНТАЖНОГО УПРАВЛЕНИЯ СРЕДСТВ СВЯЗИ ЦЕНТРАЛЬНОГО НАУЧНО ПРОИЗВОДСТВЕННОГО ОБЪЕДИНЕНИЯ "КАСКАД"

ПУШКАРЕВ ЮРИЙ ЯКОВЛЕВИЧ, ПОЛОНСКИЙ ДМИТРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.05.1983

Код ссылки

<a href="https://patents.su/6-1020826-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство с контролем

Случайный патент: Прибор для анализа газов, например, дымовых