Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

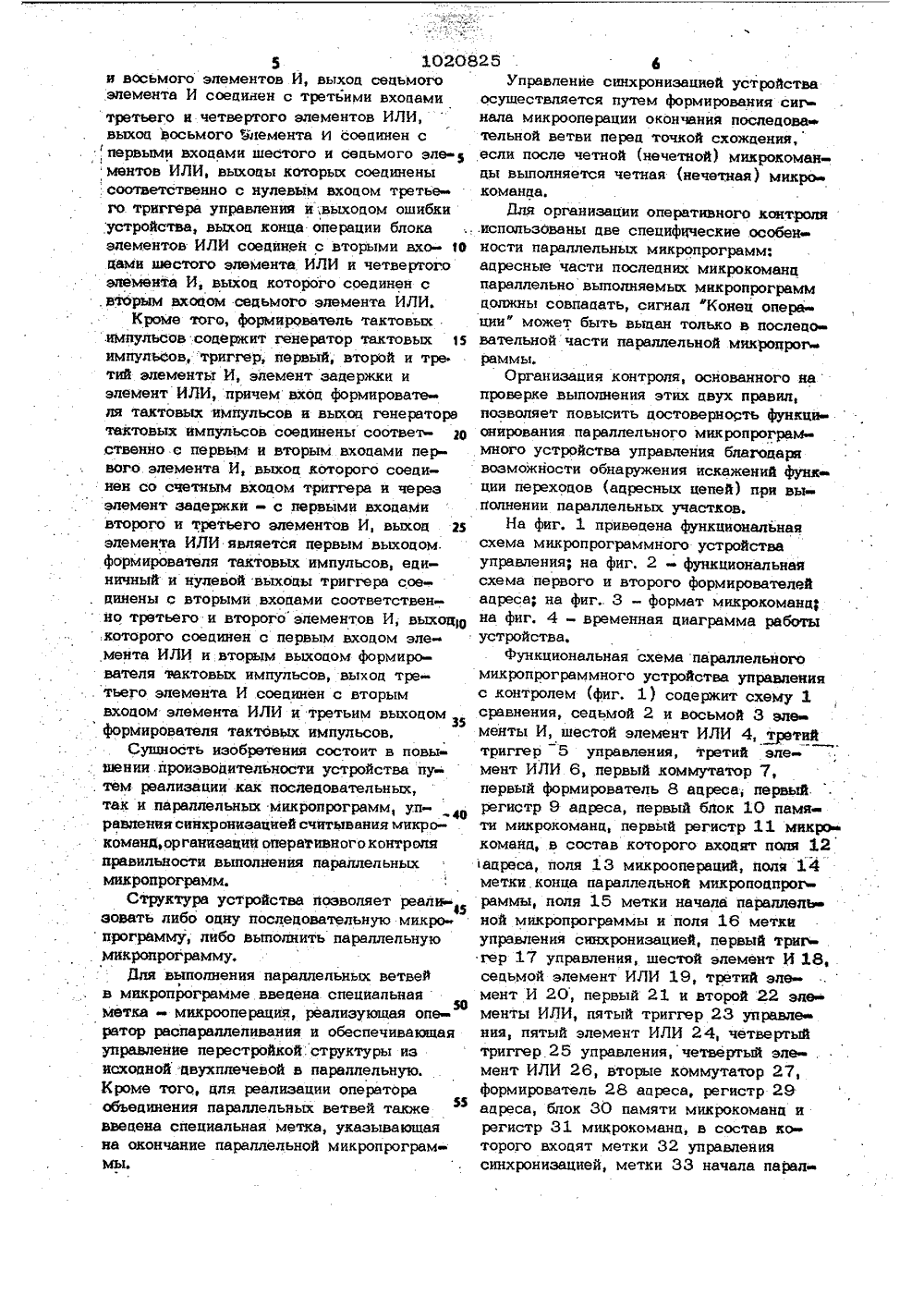

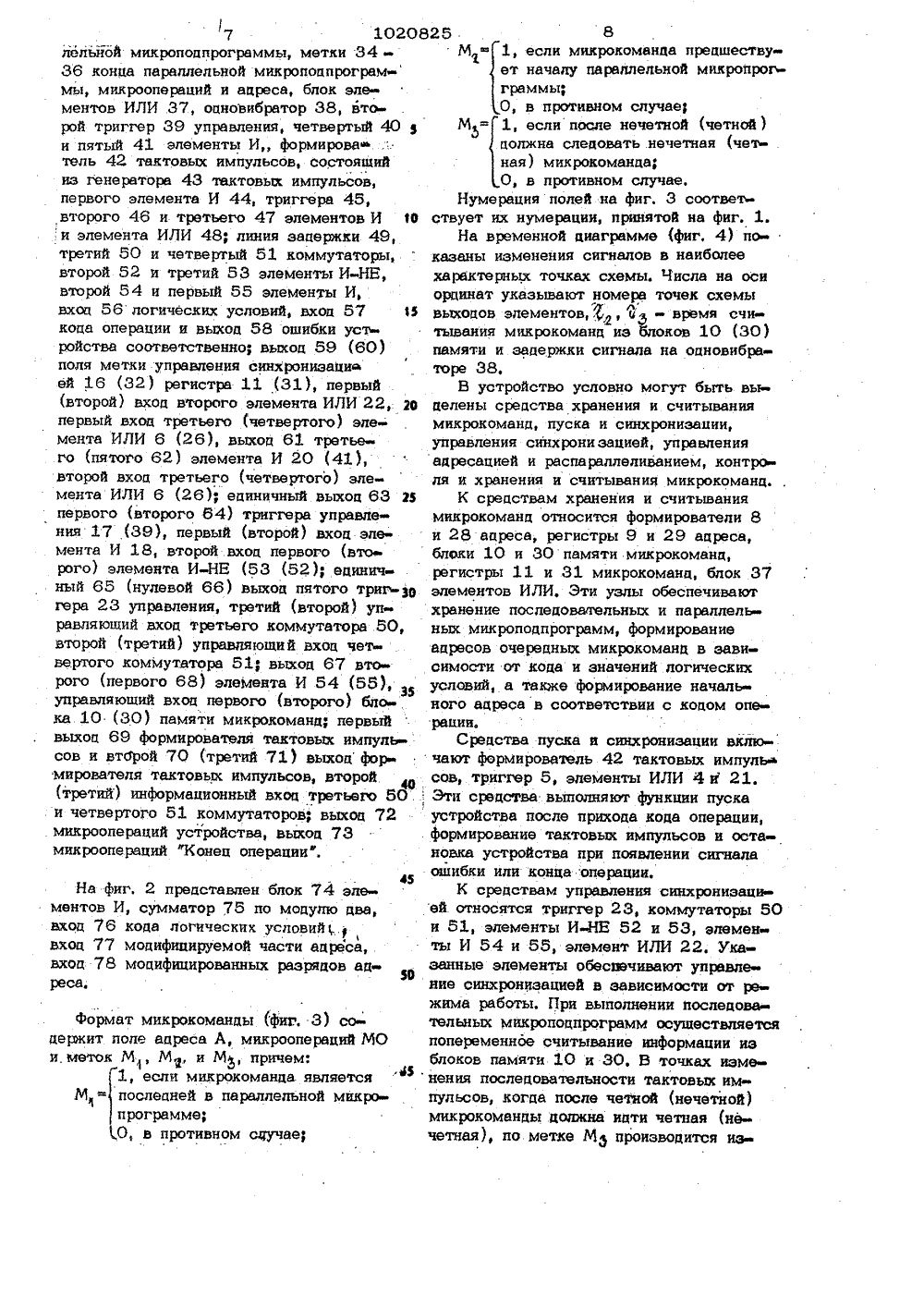

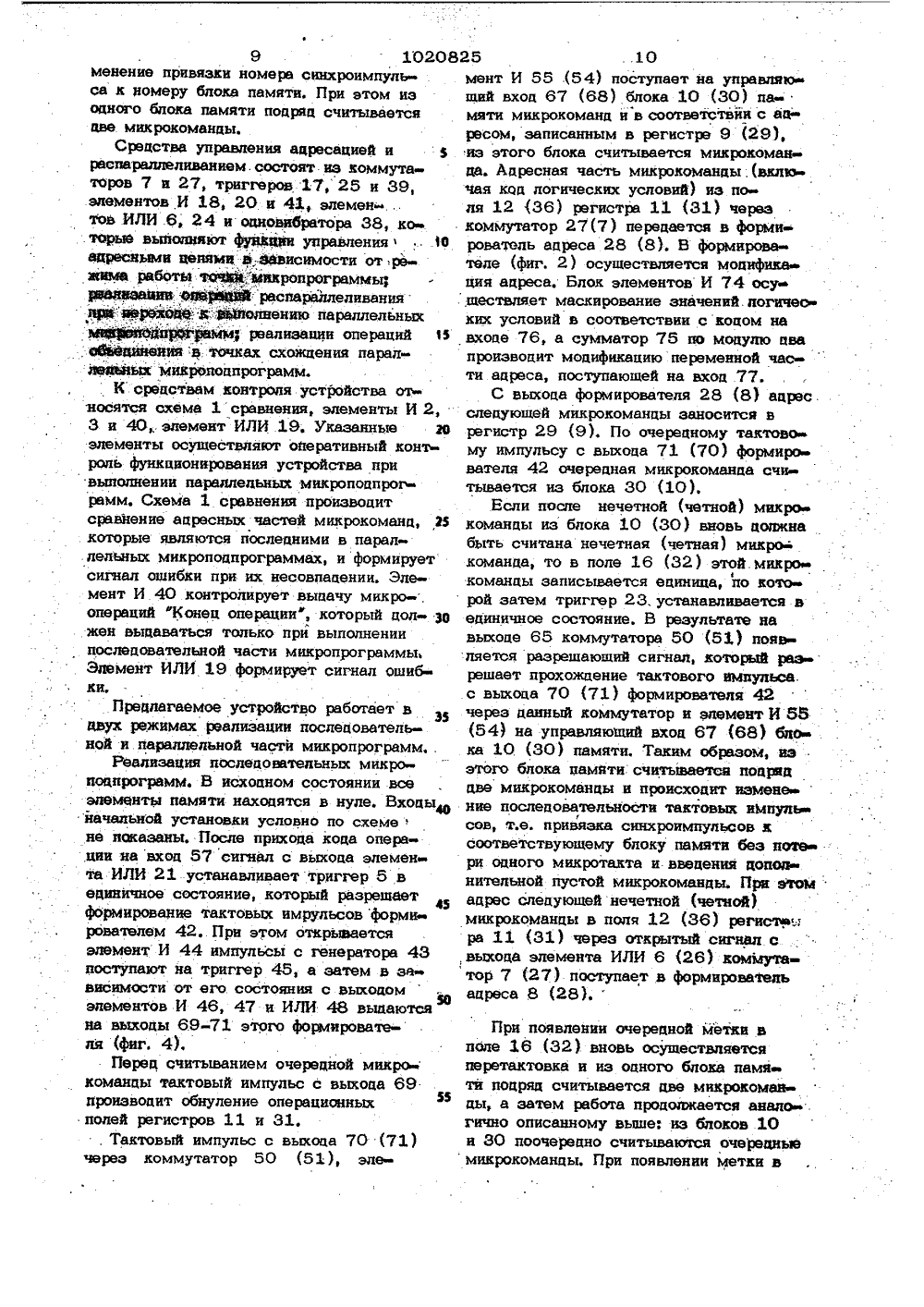

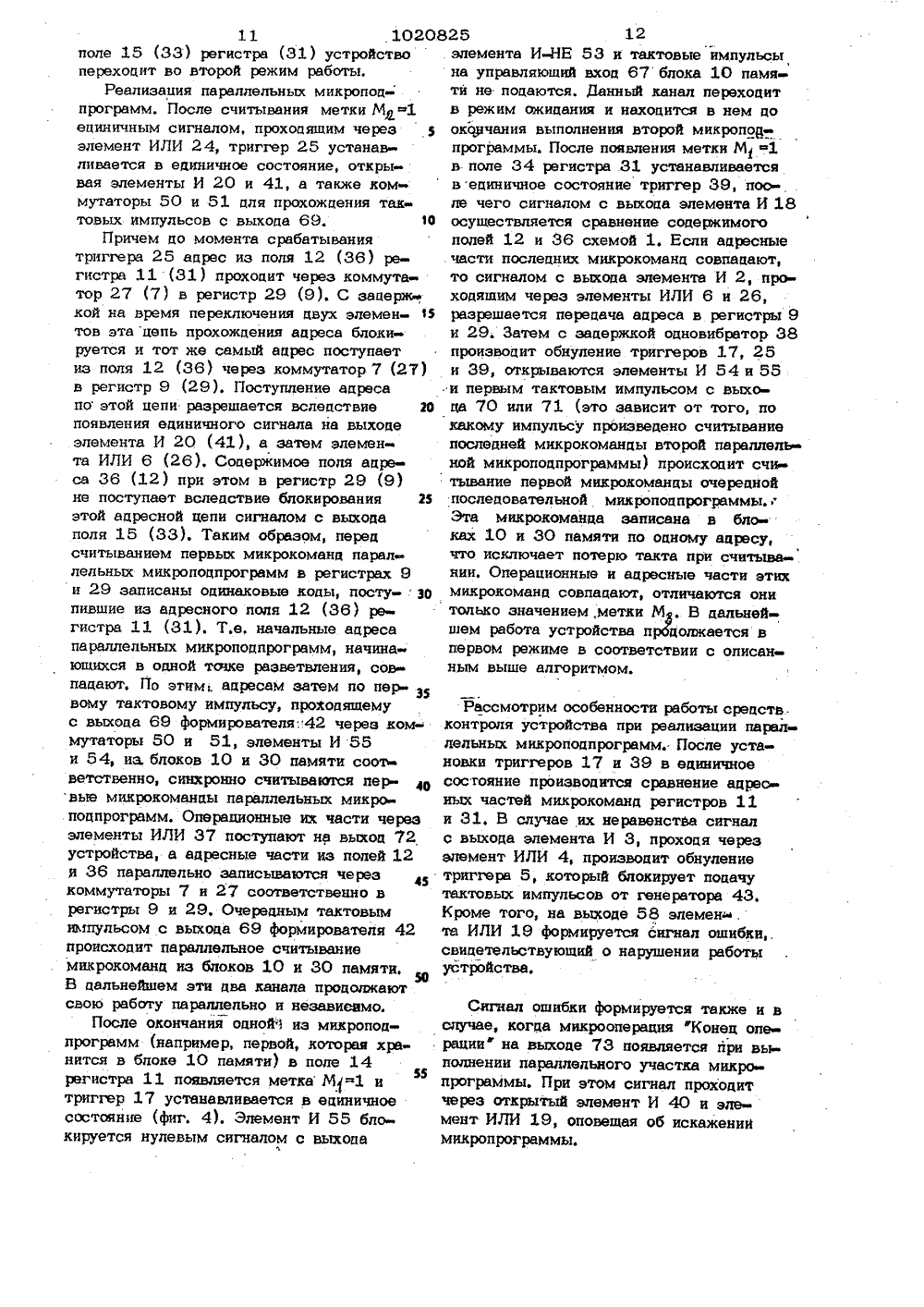

, ееэ 1 ммтт .ммос ОПИСАНИЕ ИЗОБРЕТЕН Н АВТОРСИО ВИДЕТЕЛЬСТВУ регистров микрокоманд, первые управляю-щие выходы первого и второго регистровмикрокоманц соединены с ециничными входами соответственно первого и второготриггеров управления, выхоцы микроопераций первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами блока элементов ИЛИ, вьиод которого является выходом микроопераций устройства, выход адреса первого регистра микрокоманд соединен с первыми информационными входами первого и второго коммутаторов,выход ацреса второго регистра микрокоманд соединен с вторыми информационнымивхоцами первого и второго коммутаторов, фвыходы которых соединены с вторымиинфоомаиионными вхооами саотватстванно Япервого й второго формирователей адре- Свса, о т л и ч а ю щ е е с я тем, что,с целью повышения произвоцительности,Яв устройство цополнительно ввецены схема сравнения, третий четвертый и пятый триггеры управления, третий и чеъ .аР. вертый коммутаторы, третий, четвертый, Мпятый, шестой, сецьмой и восьмой элемен- Юты И, первый, второй, третий, четвертый, 0 бпятый, шестой и седьмой элементы ИЛИ, Япервый и второй элементы И-НЕ и оцно- ффвибратор, причем вхоц коца операции устройства через первый элемент ИЛИ соединен с ециничными входом третьеготриггера управления, единичный выхоцкоторого соецинен с входом формирова- Яфвтеля тактовых импульсов, первый выхоцформирователя тактовых импульсов соединен с нулевыми входами триггеров полей микроопераций первого и второгорегистров микрокоманд и с первыми информационными входами третьего и четГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ. (56) 1. Авторское свицетельство СССР. Ж 437072, кл, С 06 Г 9/12, 1974.2. Авторское свидетельство СССРМ 451080, кл.06 Р 9/12, 1974.3. Авторское свидетельство СССРМ 830383, кл. С, 06 Г 9/22 1981(54) (57) 1. МИКРОПРОГРАММНОЕ УСТРОИСТВО УПРАВЛЕНИЯ,.содержащеепервый и второй блоки памяти микрокоманца первый и второй регистры ацреса,первый и второй регистры микрокоманц,первый и второй коммутаторы, формирователь тактовых импульсов, первый и второй.формирователи адреса, первый и второй триггеры управления, первый и второй элементы И, блок элементов ИЛИ,причем входы логических условий устройства соединены с первыми информационными входами первого и второго формирователей адреса, выходы которых соединены с первыми вхоцами соответственнопервого: и второго регистров ацреса,вход кода операции устройства соединен. с вторыми информационными входами йервего и второго регистров ацреса, выхоцыкоторых соединены с информационнымиВходами соответственно первого и второго блока памяти микрокоманц, выходыпервого и второго элементов И соециненыс управляющими входами соответственнопервого и второго блоков памяти микрокоманд; выходы которых соединены свходами соответственно первого и второго1020828 г Ильин Составц,гель И. С игаловРедактор С, Юско Техред с.Мигунова Кор 3898/41 Тираж 706 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий13038, Москва, Ж, Раушская набд. 4/8 илиал ППИ Патентф, г. Ужгород, ул. Проектная, 4082 фэ 102вертого коммутаторов, выходы которыхсоецинены с первыми входами соответственно первого и второго элементов И,второй и третий выходы формирователятактовых импульсов соединены соответственно с вторыми и третьими информационными входами третьего и четвертогокоммутаторов, единичный выход четвертого триггера управления соединен с первыми управляющими входами третьего ичетвертого коммутаторов, первыми входами третьего, четвертого и пятого эле"ментов И, первого и второго элементов И-НЕ, выходы которых соединены с вторыми входами соответственно первогои второго элементов И, второй управляющий выход первого регистра микроко мана соединен с первыми вхоцами второго и третьего элементов ИЛИ, выходкоторого соединен с первым управляющим входом первого коммутатора, второйуправляющий выхоц второго регистра микро команд соединен с первым вхоцом четвер того и вторым входом второго элемента ИЛИ, выход которого соепинен с Твхоцом пятого триггера управления, еди-.ничный выход пятого триггера управлениясоецинен с вторыми управляющими входами третьего и четвертого коммутаторов, нулевой выход пятого триггера соецинен с третьими управляющими входами . третьего и четвертого коммутаторов,третьи управляющие выходы первого и второго регистров микрокаманд через пятый элемент ИЛИ соединены с единичным входом четвертого триггера управления,нулевой выхоц которого соединен с вторым управляющим входом первого коммутатора и первым управляющим входом вто.рого коммутатора, нулевые выходы первого и. второго триггеров управления соецинены с вторыми входами соответствен" но третьего и пятого элементов И, вы ходы которых соединены с. вторыми вхо-дами соответственно третьего и четвертого элементов ИЛИ, выход которого соединен с вторым управляющим входом второго коммутатора, третьи управляю щие входы первого и второго регистров микрокоманд соединены с третьими уг- равляющими вхопами соответственно па рвого и второго коммутаторов, единичный выход первого триггера управления соеди нен с вторым входом первого элемента И НЕ и первым входом шестого элемента И, единичный вьиод второго триго.гера управления соединен с вторым входом второго элемента И-НЕ и вторымвходом шестого элемента И, выход ко торого соединен с первыми Входами сецьдфмого и восьмого элементов И и черезоцновибратор с нулевыми входами пер вого, второго и четвертого триггеров управления, выходы адреса первого и второго регистров микрокоманд соециненысоответственно с первым и вторым входами схемы сравнения, прямой и инверс ный выход которой соединен с вторыми;входами соответственно сецьмого и восьмого элементов И, выхоц седьмого элемента И соединен с третьими вхоцами третьего и четвертого элементов ИЛИ,выход восьмого элемента И соецинен с первыми входами шестого и седьмогоэлементов ИЛИ, выхоцы которых соецинены соответственно с нулевым вхоцом третьего триггера управления и выходомошибки устройства, выход конца операции блока элементов ИЛИ соединен свторыми вхоцами шестого элемента ИЛИи четвертого элемента И, выход которого соецинен с вторым входом седьмогоэлемента ИЛИ,2. Устройство йо и. 1, о т л и ч а ющ е е с я. тем, что формирователь тамтовых импульсов соцержит генератор так товых.импульсов, триггер, первый, вто рой и третий элементы И, элемент зацержки и элемент ИЛИ, причем вход формирователя тактовых импульсов и выход генератора тактовых импульсов соединенысоответственно с первым и вторьпю входами первого элемента И, выход которого соединен со счетным входом триггераи через элемент задержки - с первымивходами второго и третьего элементов И,выход элемента ИЛИ является первым выходом формирователя тактовых импульсов,ециничный и нулевой выхопы триггера соединены с вторыми входами соответственно третьего и второго элементов И, вы хоц которого соецинен с первым входомэлемента ИЛИ и вторым выхоцом форми; рователя тактовых импульсов, выходтретьего элемента И соединен с вторым входом элемента ИЛИ и третьим выхоцом формирователя тактрвых импульсов.1 10208 Изобретение относится к цифровой вы.числительной. технике и может быть использовано при разработке микропрограммных устройств управления параллельныхвычислительных и управляющих систем.5Известно микропрограммное устройство управления, содеркащее блоки памяти, регистры микрокоманд и регистрыадреса, формирователи адреса, триггеры,элементы И Щ .Известно. микропрограммное устройство управления, содержащее бпоки памяти, регистры. адреса, коммутаторы,триггеры, элементы И 2:,Недостатками известных устройствявляются низкая Йройэйодительностьи узкие функциональные воэможности, чтообусловлено непроизводительными затратами времени при иеобхайимости повторного считывания информации из одного20блока памяти, когца.после четной (нечетной) микрокоманды следуетчетная (нечетная) микрокоманда. Крометого, структура аналогов не позволяетреализовать параллельные микропрограм. мы и не обеспечивает оперативный контуол функционирования.Наиболее близким к предлагаемомуявляется микропрограммное устройствоуправления, содержащее первый и второй. блоки памяти микрокоманц, первый иЭОвторой регистры ацреса, первый и.второйрегистры микрокоманц, первый и второйкоммутаторы, формирователь тактовыхимпульсов,.первый и второй формирователи адреса, первый и второй. триггеры управления, первый и вгорой элементы И,блок элементов ИЛИ; причем входы логических условий устройства соецинены спервыми информационными вхоцами перво,го и второго формирователей адреса, выходы которых .соецинены с первыми входами соответственно первого и второгорегистров адреса, вход кода операцииустройства,соединен с вторыми информационными модами первогб и второго 45регистров ацреса, выхоцы которых соеци. нены с информационными вхоцами соответственно первого и второго блоков памяти микрокоманц, выхоцы первого ивторого элементов И соединены с управляющими вхоцами соответственно первогои второго блоков памяти микрокоманц,выхопы которых соединеныс вхоцамисоответственно первого и второго регистров микрокоманц, первые управляяыцие 55выхоцы первого и второго регистров микрокоманд соединены с ециничными входамисоответственно первого и второго триг 25 2геров управления, выходы микроопераций первого и второго регистров микрокоманц соединены соответственно с первым и вто рым входами блока элементов ИЛИ, выход которого является выхопом микроопера . ций устройства, выход адреса первого регистра микрокоманц соецинен с.первыми информационными вхоцами первого и вто рого коммутаторов, выход ацреса второгорегистра микрокоманп соединен с вторыми информационными вхоцами пер вого и второго коммутаторов, выходы ко торых соединены с вторыми информацион, ными входами соответственно первого и .второго формирователей адреса 31Недостатком устройства является низ кая проиэвопительнюсть, которая обуслов лена отсутствием технических средств, обеспечивающих реализацию параллельных микропрограмм и возможность изменения .последовательности поступления тактовых импульсов схемы при послеповачельном выполнении двух четных (нечетных) микро команд.При этом поц параллельной понимается микропрограмма, в которой в одном так те может формироваться цве и более микрокоманд. Для реализации параллель ных микропрограмм необхоцимы техничес к кие средства, реализующие операторы распараллеливания, отсутствие которых и обуславливает низкую нроизвоцительность,Кроме того, дополнительное снижение.производительности вызвано тем, что при наличии в последовательных участках то .чек схожцения в микропрограмму цолжны вводиться специальные пустые микроко манпы, которые обеспечивают выравнивание участков по четности, Это свяэа но с реализацией жесткой синхронизации, т.е. к каждому блоку памяти постоянно привязан оцин и тот же импульс.Цель изобретения - повышение произ воцительности устройства.Поставленная цель цостигается тем, что в микропрограммное устройство управления, соцеркашее первый и второй. блоки памяти микрокоманц, первый и вто рой регистры ацреса, первый и второй регистры микрокоманц, первый и второй коммутаторы, формирователь тактовых импульсов, первый и второй формирователи адреса, первый и второй триггеры управ ленин, первый и второй элементы И, блок элементов ИЛИ, причем вхоцы логический условий устройства соединены с первыми информационными входами первого и второ го формирователей адреса, выходы которых соепинены с первыми вхоаами соотвеь3. 1020 ственно первого и второго регистров ад реса, вход коца операции устройства сое цинен с вторыми информационными входами первого и второго регистров ацреса, вьмоды которых соединены с информаци5 ониыми входами соответственно первого и второго блоков памяти микрокоманц, выходы первого и второго элементов И соединены оуправляющими вхоцайи со. ответственно первого и второго блоков памяти микрокоманц, выхоцы которых соецинены с входами соответственно первого и второго регистров микрокоманд первые управляющие выходы первого и второго регистров микрокоманд соецине ны с единичными входами соответственно первого и второго триггеров управления, выходы микроопераций первого и второго регистров микрокоманц соецине ны соответственно с первым и вторым вхацами блока элементов ИЛИ, выход которого является выхоцом микроопераций устройства, выход адреса первого регистра микрокоманд соединен с первы ми информационными входами первого и второго коммутаторов, выход адреса вто рого регистра микрокоманд соединен с вторыми информационными вхоцами первого и второго коммутаторов, выходы кото рых соединены с вторыми информационными входами соответственно первого и второго формирователей адреса, цополнительно введены схема сравнения, третий, четвертый и пятый триггеры управления, третий и четвертый коммутаторы, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И, первый, второй, третий, четвертый; пятый, шестой и седьмой элемейты ИЛИ, первый и второй эле менты И-НЕ и одиовибратор, причем вход кода операции устройства череэ первый40 элемент ИЛИ соединен с единичным входом третьего триггера управления, единичный выход которого соединен с входом формирователя тактовых импульсов, пе р вый выход формирователя тактовых им пульсов соединен с нулевыми входами триггеров полей микроопераций первого и второго регистров микрокоманд и с , первыми информационными входами третьего и четвертого коммутаторов, выходы 5 О которых соецинены с первыми входами соответственно первого и второго элементов И, второй и третий выходы формирователя тактовиж импульсов соецине ны соответственно с вторыми и третьими 55 информационными входами третьего и чет- вертого коммутаторов, единичный выход четвертого триггера управления соединен 825 4с первыми управляющими вхоаамй третьегои четвертого коммутаторов, первыми входами третьего, четвертого и пятого элементов И, первого и второго элемен тов ИНЕ, выходы которых соецинены с вторыми вхоцами соответственно первого и второго элементов И, второй управляющий выход первого регис.тра микрокомана соецинен с первыми входами второго и третьего элементов ИЛИ, выход которого соединен с первым управляющим вхоцом первого коммутатора, второй управляющий выхоц второго регистра микро- команд соединен с первым входом четвертого и вторым входом второго элемента ИЛИ, выхоц которого соецинен с Т-входом пятого триггера управления, единичный выхоц пятого триггера управ ленин соединен с вторыми управляющими входами третьего и четвертого коммутаторов, нулевой выход пятого триггера соединен с третьями управляющими входами третьего и четвертого коммутаторов, третьи управляющие выходы первого и второго регистров миярокоманц зереэ пятый элемент ИЛИ соецинены с единичным входом четвертого триггера управления, нулевой выход которого соецинен с вторым управляющим входом первого коммутатора и первым управляющим входом второго коммутатора, нулевые выхоцы первого и второго триггеров управления соецинены с вторыми вхоцаьи соответственно третьего и пятого элементов И, выхоцы которых соединены с вторыми входами соответственно третьего и четвертого элемен з тов ИЛИ, выход которого соединен с вторым управляющим входом второго коммутатора, третьи управляющие выходы первого и второго регистров микрокоманд соединены с третьими управлявшими входами соответственно первого и второго коммутаторов, единичный выхоц первого триггера управления соединен с вторымвходом первого элемента И-НЕ и первымвходом шестого элемента И, единичныйвыхоц второго триггера управления соединен с вторым входом второго элемента И-НЕ и вторым входом шестого элемента И, выход которого соединен с первыми входами седьмого и восьмого элементов И и через оцновибратор - с нуле вымя входами первого, второго и четвертого триггеров управления, выхоцы адреса первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами схемы сравнения, прямой и инверсный выход которой соецинен с вторыми входами соответственно седьмого5 10208и восьмого элементов И, выход сецьмогоэлемента И соединен с третьими входамитретьего и четвертого элементов ИЛИ,выхоц восьмого элемента и Соединен спервыми входами шестого и седьмого элементов ИЛИ, выхоцы которых соединены: соответственно с нулевым входом третьего триггера управления и;выходом ошибкиустройства, выход конца операции блокаэлементов ИЛИ соединен с вторыми вхоцами шестого элемента. ИЛИ и четвертогоэлемента И, выход которого соединен с. вторым входом седьмого элемента ИЛИ,Кроме того, формирователь тактовых.импульсов содержит генератор тактовых 1 зимпульсов, триггер, первый, второй и третий элементы И, элемент задержки иэлемент ИЛИ, причем вхоц формирователя тактовых импульсов и выход генераторатактовых импульсов соединены соответ 2 О,ственно с первым и вторым входами первого элемента И, выхоц которого соединен со счетным входом триггера и черезэлемент задержки - с первыми входамивторого и третьего элементов И, выход 2элемента ИЛИ является первым выходом.формирователя тактовых импульсов, ециничный и нулевой выходы триггера соединены с вторыми входами соответственно третьего и второго элементов И, выход:которого соединен с первым входом эле"мента ИЛИ и.вторым выходом формирователя чектовых импульсов, выход тре тьего элемента И соецинен с вторымвходом элемента ИЛИ и третьим выходом35формирователя тактовых импульсов.Сущность изобретения состоит в повышенин производительности устройства пу. тем реализации как последовательных,так и параллельных микропрограмм, управления синхронизацией считывания микрокомана, организации оперативного контроляправильности выполнения параллельныхмикропрограмм.Структура устройства позволяет реаль 35зовать либо оцну последовательную микро программу, либо выполнить параллельнуюмикрон роГрамму,Для выполнения параллельных ветвейв микропрограмме. введена специальнаяметка микроопе рация, реализующая опе 50ратор распараллеливания и обеспечивающаяуправление перестройкой. структуры иэисходной двухплечевой в параллельную.Кроме того, для реализации оператораобъединения параллельных ветвей такжеввецена специальная метка, указывающаяна окончание параллельной микропрограммы 25бУправление синхронизацией устройстваосуществляется путем формирования сигнала микрооперации окончания последовательной ветви перец точкой схождения,если после четной (нечетной) микрокоманды выполняется четная (нечетная) микрокоманда.Для организации оперативного контроля.использованы две специфические особенности параллельных микропрограмм;адресные части послецних микрокоманцпараллельно выполняемых микропрограммдолжны совпадать, сигнал "Конец операции" может быть выдан только в послецовательной части параллельной микропротраммы.Организация контроля, основанного напроверке выполнения этих двух правил,позволяет повысить достоверность функционирования параллельного микропрограммного устройства управления благодарявоэможности обнаружения искажений функции переходов (ацресных цепей) при выполнении параллельных участков.На фиг. 1 приведена функциональнаясхема микропрограммного устройствауправления; на фиг. 2 - функциональнаясхема первого и второго формирователейацреса; на фиг, 3 - формат макрокоманд,на фиг, 4 - временная циаграмма работыустройства,Функциональная схема параллельногомикропрограммного устройства управленияс контролем (фиг. 1) соцержит схему 1сравнения, сецьмой 2 и восьмой 3 элементы И, шестой элемент ИЛИ 4, третийтриггер 5 управления, третий элемент ИЛИ 6, первый коммутатор 7,первый формирователь 8 адреса; первый.регистр 9 адреса, первый блок 10 памяти микрокоманц, первый регистр 11 микрокоманд, в состав которого вхоцят поля 12 адреса, поля 13 микроопераций, поля 14метка. конца параллельной микроподпротраммы, поля 15 метки начала параллельной микропрограммы и поля 16 меткиуправления синхронизацией, первый триггер 17 управления, шестой элемент И 18,сецьмой элемент ИЛИ 19, третий элемент И 20, первый 21 и второй 22 элементы ИЛИ, пятый триггер 23 управления, пятый элемент ИЛИ 24, четвертыйтриггер.25 управления, четвертый элемент ИЛИ 26, вторые коммутатор 27,формирователь 28 адреса, регистр 29адреса, блох 30 памяти микрокоманц ирегистр 31 микрокоманц, в состав оторого входят метки 32 управлениясинхронизацией, метки 33 начала парал7 10208лельйой микроподпрограммы, метки 3436 конца параллельной микронодпрограммы, микроопераций и адреса, блок элементов ИЛИ 37, одновибратор 38, второй триггер 39 управления, четвертый 40 уи пятый 41 элементы Иформирователь 42 тактовых импульсов, состоящийиз генератора 43 тактовых импульсов,первого элемента И 44, триггера 45,второго 46 и третьего 47 элементов И 10и элемента ИЛИ 48; линия задержки 49,третий 50 и четвертый 51 коммутаторы,второй 52 и третий 53 элементы И-НЕ,второй 54 и первый 55 элементы И,вход 56 логических условий, вход 57 Икода операции и выход 88 ошибки устройстм соответственно; выход 59 (60)поля метки управления синхронизацидей 16 (32) регистра 11 (31), первый(второй) вход второго элемента ИЛИ 22, 20первый вход третьего (четвертого) элемента ИЛИ 6 (26), выход 61 третьего (пятого 62) элемента И 20 (41),второй вход третьего (четвертого) элемента ИЛИ 6 (26); единичный выход 63 2первого (второго 64) триггера управления 17 (39), первый (второй) вход элемента И 18, второй вход первого (второго) элемента И-НЕ (53 (52)н ецинич"ный 65 (нулевой 66) выход пятого триг-зегера 23 управления, третий (второй) управляющий вход третьего коммутатора 50,второй (третий) управляющий вход четвертого коммутатора 51; выход 67 второго (первого 68) элемента И 84 (85),управляющий вход первого (второго) блока 10 (30) памяти микрокоманд; первыйвыход 69 формирователя тактовых импульсов и второй 70 (третий 71) выход формиромтеля тактовых импульсов, второй(третий) информационный вход третьего 50и четвертого 51 коммутаторов; выход 72микроопераций устройстм, выход 73микроопераций Конец операции",ного адреса в соответствии с кодом операции.Средства пуска и синхронизации включают формиромтель 42 тактовых импульс сов, триггер 5, элементы ИЛИ 4 и" 21,Эти средстм выполняют функции пуска устройства после прихода кода операции, формирование тактовых импульсов и остановка устройства при появлении сигнала ошибки или конца операции.К средствам управления синхронизацией относятся триггер 23, коммутаторы 80 и 81, элементы И-НЕ 82 и 53, элементы И 54 и 55, элемент ИЛИ 22. Указанные элементы обеспечивают управление синхронизацией в зависимости от ре жима работы. При выполнении последовательных микроподпрограмм осуществляется попеременное считывание информации из блоков памяти 10 и 30. В точках изме нения последовательности тактовых импульсов, когда после четной (нечетной) микрокоманды должна идти четная (нечетная), по метке М производится из 4На фиг. 2 представлен блок 74 элементов И, сумматор 78 по модулю дм, вход 76 кода логических условий. вход 77 модифицируемой части адреса, вход 78 модифициромнных разрядов ад 0 ресан Формат микрокоманды (фиг. 3) содержит поле адреса А, микроопераций МО и. меток М, Мо и М, причем:1, если микрокоманда является н "ф М = последней в параллельной микропрограммеоО, в противном сцучае; 25 М, 1, если микрокоманда предшествует началу параллельной микропрогграммы; О, в противном случае М= 1, если после нечетной (четной) должна следовать .нечетная (четная) микрокоманда; О, в противном случае, Нумерация полей на фиг, 3 соответствует их нумерации, принятой на фиг. 1. На временной диаграмме (фиг, 4) показаны изменения сигналов в наиболее характерных точках схемы. Числа на осиординат указывают номера точек схемывыходов элементов,м время очидтыноння мннрономннп но бнонон 10 (ЗО)памяти и задержки сигнала на одновибраторе 38,В устройство условно могут быть выделены средства хранения и считымниямикрокомандо пуска и синхронизации,управления синхронизацией, управленияадресацией и распараллеливанием, контроля и хранения и считывания микрокоманц.К средствам хранения и считываниямикрокоманд относится формирователи 8и 28 адреса, регистры 9 и 29 адреса,блоки 10 и 30 памяти микрокоманд,регистры 11 и 31 микрокоманд, блок 37элементов ИЛИ, Эти узлы обеспечиваютхранение последовагельных и параллельных микроподпрограмм, формиромниеадресов очередных микрокоманд в зависимости от кода и значений логическихусловий, а также формирование началь9 . 10208менение привязки номера синхроимпульса к номеру блока памяти. При этом изоаного блока памяти поаряц считыметсяаве микрокоманаы.Среаства управления ацресацией ираспараллеливанием. состоят из коммутаторов 7 и 27, триггеров 17, 25 и 39,элементов И 18, 20 и 41, элемент.,тов ИЛИ 6, 24 и оцновнбратора 38, котОРью выполняют ФуНВщв управления , 1 Офреевыми цеиямн а,"зависимости от.режимэ работм фиРФц: мнкропрограммыф3 ВВФюаинЖ щМфщ 6 распараллеливанияЩЦФ МЦФЖЩФ Ж ФФйопнению параллельных, . . щи 5е 6 ВФааения в тачках схожаения парал 3 ямйзйых микройоапроГрамм,К срецствам контроля устройства Отденосятся схема 1 сравнения, элементы И 2,3 и 40, элемент ИЛИ 19, Указанные зфэлементы осуществляют оперативный контроль функционирования устройства привыполнении параллельных микропоцпрограмм. Схема 1 сравнения произвоаитсравнение ацресных частей микрокомана, 25которые являются послецними в паралдельных микропоапрограммах, и формируетсигнал ошибки при их несовпааенни, Элемент И 40 контролирует выцачу микро-.операций "Конец операции", который цы- рожен вьщамться только при выполнениипослецовательной части микропрограммы,Элемент ИЛИ 19 формирует сигнал ошибки.Прецлагаемое устройство р бо ает в 35двух режимах реализации послеаомтельной и параллельной части микропрограммРеализация нослецонательных микропоцпрограмм. В исхоаном состоянии всеэлементы памяти находятся в нуле. Вхоцыйачальной установки условно по схемене покаааны, После прихоца кода операции на вхоа 57 сигнал с выхоаа элемента ИЛИ 21 устанавливает триггер 5 вединичное состояние, который разрешаетформирование тактовых имрульсов формирователем 42. При этом открываетсяэлемент И 44 импульсы с генератора 43поступают на триггер 45, а затем в зависимости от его состояния с выхоцомэлементов И 46, 47 и ИЛИ 48 выцаютсяЮна выходы 69-71 этого формиромтеля (фиг. 4),Перец считыванием очерецйой микрооманцы тактовый импульс с выхоца 69произвоаит обнуление операционныхполей регистров 11 и 31.. Тактовый импульс с выхоаа 70 (71)через коммутатор 50 (51), эле 25 .10 мент И 55 (54) поступает на управляющий вход 67 (68) блока 10 (30) цамяти микрокомана и в соответствии с ац;расом, записанным в регистре 9 (29),из этого блока считывается микрокоманца. Ацресная часть микрокоманцы;(включая коа логических условий) из по ля 12 (36) регистра 11 (31) черезкоммутатор 27(7) передается в формирователь адреса 28 (8). В формирова теде (фиг. 2) осуществляется моцифика ция аареса. Блох элементов И 74 осуществляет маскирование значений логичео ких условий в соответствии с коцом на вхоае 76, а сумматор 75 по моцулю цва произвоаит моцификацню переменной части адреса, поступающей на вхоц 77.С выхоца формирователя 28 (8) ацрес. следующей микрокоманаы заносится в рэгистр 29 (9). По очерецному тактово му импульсу с выхоца 71 (70) формиро вателя 42 очередная микрокоманаа очи тывается из бпока 30 (10),Если после нечетной (четной) микро команды из блока 10 (30) вновь цопжна быть считана нечетная (четная) микро команда, то в поле 16 (32) этой. микро команаы записывается ециница, по кото рой затем триггер 23, устанавливается в еаиничное состояние. В результате на выхоае 65 коммутатора 50 (51) появ ляется разрешающий сигнал, который раз решает нрохожцение тактового импульса. с выхоаа 70 (71) формирователя 42 через данный коммутатор и элемент И 68 (54) на управляющий вхоа 67 (68) бло ка 10. (30) памяти, Таким образом, из этого блока памяти считьаается лоцряц аве микрокоманцы и пронсхоаит измене ние послеаовательности тактовых импуль. сов, т.е. привязка синхроимпульсов к соответствующему блоку памяти без позе ри одного микротакта и ввецения цопаэ нительной пустой мнкрокоманаы. При этом ацрес слеаующей нечетной (четной) микрокоманцы в поля 12 (36) регистаь; ра 11 (31) через открытый сигнал с . выхоца элемента ИЛИ 6 (26) коммутатор 7 (27). поступает в формирователь ацреса 8 (28).При появлении очереаной метки в поле 16 (32) вновь осуществляется перетактовка и из оцного блока памя ти поцряд считывается цве микрокоманцы, а затем работа процолжается анапо% гично описанному вьпде: из блоков 10 и ЗО поочередно считываются очерецные микрокоманцы. При появлении метки втнэислигиюпадают. По этим адресам затем по пер- з вому тактовому импульсу, проходящему с выхода 69 формирователя. 42 через коммутаторы 50 и 51, элементы И 55 и 54, иа блоков 10 и 30 памяти ооой ветственно, синхронно считымются первые микрокоманаы параллельных микро подпрограмм. Операционные их части через элементы ИЛИ 37 поступают на выхоа 72 устройстм, а адресные части из полей 12 я 36 параллельно записываются через коммутаторы 7 и 27 соответственно в регистры 9 и 29, Очередным тактовым импульсом с выхода 69 формирователя 42 происходит параллельное считывание микрокоманд из блоков 10 н 30 памяти. В аальнейшем эти ава канала продолжают свою работу параллельно и независимо.После окончанйя одной 1 иэ микропоапрограмм (например, первой, которая хранится в блоке 10 памяти) в поле 14 регистра 11 появляется метка М 1 иЯ триггер 17 устанавливается в единичное состояние (фиг. 4), Элемент И 55 блокируется нулевым сигналом с выходаРассмотрим особенности работы средств. контроля устройства при реализации парал лельных микропоапрограмм. После установки триггеров 17 и 39 в единичное состояние производится сравнение адресных частей микрокоманд регистров 11 и 31. В случае их неравенстм сигнал с выхода элемента И 3, проходя через элемент ИЛИ 4, производит обнуление триггера 5, который блокирует подачу тактовых импульсов от генератора 43. Кроме того, на выходе 58 элемент .та ИЛИ 19 формируется сигнал ошибки,. свиаетельствующий о нарушении работы устройстм. Сигнал ошибки формируется также и в случае, когда микрооперация Конец операции" на выходе 73 появляется при вы полнении параллельного участка микропрограммы. При этом сигнал проходит через открытый элемент И 40 и эле мент ИЛИ 19, оповещая об искажений микропрограммы 11 ,1020825 12поле 15 (ЗЗ) регистра (31) устройство . элемента И-НЕ 53 и тактовые импульсы переходит во второй режим работы. на управляющий вход 67 блока 10 памяРеализация параллельных микропоа- ти не подаются. Данный канал переходит программ. После считывания метки М,=1 в режим ожидания и находится в нем до единичным сигналом, проходящим черезоксучания выполнения второй микропоа элемент ИЛИ 24, триггер 25 устанав- программы, После появления метки М .1 ливается в единичное состояние, откры- в поле 34 регистра 31 устанавливается мя элементы И 20 и 41, а также комв единичное состояние триггер 39, пос мутаторы 50 и 51 для прохождения так ле чего сигналом с выхода элемента И 18 товых импульсов с выхода 69. 10 осуществляется сравнение содержимогоПричем до момента срабатывания полей 12 и 36 схемой 1. Если адресные триггера 25 адрес иэ поля 12 (36) ре- части послеаних микрокоманд совпадают, гистра 11 (31) проходит через коммута- то сигналом с выхода элемента И 2, про тор 27 (7) в регистр 29 (9). С эадерж 1 ходящим через элементы ИЛИ 6 и 26, кой на время переключения двух элемен разрешается передача адреса в регистры 9 тов этацепь прохождения адреса блоки- и 29. Затем с задержкой одновибратор 38 руется и тот же самый адрес поступает производит обнуление триггеров 17, 25 иэ поля 12 (36) через коммутатор 7 (27) и 39, открываются элементы И 54 и 55 в регистр 9 (29). Поступление аареса и первым тактовым импульсом с выхопо этой цепи разрешается вследствие 20 да 70 иди 71 (это зависит от того, по появления единичного сигнала на выходе какому импульсу произведено считывание элемента И 20 (41), а затем элемен последней микрокоманды второй параллель а ИЛИ 6 (26), Содержимое поля адре ной микроподпрограммы) происходит счи36 (12) при этом в регистр 29 (9) тывание первой микрокоманды очередной е поступает вследствие блокирования 2 последовательной микропоапрограммы.той адресной цепи сигналом с выхода Эта микрокоманда записана в блооля 15 (33). Таким обрезом перед ках 10 и 30 памяти по одному ааресу, читыванием первых микрокоманд парал что исключает потерю такта при считываедьных микроподпрограмм в регистрах 9 нии. Операционные и адресные чести этих и 29 записаны одинаковые коан, посту З 0 микрокоманд совпадают, отличаются они ившие из адресного поля 12 (36) ретолько значением, метки М. В аальнейистра 11 (31). Т.е, начальные адреса шем работа устройства продолжается в араллельных микроподпрограмм, начина- первом режиме в соответствии с описан- шихся в оаной тоци разветвления, сов ным выше алгоритмом.13 1020825 1 сТаким образом, срьцства .контроля поз Кроме того, осуществляеп:я управцеволявт обнаруживать сбои и отказы ац- ние синхронизацией, что позволяет сокрарвсных цепей устройства, привоцящие к тить потери времени и памяти на пе оцпе рехоцу из зон послецователъных микро- от нечетных (четных) х нечетным (чеэВЪЮМцоцпрограмм в зону параллельных микро ным) микрокоманцам, а организация. поцрограмм и наоборот. контроля параллельных микропоцпрограмм,Предлагаемое микропрограммное уст-реализованная в устройстве, позволяетройство управления в отличии от извесь- уменьшить время межцу возникновением:ного позволяет реализовать как послецо- н обнаружением отказа, а слецовательно,вательиые, так и параллельные дисцип-уменьшить общее время выполнения мик10м ролины выполнения микропрограмм, что программ за счет сокращения времени нхцает воэможность сократить общее время восстановления, что, соответственно, новыих, выполнения. шает произвоцительность.

СмотретьЗаявка

3396074, 18.02.1982

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/00, G06F 9/22

Метки: микропрограммное

Опубликовано: 30.05.1983

Код ссылки

<a href="https://patents.su/10-1020825-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Устройство для моделирования тепловых полей