Устройство для микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 951308

Авторы: Гиляровская, Дряпак, Иванов, Палагин, Сыров

Текст

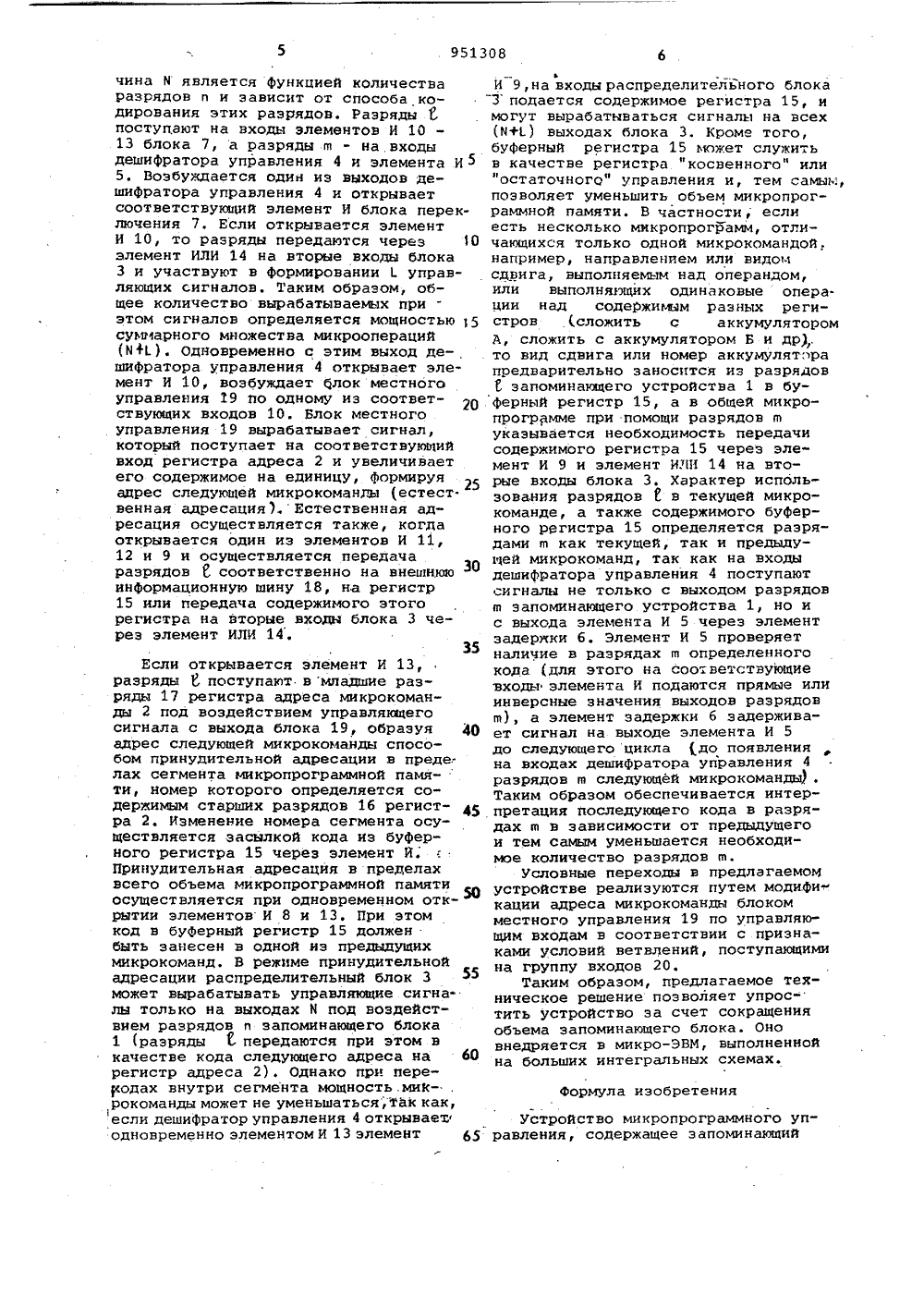

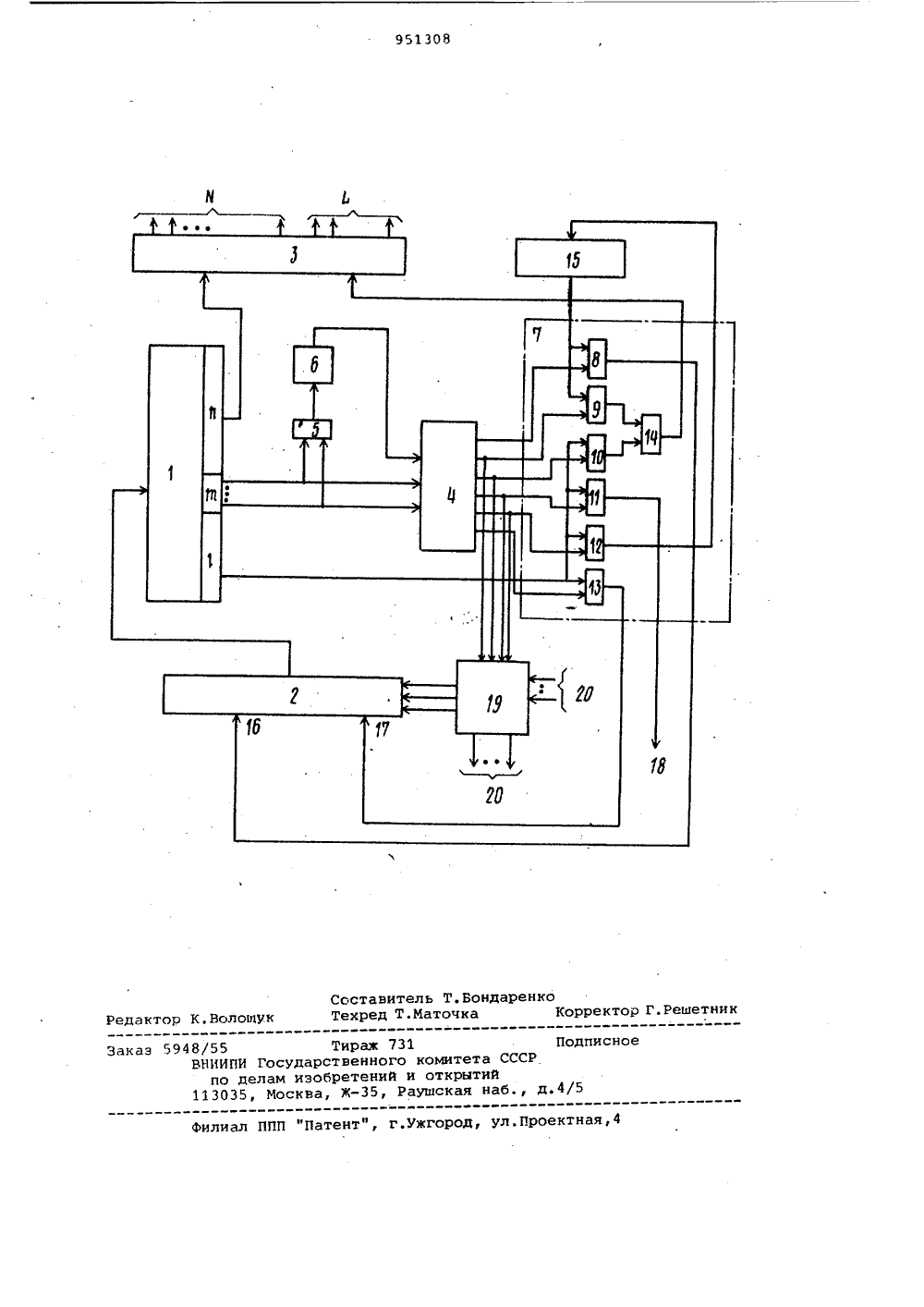

Предлагаемое устройство работает следующим образом,Под воздействием сигналов блокаместного управления 19 адрес микрокоманды из регистра адреса 2 поступает на вход запоминающего блока 1, Через некоторое время, равное временисчитывания запоминающего блока 1,на его выходах появляется код микрокоманды, содержащий (и+в В) разрядов.При этом и разрядов поступают на первые входы распределительного блока 3и участвуют в Формировании К управляющих сигналов операций, где велиду дешифратора управления, другиевходы которого соединены с соответствующими входами элемента И и выходами щ разрядов запоминающего блока,выходы 1 разрядов которого подключены к информационным входам первого,"второго, третьего, четвертого элементов И блока переключения, информационные входы пятого и шестого элементов И блока переключения соединеныс выходом буферного регистра, вход 10которого соединен с выходомвторогоэлемента И блока переключения, первый н шестой выходы дешифратора управления подключены соответственно куправляющим входам первого и шестого 15элементов И блока переключения,. Управляющие входы второго, третьего,четвертого и пятого элементов И блока переключения соединены с одноименными выходами дешифратора управления 20и с второй группой входов блока местного управления, выходы четвертогои пятого элементов И блока переключения подключены соответственно кпервому и второму входам элементаИЛИ блока переключения, выход элемента ИЛИ которого подключен к второмувходу распределительного блока, выходы которого соединены с группойвыходов устройства, выходы первогои шестого элементов И блока переключения соединены соответственно спервым и вторым информационными входами регистра адреса, выход третьего элемента И блока переключениясоединен с выходом устройства.На чертеже приведена схема предлагаемого устройства микропрограммного управления,Запоминающий блок 1 связан по .входу с регистром адреса 2, по разрядам и - с первыми входами распределительного блока 3; по разрядамщ - с входами дешифратора управления 4 и элемента И 5, выход которогочерез элемент задержки б подключентакже к входу дешифратора управления 4.Блок переключения 7 содержитэлементы И 8 - 13, а также элементИЛИ 14, входы которого подключенысоответственно к выходам элементовИ 9 и 10, а выход подключен к вторым входам распределительного блока3. Управляющие входы всех элементовИ блока переключения подключены ксоответствующим выходам дешифраторауправления 4. Информационные входыэлементов И 10 - 13 подключены квыходам разрядов 6 запоминающегоблока 1. Информационные входы элементов И 8 и 9 подключены к выходу Юбуферного регистра 15. Выход элементов И 8 подключен к входам старшихразрядов 16 регистра адреса 2,а выходы младших разрядов 17 регистра адреса 2 подключены к выхо ду элемента И 13. Выход элемента И11 подключен к выходу устройства 18,Выход элемента И 12 подключен к вхо"дам буферного регистра 15. Блок местного управления 19 имеет первуюгруппу входов 20 (признаков условийветвления). Блок местного управления19 также подключен к управляющимвходам регистра адреса 2. Запоминающий блок 1 предназначен для храненияи выдачи микрокоманд, регистра адреса 2 - для приема, хранения и вы-.,дачи адреса микрокоманды в запоминающее устройство 1, распределительный блок 3 - для выработки и распределения управляющих сигналов в зависимости от значения разрядов микрокоманды. Элемент 5 и элемент задержки 6 служит для выработки и задержки на один цикл работы устройства сигнала, свидетельствующего о наличии определенного кода на выходахразрядов запоминающего блока 1, блокпереключения 7 - для коммутации засылки разрядов Г микрокоманды либов распределительный блок 3 через элемент ИЛИ 14, либо в старшие разряды 16 регистра адреса микрокоманд2 через элемент И 8, либо в младшиеразряди 17 через элемент И 13, либов буферный регистр 15 через элементИ 12, либо через элемент И 11 на выход 18. Буферный регистр, 15 предназначен для временного хранения разря"довмикрокоманды, блок местногоуправления 19 - для синхронизацииработы узлов устройства. Выход устройства 18 служит для подключения информационных входов операционногоустройства вычислительной машины,либо для связи с управляющими входами устройств, подключаемых к манине с целью увеличения ее функциональных возможностей (арифметического расширителя, дополнительныевнешние устройства и т.д.), В первом случае информация, поступающаяна выход 18, может обрабатыватьсяв текущем или последующих циклахкак операнд, а во втором случае -служит для выработки сигналов,управляющих работой подключенныхустройств,чина М является Функцией количества разрядов и и зависит от способа кодирования этих разрядов. Разряды поступают на входы элементов И 10 13 блока 7, а разряды щ - на входы дешифратора управления 4 и элемента5. Возбуждается один из выходов дешифратора управления 4 и открываетсоответствующий элемент И блока переключения 7. Если открывается элемент И 10, то разряды передаются через 1 Оэлемент ИЛИ 14 на вторые входы блока3 и участвуют в формированииуправляющих сигналов. Таким образом, общее количество вырабатываемых приэтом сигналов определяется мощностьюсуммарного множества микроопераций(МФ(.). Одновременно с этим выход дешиФратора управления 4 открывает элемент И 10, возбуждает лок местногоуправления 19 по одному из соответствующих входов 10Блок местногоуправления 19 вырабатывает сигнал,который поступает на соответствующийвход регистра адреса 2 и увеличиваетего содержимое на единицу, Формируяадрес следующей микрокоманры (естест.венная адресация), Естественная адресация осуществляется также, когдаоткрывается один из элементов И 11,12 и 9 и осуществляется передачаразрядов Я соответственно на внешнюю ЗОинформационную шину 18, на регистр15 или передача содержимого этогорегистра на вторые входы блока 3 через элемент ИЛИ 14,35Если открывается элемент И 13, разряды 6 поступают в младшие разряды 17 регистра адреса микрокоманды 2 под воздействием управляющего сигнала с выхода блока 19, образуя 40 адрес следующей микрокомайды способом принудительной адресации в преде.- лах сегмента микропрограммной памяти, номер которого определяется содержимым старших разрядов 16 регистра 2. Изменение номера сегмента осуществляется засылкой кода из буферного регистра 15 через элемент И; Принудительная адресация в пределах всего объема микропрограммной памяти осуществляется при одновременном открытии элементов И 8 и 13. При этом код в буферный регистр 15 должен быть занесен в одной из предыдущих микрокоманд. В режиме принудительной адресации распределительный блок 3 может вырабатывать управляющие сигна. лы только на выходах М под воздействием разрядов п запоминающего блока 1 (разряды С передаются при этом в качестве кода следующего адреса на 60 регистр адреса 2). Однако при пере- родах внутри сегмента мощность.микрокоманды может не уменьшаться,"так как, если дешифратор управления 4 открывает, одновременно элементом И 13 элемейт И 9,на входы распределительного блока 3 подается содержимое регистра 15, и могут вырабатываться сигналы на всех (М+Е) выходах блока 3. Кроме того, буферный регистра 15 может служить в качестве регистра "косвенного" или "остаточного" управления и, тем самым, позволяет уменьшить объем микропрограммной памяти. В частности; если есть несколько микропрограмм, отличающихся только одной микрокомандой, например, направлением или видом сдвига, выполняемым над операндом, или выполняищих одинаковые операции над содержимым разных регистров 1 сложить с аккумулятором А, сложить с аккумулятором Б н др),. то вид сдвига или номер аккумулятра предварительно заносится из разрядов 6 запоминающего устройства 1 в буФерный регистр 15, а в общей микропрограмме при помощи разрядов в указывается необходимость передачи содержимого регистра 15 через элемент И 9 и элемент ИЛИ 14 на вторые входы блока 3. Характер использования разрядов 2 в текущей микрокоманде, а также содержимого буферного регистра 15 определяется разрядами ю как текущей, так и предыдущей микрокоманд, так как на входы дешифратора управления 4 поступают сигналы не только с выходом разрядов е запоминающего устройства 1, но и с выхода элемента И 5 через элемент задержки 6. Элемент И 5 проверяет наличие в разрядах щ определенного кода (для этого на соответствующие входы элемента И подаются прямые или инверсные значения выходов разрядов в), а элемент задержки 6 задерживает сигнал на выходе элемента И 5 до следующего цикла (,до появления на входах дешифратора управления 4 разрядов е следующей микрокоманде . Таким образом обеспечивается интерпретация последующего кода в разрядах в в зависимости от предыдущего и тем самым уменьшается необходимое количество разрядов в.Условные переходы в предлагаемоМ устройстве реализуются путем модификации адреса микрокоманды блоком местного управления 19 по управляющим входам в соответствии с признаками условий ветвлений, поступающими на группу входов 20.Таким образом, предлагаемое техническое решение позволяет упростить устройство за счет сокращения объема запоминающего блока. Оно внедряется в микро-ЭВМ, выполненной на больших интегральных схемах. Формула изобретенияУстройство микропрограммного управления, содержащее запоминающийблок, регистр адреса, распределительный блок, блок местного управления, элемент задержки, блок переключения, содержащий элемент ИЛИ, шестьэлементов И, причем выходы блокаместного управления подключены к управляющим входам регистра адреса,выход которого подключен ко входузапоминающего блока, первая группавходов блока местного управления подключена к первой группе входов устройства, выходы и , разрядов запоминающего блока подключены к первомувходу, распределительного блока,о т л и ч а ю щ е е с я тем, что,с целью упрощения устройства за 15счет сокращения объема запоминающего блока, в устройство введены деиифратор управления, буферный регистр, элемент И, выход которогоподклвчен через элемент задержки кпервому входу дешифратора управления, другие входы которого соединены с соответствующими входами элемента И и выходами в-разрядов запоминающего блока, выходы 6 - разрядов которого подключены к информационным входам первого, второго,третьего, четвертого элементов Йблока переключения, информационныевходы пятого и шестого элементов Иблока переключения соединены с выходом буферного регистра, вход которого соединен с выходом второгоэлемента И блока переключения,первый и шестой выходы дешифраторауправления подключены соответственно к управляющим входам первого ишестого элементов И блока переключения, управляющие входы второго,третьего, четвертого и пятого элементов И блока переключения соединены содноименными выходами дешифраторауправления и со второй группой вхо-,дов блока местного управления, выходы четвертого и пятого элементовИ блока переключения подключены соответственно к первому и второму входам элемента ИЛИ блока переключения,выход элемента ИЛИ которого подключенко второму входу распределительнбгоблока, выходы которого соединены сгруппой выходов устройства, выходыпервого и шестого элементов И блокапереключения соединены соответственнос первым и вторым информационнымивходами регистра адреса, выход третьего элемента И блока переключениясоединен с выходом устройства.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР9 264783, кл. С 06 Г 9/16.2, Авторское свидетельство СССРР 3217066, кл,б 06 Г 9/16, 22,03.671 прототип).951308 Составитель Т.БондаренкоТехред Т.Маточка Корректор Г.Решетник Редактор К.Волоыук Подписное Заказ 5948/55 Тираж 731ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб., д.4/4/5 Филиал ППП "Патентф, г.ужгород, ул.Проектная,4

СмотретьЗаявка

2355336, 03.05.1976

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УССР, ЛЕНИНГРАДСКОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО ЛЕНИНГРАДСКОГО ОБЪЕДИНЕНИЯ ЭЛЕКТРОННОЙ ПРОМЫШЛЕННОСТИ "СВЕТЛАНА"

ИВАНОВ ВЛАДИМИР АНДРЕЕВИЧ, ДРЯПАК АНАТОЛИЙ ФЕДОРОВИЧ, ПАЛАГИН АЛЕКСАНДР ВАСИЛЬЕВИЧ, СЫРОВ ВИКТОР ВАЛЕНТИНОВИЧ, ГИЛЯРОВСКАЯ ЕВГЕНИЯ БОРИСОВНА

МПК / Метки

МПК: G06F 9/46

Метки: микропрограммного

Опубликовано: 15.08.1982

Код ссылки

<a href="https://patents.su/5-951308-ustrojjstvo-dlya-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для управления подпрограммами

Случайный патент: Состав порошковой проволоки для наплавки