Оперативное запоминающее устройство типа 2д с обнаружением и исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

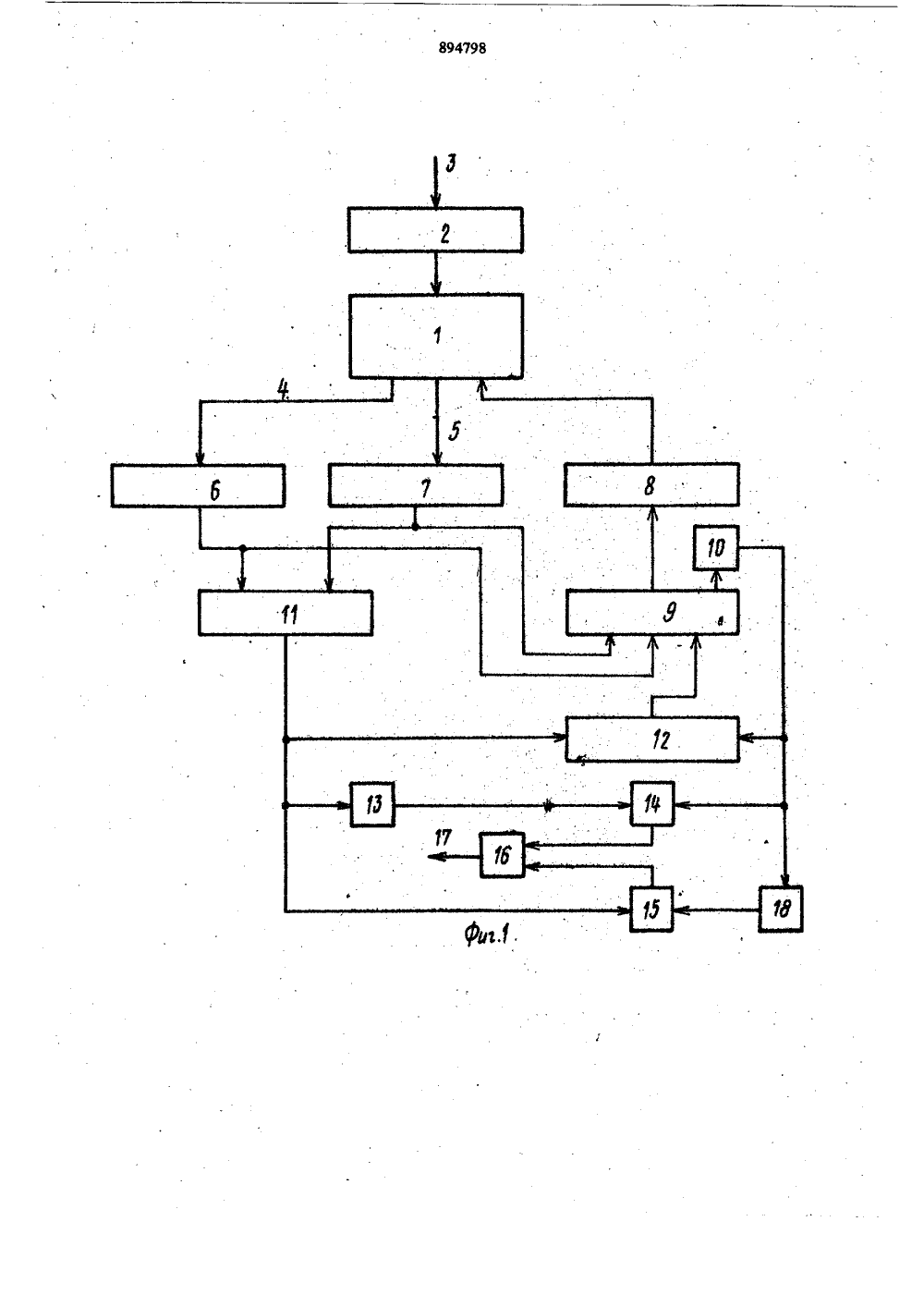

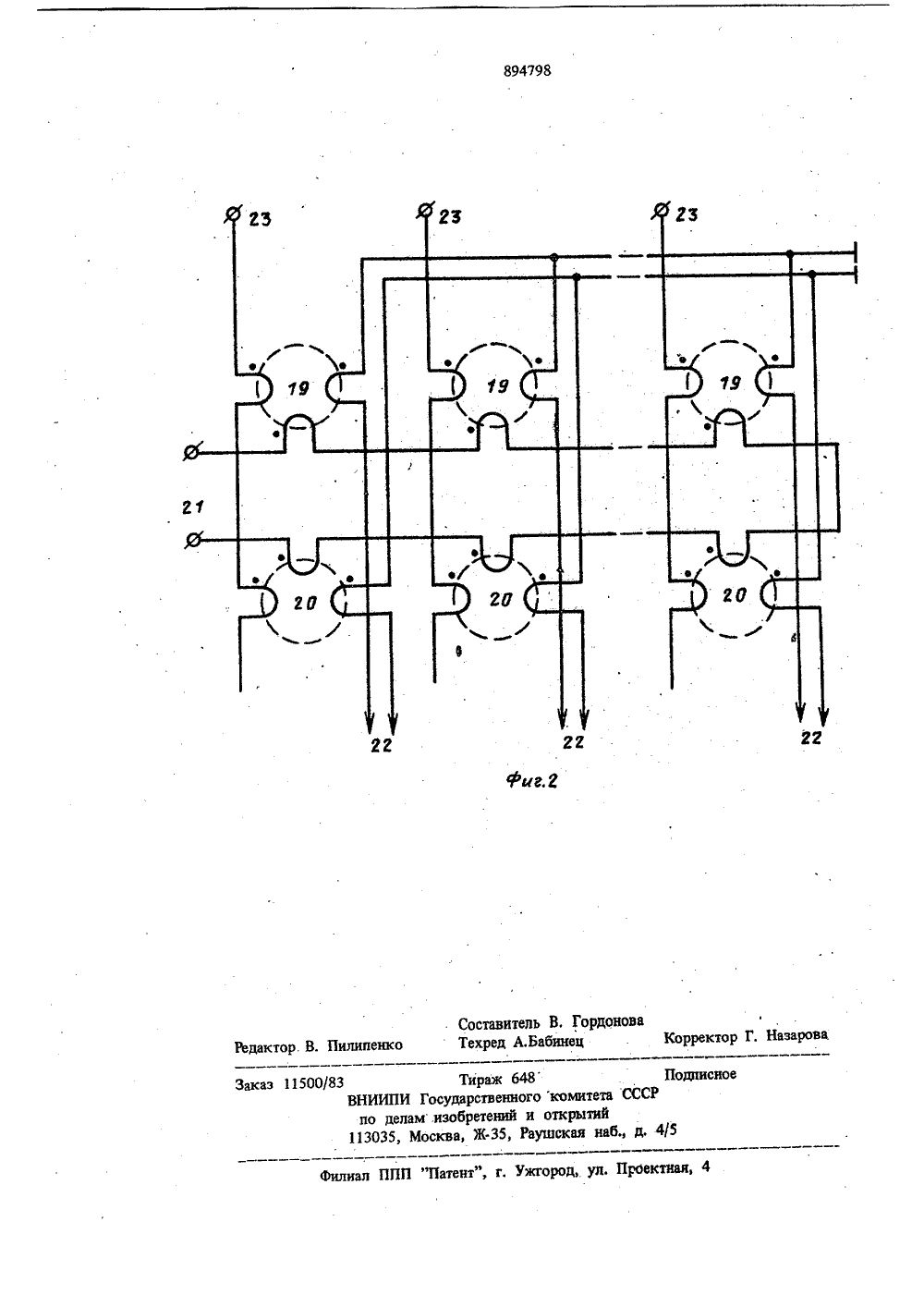

1) Заявител уворова академия им, Ф.Э, Дзержинского ЗАПОМИНАНИИЕЕ УСТРОЙСТВОНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМОШИБОК 4) ОПЕРАТИВН ТИНА 2 Д Совышение быстродейыхо пер Изобретение относится к запоминающим ванне записанной в предыдущем цикле инфорустройствам. мации, а также невозможность исправлятьИзвестно оперативное запоминающее устрой. ошибки, если выполняется только считываниество, содержащее накопитель, блоки выбора из накопителя,адреса, усилители считывания, блоки контро- Цель изобретения - иля 13. ствня устройства,, Недостатками устройства являются большие Поставленная цель достигается тем, чтоаппаратурные затраты и низкое быстродействие. в оперативное запоминающее устройство типаНаиболее близким по технической сущное Д с обнаружением и исправлением ошибок,ти к предлагаемому является оперативное за- содержащее накопитель, входы которого соедипоминающее устройство с обнаружением и ис О иены соответственно с выходами формирова.правлением ошибок, содержащее накопитель, телей тока записи и дешифратора адреса, вхо.входы которого соединены соответственно с ды которого являются входами устройства,выходами дешифратора адреса и формврова. первую группу усилителей считывания, входытеней тока записи, первую группу усилителей которых подключены к одним иэ выходов насчитывания, регистр числа, счетные входы ко-копителя, группу элементов И, регистр числа,торого подключены к выходам группы злемен счетные входы которого подключены к выхотов И, а выходы - к входам формировате- дам элементов И группы, а выходы - соот.лей тока записи, блок контроля, и д кото- ветственно ко входам формирователей токарого подключен к первому входу. вого эле- записи и блока контроля, выход которого сомента И г. единеи с первым входом первогоэлемента ИНедостатками устройства являются низкое и управляющими входами элементов И, групбыстродействие вследствие того, что для ис- пы, введены группа. элементов ЭКВИВАЛЕК 1 правления ошибки требуется проводить считы НОСТЬ, элемент И-НЕ; второй элемент И, эле8947984 1 О 15 20 мент ИЛИ, элемент НЕ и вторая группа усилителей считьвания, входы которых подклю.Чены к другим выходам накопителя, а выхо.ды соединены соответственно с информационными входами регистра числа и входами элементов ЭКВИВАЛЕНТНОСТЬ группы, выходыкоторых подключены ко входу элемента И НЕ,первому входу второго элемента И и к нформационным входам элементов И группы,выход элемента И-НЕ подключен ко второмувходу первого, элемента И, выход которогосоединен с первым входом элемента ИЛИ,второй вход которого подключен к выходувторого элемента И, а выход является конт.рольным выходом устройства, второй входвторого элемента И соединен с выходом эле.мента НЕ, вход которого подключен к выходу блока контроля.При этом накопитель целесообразно выполнйть-из числовых линеек на магнитных сердечниках, прошитых числовыми обмотками, разрядными обмотками считывания и записи, при.чем одноименные разрядные обмотки считывания, проходящие соответственно через рабочиеи стабилизирующие магнитные сердечники числовых линеек накопителя, соединены носледо.вательно и подключены соответственно к вы.ходам накопителя,На фиг. 1 изображена структурная схемапредлагаемого устройства; на фиг. 2 - прин.ципиальная схема. числовой линейки накопителя.устройство содержит накопитель 1, дешифратор 2 адреса со входами 3.Устройство содержит первую 6 и вторую 7группы усилителей, формирователи 8 тока записи, регистр 9 числа, блок 10 контроля,группу элементов ЭКВИВАЛЕНТНОСТЬ 11,группу элементов И 12, элемент И-НЕ 13,первый 14 и второй 15 элементы И, элементИЛИ 16 с выходом 17 и элемент НЕ 18.Входы накопителя 1 соединены соответственно с выходами формирователей 8 тока за.писи и дешифратора 2 адреса, входы 3 кото.рого являются входами устройства. Входы усилителей первой б и второй 7 групп подклю.чены соответственно к одним 4 и другим 5выходам накопителя 1, Счетные входы регист.ра 9 числа соединены с выходами элементовИ группы 12, а выходы - соответственно совходами формирователей 8 тока записи и блока 10 контроля, выход которого подключенк первому входу первого элемента И 14 иуправляющим входам элементов И группы 12.Выходы усилителей считывания первой б ивторой 7 групп соединены соответственно с ин.формационными входами регистра 9 числа ивходами элементов ЭКВИВАЛЕНТНОСТЬ группы 11, выходы которых подключены ко входу элемента И-НЕ 13, первому входу второго элемента И 15 и информационным входамэлементов И группы 12. Выход элементаИ. НЕ 13 подключен ко второму входу первого элемента И 14, выход которого соединен с первым входом элемента ИЛИ 16, второй входкоторого подключен к выходу второго эле.мента И 15, а выход 17 является контрольнымвыходом устройства. Второй вход второго элемента И, 15 соединен с выходом элементаНЕ 18, вход которого подключен к выходу бло.ка 10 контроля,При этом накопитель 1 выполнен из число.вых линеек на магнитных сердечниках 19 и 20,прошитых числовыми обмотками 21, разрядными обмотками 22 считывания и записи 23, причем одноименные разрядные обмотки 22 счи. тывания, проходящие соответственно через рабочие 19 и стабилизирующие 20 магнитные сер дечники числовых.линеек накопителя 1, соеди. иены последовательно и подключены соответственно к выходам 4 и 5 накопителя 1.Блок 10 контроля может быть построенлюбым из известных методов например, приконтроле по модулю два блок 10 контролябудет фиксировать факт ошибки в нечетномчисле разрядов.Устройство работает следующим образом.Неисправность, возникшая в одном илинескольких разрядах накопителя 1 обиаружи.вается при считывании информации, причемфакт ее возникновения регистрируется блоком10 контроля, а место - элементами ЭКВИВАЛЕНТНОСТИ группы 11. При наличии управ.ляющего сигнала на выходе блока контроляпроизводится исправление всех ошибок путем 35инвертирования тех разрядов регистра числа,в которых бьша зафиксирована ошибка. Адрес,по которому необходимо произвести считывание числа дешифрируется дешифратором 2,в результате чего выбирается числовая линейка, 40иответствующая ячейке памяти накопителя 1,из которой необходимо считать информацию,В разрядных обмотках 22 считывания рабочихсердечников 19 и стабилизирующих сердечни.ков 20 соответственно иидуктируются ЭДС, 45соответствующие кодам "1" и "0", Эти сигна.лы, усиленные соответственно усилителямисчитывания первой 6 и второй 7 групп посту.лают одновременно на информационные входысоответствующих разрядов регистра 9 числаи на входы элементов ЭКВИВАЛЕНТНОСТИгруппы 11.Процесс исправления ошибок при считы.ванин информации осуществляется следующимобразом.При возникновении ошибки на выходеблока 10 контроля появляется сигнал сбоя,который поступает на управляющие входы элементов И группы 12, что позволяет выдать5 8сигнал на исправление ошибки, который фор .мируется элементами ЭКВИВАЛЕНТНОСТИгруппы 11 соответственно в трех разрядах,где произошла ошибка, и подается га информационные входы элементов И группы 12.Сигивл исправления, ошибки поступает насчетный вход того разряда регистра числа 9,где, произошла ошибка, и инвертирует записанную в нем информацию.. В случае, если блок 10 контроля обнаруживает ошибку и сигнал об этом поступаетна первый вход первого элемента И 14, а на, выходах элементов ЭКВИВАЛЕНТНОСТИ группы 1 сигналов нет, тогда на выходе элемен.та И-НЕ 13 возникает сигнал, который поступает на второй вход первого элемента И 14.Сигнал с выхода первого элемента И 14 поступает на первый вход элемента ИЛИ 16 ина его выходе 17 появляется сигнал ирерывания, свидетельствующий о том, что обнаружена неисправляемая ошибка, Аналогичныйсигнал будет выдан и в том случае, если блок10 контроля ошибки не обнаружит, тогда навыходе элемента НЕ 18 появится сигнал, иоступа-ющий на второй вход второго элемента И 15 и накаком-либо выходе элементов ЭКВИВАЛЕНТНОСТИ группы 11,будет сигнал, который иройдет через первый вход второго элемента И 15на его выход и поступит на второй вход злемента ИЛИ 16.КОличество обнаруживаемых и исправляемых ошибок в предлагаемом устройстве зависит только от типа блока 10 контроля, причем время исправления ошибок не зависит отих количества и практически не увеличивает. время цикла обращения к оперативному за.поминающему устройству,Технико-экономическое преимущество предлагаемого устройства заключается в том, чтооно, позволяет увеличить быстродействие почтивдвое по сравнению с известным. 94798 бадреса, входы которого являются входами. устройства, первую группу усилителей считывания, входы которых подключены к одним из выходов накопителя, группу элементов И, регистр числа, счетные входы которого иодключены к выходам элементов И группы, а выходы - соответственно ко входам формирователей тока записи и блока контроля, выход которого соединен с первым входом 10 первого элемента И и управляющими входамиэлементов И группы, о т л и ч а ю щ е ес я .тем, что, с целью повышения быстродействия устройства, оно содержит группу элементов ЭКВИВАЛЕНТНОСТЬ, элемент И-НЕ, 1 з второй элемент И, элемент ИЛИ, элемент НЕи вторую группу усилителей сяпьвавия, вхо.ды которых подключены к другим выходам накопителя, а выходы усилителей считывания соединены соответственно с информационными щ входами регистра числа и входами элементовЭКВИВАЛЕНТНОСТЬ группы, вирды которых подключены ко входу элемента И-НЕ, первому входу второго элемента И и к информационным входам элементов И группы, выход элеэа мента И.НЕ подключен ко второму входу пер.ного элемента И, выход которого аждинен спервым входом элемента ИЛИ, второй входкоторого подключен к выходу второго элемен.та И, а выход является контрольным выходом чв устройства, второй вход второго элемента Исоединен с выходом элемента НЕ, вход которого подключен к выходу. блока контроля,Формула изобретения43 1. Оперативное запоминающее устройство типа 2 Д с обнаружением и исправлением ошибок, содержащее накопитель, входы которого соединены соответственно с выходамиформирователей тока записи и дешифратора 2, Устгэйство по п, 1, о т л и ч а ю.35щ е е с я тем, что накопитель выполнен изчисловых линеек на магнитных сердечниках,прошитых числовыми обмотками, .разряднымнобмотками считывания н записи, причем од- .ноименные разрядные обмопси считывания,4, проходящие соответственно через рабочие истабилизирующие магнитные сердечники накопителя, соединены последовательно и подключены соответственно к выходам накопителя.Источники информации,принятые во внимание при экспертизе1. Путинцев Н, Д, Аппаратный контроляуправляющих цифровых вычислительных ма.шнн. М "Советское радио", 1966, с. 286.2, Авторское свидетельство СССР У 6232388,кл, 6 11 С 2900, 1978 (прототип),894798 2 г,2 Составитель В, Г Техред А.Бабинец ва Корректор Редактор. В. Пилиненк арова Тираж 648 ПодписноНИИПИ Государственного комитета СССРпо делам .изобретений и открытий13035, Москва, Ж.35, Раушская набд, 4/5 аказ 11500 л ППП "Патент", г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

2904419, 04.04.1980

ВОЕННАЯ ОРДЕНОВ ЛЕНИНА, ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ И СУВОРОВА АКАДЕМИЯ ИМ. Ф. Э. ДЗЕРЖИНСКОГО

ТАФИНЦЕВ ВЛАДИМИР АЛЕКСАНДРОВИЧ, БРЯНЦЕВ НИКОЛАЙ МИХАЙЛОВИЧ, ГАЙДУКОВ ВЛАДИМИР ЛЬВОВИЧ, ТИТОВ ВИКТОР АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, обнаружением, оперативное, ошибок, типа

Опубликовано: 30.12.1981

Код ссылки

<a href="https://patents.su/5-894798-operativnoe-zapominayushhee-ustrojjstvo-tipa-2d-s-obnaruzheniem-i-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Оперативное запоминающее устройство типа 2д с обнаружением и исправлением ошибок</a>

Предыдущий патент: Запоминающее устройство с автономным контролем

Следующий патент: Устройство для контроля блоков памяти

Случайный патент: Бесконтактное реле времени