Мажоритарный декодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

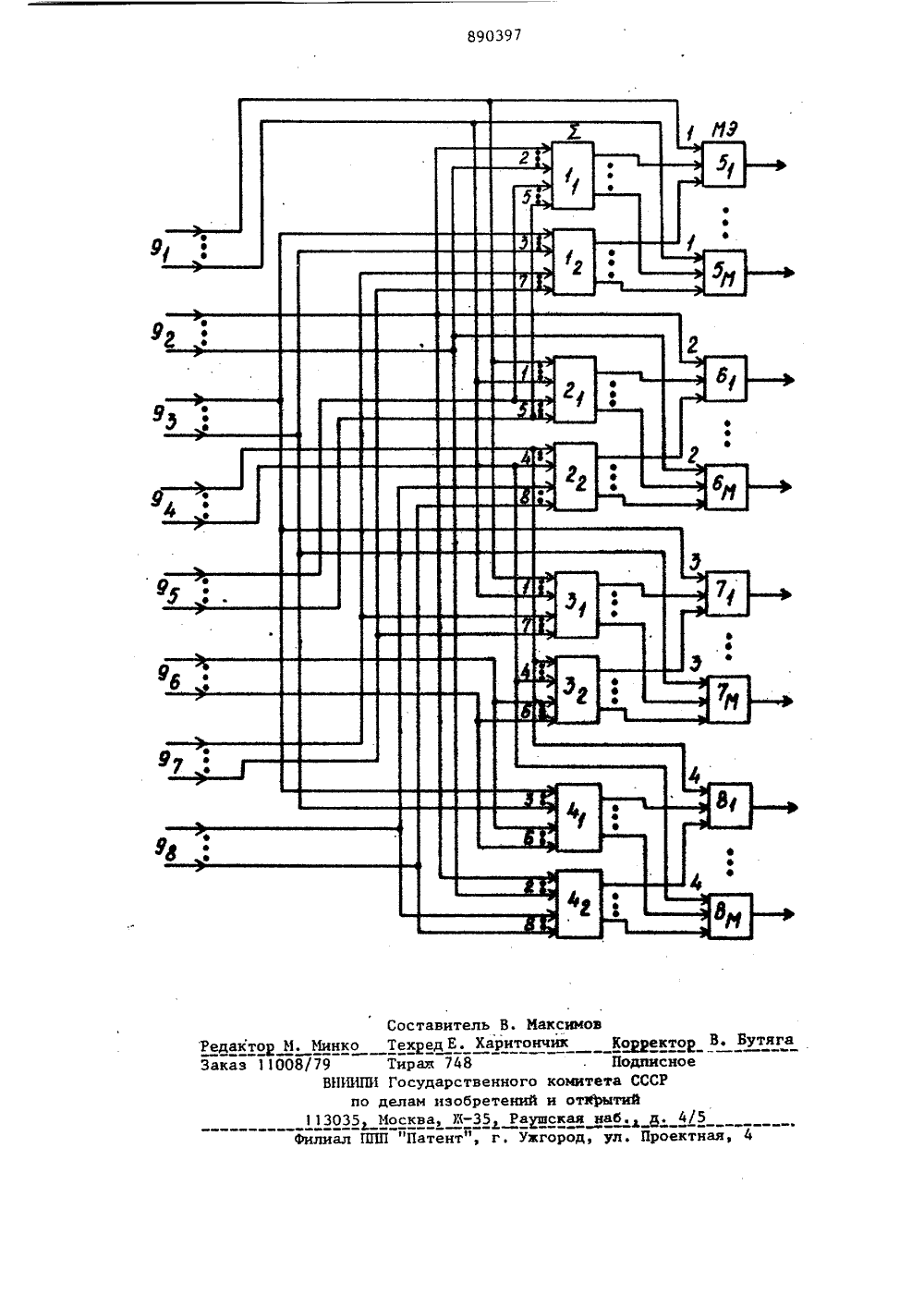

Союз СоветсннкСоцналнстичесникРеспублик ОРСК О МУ СВИДЕТЕЛЬСТ К(23)Приоритет ударстиевй квмвтв СССР кзабувтвик) МАЖОРИТАРНЫЙ ДЕКОДЕ енпредставле- основанием ройстшибки стно декодирующее ус ляыщее произвольные.о ошибок кратности М в ах, содержащие сдвиг с обратными связями, огическими блокамиИэв нсправ пакеты ких ко гистры ные с разрядов х позици нню группы расположен ях, которы Р-ичный ра 3 М ) 2 смежнь гх на определе цикличесющие ресоединенься ка2 могут рассматряд слова, где Изобретение относится к цифровой вычислительной технике и передаче информации и может быть использовано в ЦВМ, в которых информация передается, хранится или обрабатывается в коррек сирующем коде, а также в многока- ф нальных системах передачи инФормации.В таких системах возникает необходимость исправления кратных ошибок в определенных группах смежных разрядов. Например, для запоминающих устройств ЦВМ разработано много типов полупроводниковых интегральных схем, содержащих в одном корпусе оборудование для хранения нескольких 2-8 разрядов большого количества слов. Существуют15 и другие многоразрядные интегральные схемы ЦВМ, например четырехраэрядный арнфметико-логический блок, Отказ одной из таких схем приведет к искажеАналогичная ситуация может возникнутьв многоканальных системах передачи Йформации, где в каждый момент времени по нескольким каналам передаютсянесколько смежных разрядов слова. Этиразряды могут быть искажены импульсной помехой, одновременно воздействующей на все каналы, на приемное или передающее устройство. Для восстановдения информации в таких ситуациях должны быть использованы корректирующиекоды и соответствующие декодирующиеустройства, обеспечивающие исправление пакетов из И ошибок в определных смежных позициях информационногослова, соответствукщих егонню в системе счисления с890397 Недостаток данного устройства заключается в большом времени декодирования из-за последовательного характера процесса.Известно также декодирующее устройство, исправляющее ошибки в Р-ичном разряде слова, представленном группой из М смежных двоичных разрядов, содержащее сдвигающие регистры, соединенные с логическими блоками 23.Недостаток известного устройства заключается также в большом времени декодирования,Наиболееблизким по техническойсущности и достигаемым результатам кпредлагаемому является мажоритарныйдекодер, содержащий мажоритарные элементы, выход каждого из которых подключен к выходной шине соответствующего разряда, а также г М сумматоровио модулю 2, где г (2 М+1), где К -число информационных разрядов слова,причем каждый мажоритарный элементимеет г входов, каждый из которыхподключен к выходам соответствующихсупчаторов по модулю 2 33.Недостаток известного устройствазаключается в его сложности из-забольшого числа сумматоров по модулю 2н сложности мажоритарных элементовс большим числом входов (не мене 2 М++1),Цель изобретения - упрощение декодера, в частности, для случая использования 8 М 4 М) корректирующего35кода, построенного на основе 8,4мажоритарно декодируемого корректирующего кода с кодовым расстоянием 3,где 8 М - общее число разрядов кода:4 М - число информационных разрядов40за счет уменьшения числа сумматоровв пересчете на один разряд) и уменьше ня числа входов мажоритарных элементов при сохранении их количества.Для достижения укаэанной цели45мажоритарный декодер, содержащии четыре группы по М мажоритарных элементов, выход каждого из которых подключен к выходу соответствующего двоичного информационного разряда декодера, где М - число смежных двоичных 50разрядов, рассматриваемых как Р-ичный разряд слова, Р = 2 , содержитМчетыре группы по два М-разрядных арифметических сумматора в каждой, первыевходы первого и второго сумматора в 55первой группе подключены соответственно к второй и третьей М-разрядной,групппе входов декодера, во второй 4группе - к первой и четвертой группе входов декодера, в третьей группе к первой и четвертой группе входов декодера, а в четвертой группе - к третьей и второй группе входов декодера, вторые входы М-разрядных арифметических сумматоров в первой группе подключены соответственно к пятой и седьмой группе входов, во второй группе - к пятой и восьмой группе входов, в третьей группе - к седьмой и шестой группе входов, а в четвертой группе - к шестой и восьмой группе входов декодера, причем первые входы каждого из М мажоритарных элементов каждой группы подключены к одноименной группе входов декодера, а вторые и третьи входы - к соответствующим выходам первого и второго М-разрядных арифметических сумматоров одноименной группы.Входной (8 М, 4 М) корректирующий код для устройство формируется по следующим правилам.Исходное двоичное 4 М-разрядное слово разбивается на четыре группы по М смежных разрядов в каждой, и каждая такая группа рассматриваетя как один Р-ичный разряд, где Р = 2 . Затем формируется корректирующий код, аналогичный известному двоичному разделимому мажоритарно декодируемому коду 8,4) описанному в Г 33, только вместо двоичных разрядов используются Р-ичные разряды, а вместо операции сложения по модулю 2 - операция арифметического сложения на М-разрядном арифметическом сумматоре с потерей переноса иэ старшего разряда, т.е. по модулю Р = 2 . Если Р-ичныеМинформационные символы обозначить а, Ь, с, д, то символы корректирующего кода А, В, С, О, Е, Г, С, Н формируют по следующим соотношениям: А = а ВЬ; Сс; О = д; ЕаЬ; Г=С+д; С=а+с; Н Ь+с 1, причем "+" означает операцию сложения по модулю Р. Например, двоичный код 10011101 при необходимости исправления ошибки, заключающейся в искаже- . нии пары смежных разрядов (первого и второго, третьего и четвертого и т.д.) рассматривается как код 2131 в системе счисления с основанием Р = 2 = 4(а = 2, Ь.= 1, с . 3, д1). Иэ этого кода по указанным соотношениямформируется код 21313012, которыйпредставляется двоичным кодом10011101000110.ключен к выходу соответствующего двоичного инФормационного разряда декодера, где М - число смежных двоичных разрядов, рассматриваемых как Р-ичныймразряд слова, Р = 2 , о т л и ч а - ю щ и й с я тем, что, с целью упрощения декодера, он содержит четыре группы по два М-разрядных ариФметических сумматора в каждой, первые входы первого и второго сумматора в О первой группе подключены соответственно к второй и третьей И-разрядной группе входов декодера, во второй группе - к первой и четвертой группе входов декодера, в третьей группе - к 15 первой,и четвертой группе входов декодера, а в четвертой группе - к третьей и второй группе входов декодера, вторые входы М-разрядных арифметических сумматоров в первой группе щ подключены соответственно к пятой и седьмой группе входов, во второй группе - к пятой и восьмой группевходов, в третьей группе - к седьмойи шестой группе входов, а в четвертой группе - к шестой и восьмой группе входов декодера, причем первыевходы каждого из М-мажоритарных элементов каждой группы подключены к одноименной группе входов декодера, авторые и третьи входы " к соответствующим выходам первого и второгоИ-разрядных ариФметических сумматороводноименной группы.Источники инФормации,принятые во внимание при экспертизе1. Авторское свидетельство СССРУ 362302, кл.06 Р 1.1/12, 1971.Составитель В. МаксимРедактор И. Иинко Техвед Е. Харитончик Корректор В. Бутяг Подписноета СССР 4/5 лиал ППП "Патент", г. Ужгород, ул. Проектная,з 11008/79 ВНИИПО по 113035

СмотретьЗаявка

2888568, 26.02.1980

ПРЕДПРИЯТИЕ ПЯ Г-4677, ВОЕННАЯ ОРДЕНОВ ЛЕНИНА, ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ И СУВОРОВА АКАД. ИМ. Ф. Э. ДЗЕРЖИНСКОГО

ЕЩИН КОНСТАНТИН КОНСТАНТИНОВИЧ, ЗАВОЛОКИН АНАТОЛИЙ КУЗЬМИЧ, ЗАРОВСКИЙ ВИТАЛИЙ ИВАНОВИЧ, МОШКОВ АЛЕКСЕЙ АЛЕКСЕЕВИЧ, МУСАТОВ ИГОРЬ ФЕДОРОВИЧ, РЕЙНЕР ВАЛЕНСИЯ ИВАНОВНА, ЮФЕРОВА ЕВГЕНИЯ КИРИЛЛОВНА

МПК / Метки

МПК: H03M 13/43

Метки: декодер, мажоритарный

Опубликовано: 15.12.1981

Код ссылки

<a href="https://patents.su/5-890397-mazhoritarnyjj-dekoder.html" target="_blank" rel="follow" title="База патентов СССР">Мажоритарный декодер</a>

Предыдущий патент: Логический анализатор

Следующий патент: Устройство для контроля логических узлов

Случайный патент: Устройство для дуговой сварки с поперечными колебаниями горелки