Логическое запоминающее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

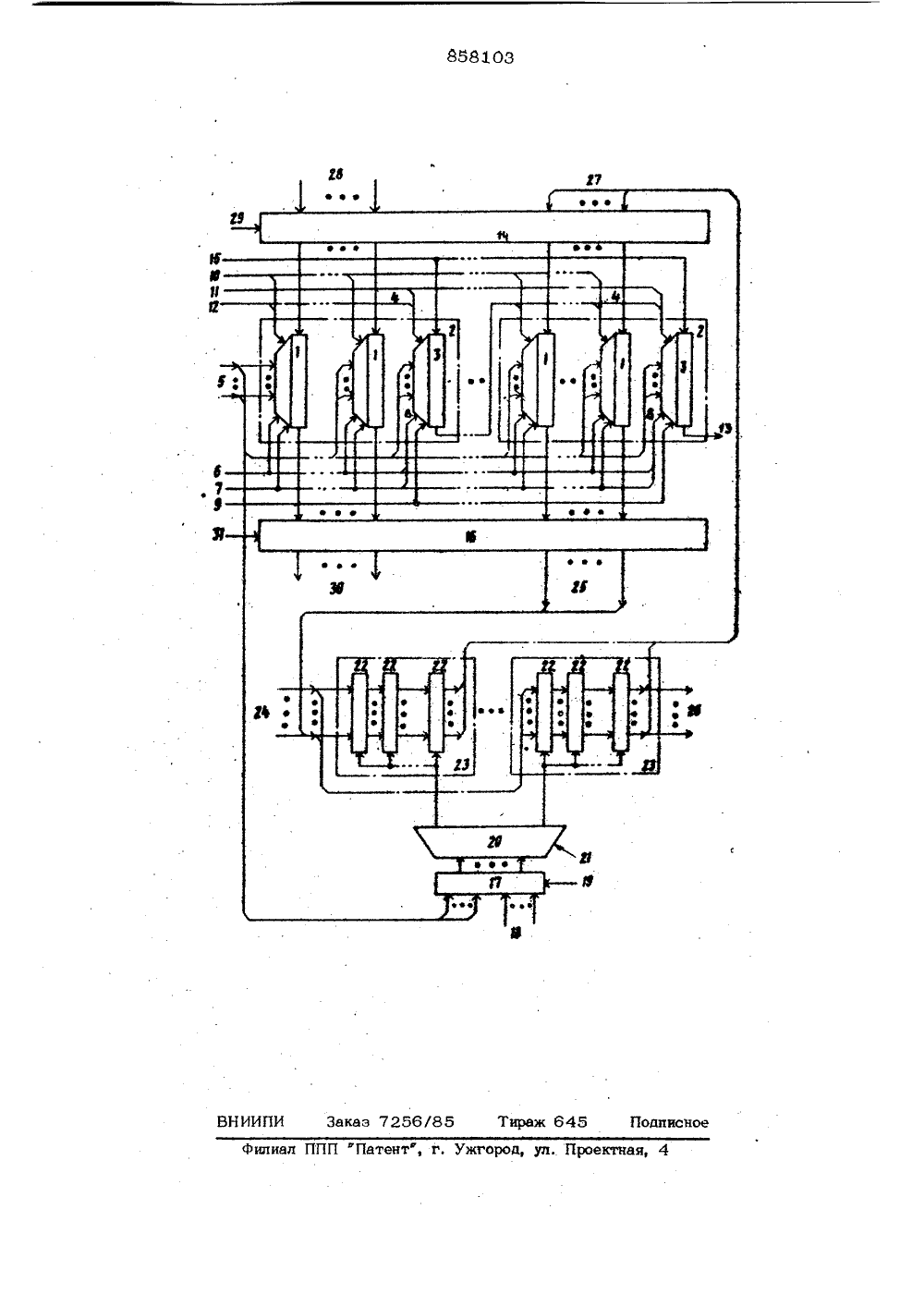

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Соеэ СоветскихСоциалистическихРеспублик и 858103по делам изобретении и открытий(53) УДК 681,327. ,66 (088,8) Дата опубликевания описания 26.08,81 72) Авторы изобретеии) Заявител мский политический инс 54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО Недостаявляется ниэ ленное отсутс щения процес дачи н обраб Изобретение относится к области вычислительной техники н может быть использовано при построении устройств хранения и переработки дискретной информацииПо основному авт. св, Ль 649037 известно логическое запоминающее устройство, содержащее группы одноразрядных блоков памяти, управляющие блохи памяти и шины группового стробирования по числу групп одноразрядных блоков памяти, подключенные к стробируюшим входам одноразрядных блоков памяти и к стробирующему входу управляющего блока памяти соответствующей групйы, шину общего стробировання, . соединенную со стробируюшими входами одноразрядных блоков памяти, информационные входы и выходы которых соединены соответственно с выходами входного и со входами выходного регистров, управляющую шину стробирования, подключеннуо к стробируюшим входам управляющих блоков памяти, шину ввода константы и шину индикации, соединенные соответственно о информационными входа ми управляющих блоков памяти и с информационным выходом управляюще.о блоха намятп последней группы, шину признака группового стробирования, подключенную к шине группового стробнрования первой груп- пы блоков памяти, первые адресные шины и шину записи, соединенные соответственно с адресными входами и со входами записи всех одноразрядных и управляюших блоков памяти, шину считывания, подключенную ко 10 входам счичъщания одноразрядных блоковпамяти и ко входам записи управляющих блоков памяти, шину опроса, соединенную со входами считывания управляющих блоков памяти, инФормационные выходы каждого иэ которых, кроме последнего, подключены к шине группового стробирования последующей группы ком известного устройства кое быстродействие, обуслов твием возможности совмесов приема, буфериэации, в отки нобормацин.3 8581Пель изобретения - повышение быстродействия логического запоминающего устройствафПоставленная цель достигается тем,что устройство содержит переключательадресных щин, дешифратор адреса и блокипамяти магазинного типа по числу адресов одноразрядных блоков памяти, первыеи вторые адресные входы переключателяадресных щин подключены соответственно 10к первым и вторым адресным шинам устройства, управляющий вход и выходы - соответственно к шине выбора адреса и ковходам дешифратора адреса, управляющийвход которого соединен с шиной управления дешифратором, каждый выход дещифротора адреса подключен к управляющимвходам регистров соответствующего блока памяти магазинного типа, информационные входы первьж и информационныеговыходы последних регистров каждого блока памяти магазинного типа подключенысоответственно к выходам выдачи словавыходного и ко входам приема словавходного регистров. . 25На чертеже приведена сХема предложенного устройства,Устройство содержит одноразрядныеблоки 1 памяти, объединенные в группы 2,каждая иэ которых содержит управляющий зоблок 3 памяти, шину 4 группового стробирования. Адресные входы блоков 1 и 3памяти подключены к первым адреснымшинам 5, Входы записи и считыванияблоков 1 памяти соединены с одноименными шинами записи 6 и считывания 7, авход 8 записи блоков 3 памяти подключенкак к вине 6 записи, так и к шине 7считывания. Входы 8 считывания всехблоков памяти соединены с шиной 9 опро са. Стробирующие входы блоков 1 памятикаждой иэ групп 2 подключены к шине 10общего стробирования, а стробирующийвход каждого блока 3 памяти соединенс соответствующей шиной 4 группового 45стробирования и с управляющей шиной11 стробирования. Шина 4 групповогостробирования первой группы 2 подключена к шине 12 признака группового стробирования, а информацИонный выход бло ока 3 памяти последней группы 2 соединенс шиной 13 индикации.Информационные входы блоков 1 памяти подключены к информационным выходам входного регистра 14, информационные входы блоков 3 памяти - к шине 15ввода константы, а информационные выходы блоков 1 памяти соединены с информационными входами выходногорегистра 16. 03 4В состав устройства входит также переключатель 17 адресных шин, подключенный к первым 5, ко вторым 18 адресным шинам и к шине 19 выбора адреса.Выходы переключателя адресных щин соединены со входами дешифратора 20 адреса, управляющий вход которого подключен к шине 21 управления дешифратором, а выходы - к управляющим входам регистров 22 соответствующего блока 23 памяти магазинного типа. Информационные входы всех, кроме первых регистров 22 блоков 23 памяти магазинного типа, соединены с информационными выходами предыдущих регистров. Информационные входы первых регистров 22 блоков 23 памяти подключены к шинам 24 приема слова и к выходам 25 выдачи слова выходного регистра 16. Информационные выходы последних регистров 22 блоков 23 памяти подключены к шинам 26 выдачи слова и ко входам 27 приема слова входного регистра 14, Входы приема байта и управляющий вход входного регистра 14 соединены с шинами 28 приема байта и с управляющей шиной 29 байтового приема соответственно. Выходы выдачи байта и управляющий вход выходного регистра 16 подключены соответственно к шинам 30 выдачи байта и к управляющей шине 31 байтовой выдачи.Считаем, что до начала работы во всех ячейках блоков 3 памяти записаны нули. Выполнение операций записи или считывания в блоках 1 и 3 памяти прстисходит только в том случае, если они находятся в активном состоянии. Переход каждого из блоков 1 и 3 в активное состояние осуществляется по сигналу, поступающему на стробирующий вход этих блоков. После выполнения операций записи или считывания блоки 1 и 3 памяти переходят в пассивное состояние. Регистры 22 блоков 23 памяти при низком уровне напряжения на их управляющих входах находятся в состоянии выдачи информации, а при высоком уровне напряжения - в состоянии приема информации, .причем, время сохранения информации на выходах регистров 22 при смене уровня напряжения на их управляющих входах с низкого на высокий больше времени записи входной информации.В каждой числовой линейке одноразрядных блоков 1 памяти операции приема или выдачи байта возможны в тех байтовых группах 2, в соответствую 1 цих ячейках которых управляющих блоков 3 па03 блинейке одноразрядных блоков 1 памятисформировано,Тогда в четвертом такте данного режима стробирующие входы всех одноразрядных блоков 1 памяти по шине общегостробирования поступает сигнал, активизирующий в них ячейки памяти выбраннойчисловой линейки. В этом же такте посигналу на шине 19 выбора адре"а иереключателя 17 адресных шин на входыдешифратора 20 вдреса поступает кодадреса с первых адресных шин 5.В пятом такте на шину 21 управлениядешифратором 20 поступает сигнал, покоторому на одном из его выходов появляется сигнал, активизирующий блок 23памяти магазинного типа, соответствующийвыбранной в одноразрядных блоках 1 памяти числовой линейке. В этом же тактепо сигналу на шине 7 считывания полноформатное информационное слово черезвыходной регистр 16 поступает нв информационные входы первого регистра 22выбранного блока 23 памяти магазинноготипа. В этом же такте по сигналу, поступающему с выхода деширатора 20адреса на управляющие входы регистров22, происходит сдвиг информации в направлении от первого регистра к последнему. При этом сформированное в данномрежиме полноформатное слово записываетсяв первый регистр, содержйчое первогорегистра переписывается во второй регистр второго - в третий и т.д. Информацияс последнего регистра 22 поступает нашины 26 выдачи слова. На этом режимформирования слова заканчивается.В режиме расформирования словаустройство работает следующим образом.В первом такте по сигналам нв шине19 выбора адреса и шине 21 управлениядешифратором на одном из выходов дешфратора 20 появляется сигнал, соответс 1 вующий коду адреса на первых адресныхшинах 5, по которому осуществляетсясдвиг информации в выбранном блоке 23памяти магазинного типа. При этом информмационное слово иэ последнего регистра22 переписывается во входной регистр 14,В этом же такте на шину 10 общегостробирования поступает сигнал, активизирующий одноразрядные блоки 1 памяти.Во втором такте по сигналу на шине6 записи полноформатное слово из входного регистра 14 переписывается в соответствующуюкоду адреса на первыхадресных шинах 5 числовую линейку одноазрядных блоков 1 памяти. 5 8581мяти записан признак обработки байта,например логическая единица. Организуяпоследовательную перезапись единицы иэодной ячейки памяти блоков 3 памяти вдругую в какой-лЖо числовой линейкеможно управлять выдачей или записьюпоследовательно следующих байтов ин .формации, что эквивалентно расформированию на бай 1 ы или формированию из байтовполноформатного информационного слов а. 10Предложенное устройство имеет четырережима работы: режим формирования слова,режим расформирования слова, режим приема слова и режим выдачи слова. Каждыйиз первых двух режимов может быть совмещен во времени с последними двумяр ежимами.В режиме формирования слова устройство работает следующим образом,В первом такте на шину 12 признака 20группового стробирования поступает ситнал, активизирующий числовую линейку вблоках 1 и 3 памяти группы 2, соответствующую коду адреса, присутствующемуна первых адресных шинах 5. В этом же 2такте по сигналу на управляющей шине29 байтового приема записывается байтинформации, присутствующий на шинах28 байтового приема, в соответствующиеинформационным входам каждой группы 2 ЭОразряды входного регистра 14.Во втором такте по сигналу на шине6 записи осуществляется запись байтаинформации из входного регистра в ячейки одноразрядных блоков памяти первой 35группы 2, соответствующие коду адресанв первых адресных шинах 5. Одновременно в той же числовой линейке производится запись логической единицы в ячейкууправляющего блока 3 памяти, поступаю- ф 0щей на его информационный вход с шиныввода константы.В третьем такте по сигналам науправляющей шине 11 стробирования ишине 9 опроса осуществляется опрос содержимого управляющих блоков 3 памяти.Считывание информации из управляющихблоков 3 памяти при этом производитсяс разрушением. Считанный сигнал поступает на шину 4 группового счробирования 50последующей группы 2 блоков памяти.В дальнейшем в режиме формированияслова данные три такта повторяются призаписи очередного байта информации дотех пор, пока после очередного третьеготакта на шине 13 индикации не появитсясигнал, готорый говорит о том, что полноформатное слово в выбранной числовой ослова.Режимы выдачи сформированных слов 45и приема слов для расформирования. набайты могут выполняться одновременно.Кроме того, введенные отличительные 03 8признаки позволяют организовать параллел.ную работу устройства в режимах формирования или расформирования слов в одноразрядных блоках 1 памяти и приема и выдачи полнсформвтных слов в блоках 23 памяти магазинного типа, Это позволяет при обмене массивами слов между устрой ством и множеством пользователей уменьшить потери времени на вхождение в связь и выхождение из связи в О раз, где и число регистров в каждом из блоков 23 йагазинного типа. 1 олученный выигрышво времени прямопропорционален числу регистров в блоках 23 памяти магазинного типа, максимальная величина которых определяется количеством слов, которое за один прием может обработать пользователь,ф о р м у л а изобретения Логическое запоминающее устройствопо авт.св. % 649037, о т л и ч в ю щ ее с я тем, что, с целью повышения бысчродействия усчройства, оно содержитпереключатель адресных шин, дешифраторадреса и блоки памяти магазинного типапо числу адресов одноразрядных блоковпамяти, первые и вторые адресные входыпереключателя адресных шин подключенысоответственно к первым и вторым адресным шинам устройства, управляющий входи выходы - соответственно к шине выбораадреса и ко входам дешифратора адреса,упрюляющий вход которого соединен сшиной управления дешифратором, каждыйвход дешифраторв адреса подключен купрюляющим входам регистров соответствующего блока памяти магазинноготипа, в информационные входы первых иинформационные выходы последних регистров каждого блока памяти магазинноготипа подключены соответственно к выходам выдачи слова выходного и ко входамприема слова входного регистров.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРФилиал ППП Патент", г. Ужгород, ул ПИ Заказ 7256/8 М 8103 тира 5 Подписное ктная, 4

СмотретьЗаявка

2840078, 02.11.1979

ОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

НЕСТЕРУК ВАЛЕРИЙ ФИЛИППОВИЧ, ЕФИМОВ СЕРГЕЙ СЕРГЕЕВИЧ

МПК / Метки

МПК: G11C 15/00

Метки: запоминающее, логическое

Опубликовано: 23.08.1981

Код ссылки

<a href="https://patents.su/5-858103-logicheskoe-zapominayushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Логическое запоминающее устройство</a>

Предыдущий патент: Интегральный элемент памяти

Следующий патент: Логическое запоминающее устройтво

Случайный патент: Регулятор роста растений