Система многоканального приема и преобразования в код аналоговых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

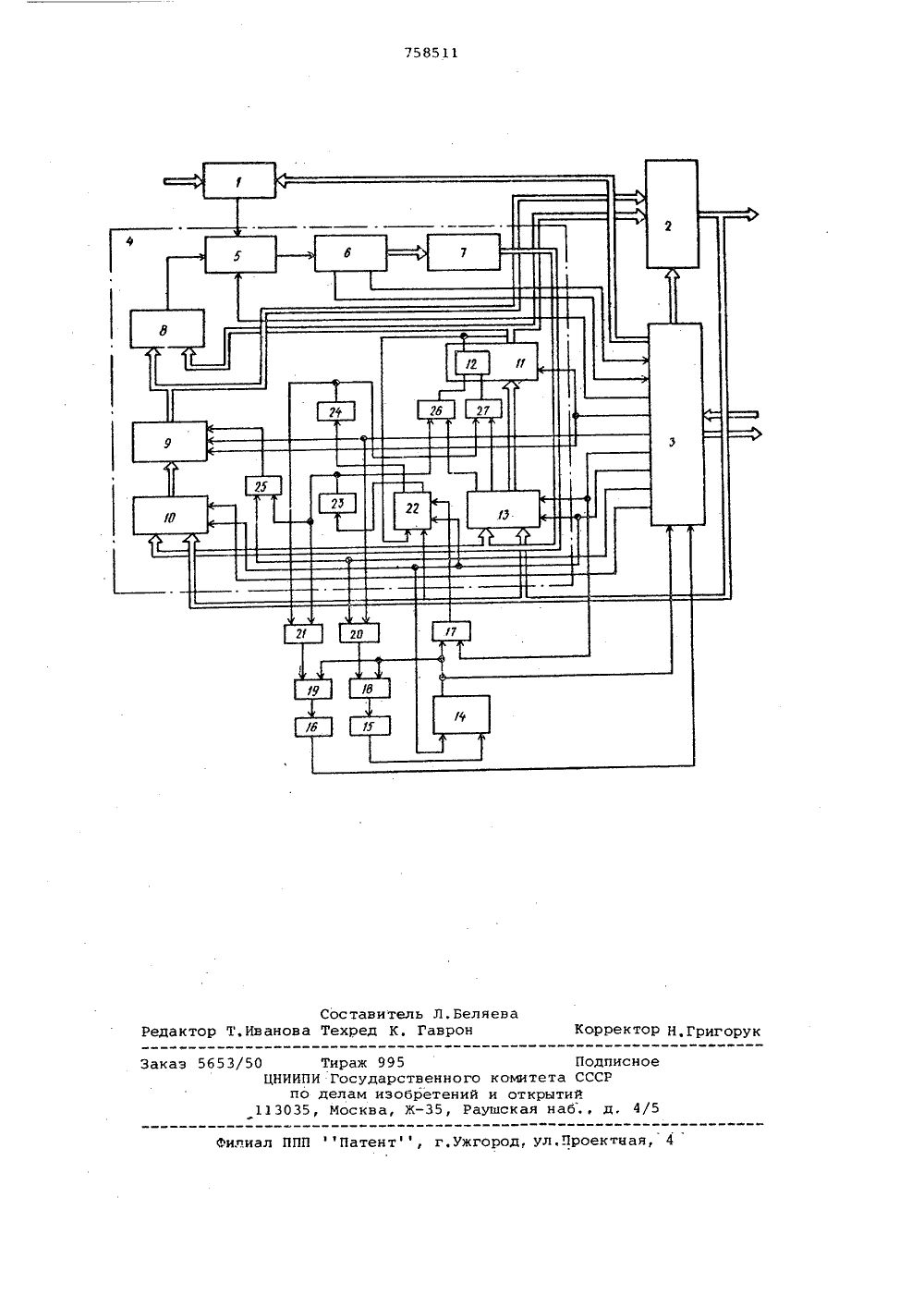

Союз Советских Социалистических Республик(53)М. Кл.З Н 03 К 13/02 Государственный комитет СССР по делам изобретений и открытий(5 4 ) СИСТЕМА МНОГОКАНАЛЬНОГО ПРИЕМАИ ПРЕОБРАЗОВАНИЯ В КОД АНАЛОГОВЫХСИГНАЛОВ Изобретен ие отн оси тс я к ан алогсдискретным преобразователям и предназначено, в частности, для создания высокоэффективных систем много канального приема и преобразования в код аналоговых сигналов.Известна система многоканального приема и преобразования в код аналоговых сигналов, содержащая комлу татор входных аналоговых сигналов, выходом соединенный с входом аналого-цифрового преобразователя (АЦП), кодовые выходы которого соединены с информационными входами блока памяти (1) .Недостатком этой системы является низкая пропускная способность, так как в ней преобразование по каждому каналу выполняется полнотактными из за отсутствия возможности использования результатов преобразования предыдущего цикла преобразования в последующем.Наиболее близкой по техническому 25 решению является система многоканального приема и предбразования в коданалоговых сигналов, содержащая коммутатор, соединенный адресными входами с первыми выходами блока управ ления, вторые выходы которого соединены с первыми входами блока па-мяти, аналого-цифровой преобразова-.тель параллельно-последовательноготипа, в котором аналоговый вычитатель соединен первым входом свыходом коммутатора, вторым входом - с выходом цифро-аналогового преобразователя, третьимвходом - с третьим выходом блока управления и выходом - с входом преобразователя считывания, соединенногопервым и вторым выходами соответственно с первым и вторым входами блокауправления и третьими выходами - свходами преобразователями код - код,выходы которого соединены с первымивходами первого и второго блоков записи, выходы первого из которых соединены с первыми входами реверсивного счетчика, первые выходы второго блока записи соединены спервыми входами регистра, выходы блока памяти соединены с вторыми входами первого и второгоблоков записи, третьи входы блоков записи соединены с четвертым выходом блока управления, пятый и шестой выходы которого соединены соответственно с четвертыми входами первого и второго блоков записи, выходыреверсивного счетчика соединены спервыми входами цифро-аналоговогопреобразователя и вторыми входамкблока памяти, третьи входы которогосоединены с выходом старшегоразряда и кодовыми выходами регистраи с вторыми входами цифро-аналогового преобразователя,.вторые входы регистра и реверсивного счетчика соединены с седьмым выходом блока управления, восьмой выход которого соединен с третьим входом реверсивногосчетчика, Кроме того, девятый выходблока управления соединен с четвертым входом реверсивного счЕтчика, авторой и третий выходы второго блока записи соответственно соединеныс единичным и нулевым входами старшего разряда регистра 2,Недостатком этой системы является 20низкая прогускная способность из-занеобходимости частого выполнения такта аналоговой коррекции между тактами преобразования.Цель изобретения - повышение пропускной способности системы.Поставленная цель достигается тем,что система многоканального приема ипреобразования в код аналоговых сигналов, ссдержаШая коммутатор, соединенный адресными входами с первымивыходами блока управления, вторыевыходы которого соединены с первымивходами блока памяти, аналого-цифровой преобразователь параллельно-последовательного типа,в котором аналоговый вычитатель соединен первым входом с выходом коммутатора, вторымвходом - с выходом цифро-аналоговогопреобразователя, третьим входомтретьим выходом блока управления ивыходом - с входом преобразователясчитывания, соединенного первым ивторым выходами соответственно с первым и вторым входами блока управления и третьими выходами - с входамипреобразователя код-код,выходы которого соединены с первыми входамипервого и второго блоков записи, выходы первого иэ которых соединены спервыми входами реверсивного счетчика, первые выходы второго блока записи соединены с первыми входамирегистра, выходы блока памяти соединены со вторыми входами первого ивторого блоков записи, третьи входыблоков записи соединены с четвертымвыходом блока управления, пятый ишестой выходы которого соединены соответственно. с четвертыми входамипервого и второго блоков записи, выходы реверсивного счетчика соединены бОс первыми входами цифро-аналоговогопреобразователя и вторыми входамиблока памяти, третьи входы которогосоединеиы старшего разряда и кодовыми выходами регистра и с вторыми вхо дами цифро-аналогового преобразоватля, вторые входы регистра и реверсивного счетчика соединены с седьмым выходом блока управления, восьмой выходкоторого соединен с третьим входомреверсивного счетчика, дополнительносодержит триггер, одноразрядный блокзаписи, элементы задержки, элементыИ и элементы ИЛИ, причем нулевой вход триггера соединен с выходом первогоэлемента задержки, выход второгоэлемента задержки соединен с третьимвходом блока управления, четвертыйвход которого соединен с выходомтриггера и с первыми входами элементов И, второй вход первого элементаИ соединен с четвертым входом второго блока записи, выходы второго итретьего элементов И соединены соответственно с входами первого и второго элементов задержки, вторые входы второго и третьего элементов Исоединены соответственно с выходами первого и второго элементов ИЛИ, первый из которых первым входом соединен с третьим входом реверсивногосчетчика, входы третьего и четвертого элементов задержки соединены соответственно с нулевым и единичнымвыходами одноразрядного блока записи, соединенного первым входом с выходом старшего разряда регистра, вторым входом - с выходом блока памяти,третьим входом - с единичнымвходом триггера и с третьим входомблока записи, четвертым входом - свыходом первого элемента И, выход третьего элемента ИЛИ соединен с четверпям входом реверсивного счетчика, первый вход третьего элементаИЛИ соединен со вторым входом первого элемента ИЛИ и с девятым выходомблока управления, выходы четвертогои пятого элементов ИЛИ соединены соответственно с единичным и нулевымвходами старшего разряда регистра,выход третьего элемента задержки соединен со вторым входом третьего элемента ИЛИ и с первыми входами второго и четвертого элементов ИЛИ, второй вход последнего из которых соединенсо вторым выходом второго блоказаписи, третьим выходом соединенного с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента задержки и вторым входом второго элемента ИЛИ.На чертеже представлена структурная схема системы многоканального приема и преобразования в код .аналоговых сигналов.Система содержит коммутатор 1, блок памяти 2, блок управления 3, аналого-циФровой преобразователь 4 параллельно-последовательного типа, аналоговый вычитатель 5, преобразователь считывания б, преобразователь ЦАП) 8, ревврсивный счетчик 9, пер 758511вый блок записи 10, регистр 11,старший разряд 12 регистра,.второйблок записи 13, триггер 14, первый15 и второй 16 элементы задержки,первый 17, второй. 18 и третий 19элементы, первый 20 и второй 21 элементы ИЛИ, одноразрядный блок записи22, третий 23 и четвертый 24 элементы зацержки, третий элемент ИЛИ 25,четвертый 26 и пятый 27 элементы ИЛИ.Система работает следующим образом,Во время первого цикла преобразования, когда в блоке 2 еще отсутству 10 т коды, соответствующие значениям аналоговых сигналов, поданных на входы коммутатора 1. В данной системе, как и в прототипе, осуществляется режим загрузки блока 2, при котором по каждому каналу коммутатора 1 выполняются полные (двухтактные)преобразования. В результате Формируются и запоминаются начальные коды, соответствующие всем входным аналоговым сигналам.В первом такте преобразования вычитатель 5 имеет передаточный коэффициент такой величины, вто при значении входного сигнала, равного максимально допустимой величине диапазона изменения входных сигналов, на выходах преобразователя 6, являющихсявыходами его компараторон, устананливается максимальный позиционный код. Этот код преобразуется преобразонателегл 7 н двоичный код с максимальным значением 2 К -1. Поэтому входной сигнал, имеющий любое другое значение внутри допустимого диапазона изменения, преобоазуется н соотнетствующий двоичный код со значением, лежаший в интервале от 0 да 2 -1. Код,Кобразованный н первом такте на выходах преобразователя 7, далее записывается через блок 10 в счетчик 9, выходы которого управляют преобразонателем 8. Выходной сигнал последнего вычитается из входного преобразуемого сигнала в вычитателе 5, который также усиливает этот разнсстный сигнал, После этого блок 3 формирует другой уровень сигнала, управляющего значением передаточного коэффициента вычитателя 5, который увеличивается в 2" раз сравнению со значением, имевшим место в первом такте преобразования. В результате этого усиленный в 2 раз разностный сигнал приводится к тому же диапазону изменения входных сигналов.Поскольку в рассматриваемом АЦП параллельно-последовательного типа чувствительность компараторов преобраэователя б обычно в (2") раз пренышает величину кванта преобразователя, к моменту начала выполнения второго такта нередко значение выходного сигнала вычитателя 5 выходит5 10 15 20 25 30 35 40 45 50 55 60 65 за пределы диапазона входных сигналов, что принодит к срабатыванию одного иэ граничных компараторов преобразователя б и появлению соотнетствующего сигнала на его первом иливтором выходе. Анализ состояниясигналов на этих выходах производится в блоке 3, При наличии одьогоиз них блок 3 формирует импульс, ко"тарый проходит на третий или четвертый вход счетчика 9, увеличинач илиуменьшая его содержимое на единицу.Одновременно с этим чачинает изменяться на соответствующую величину.выходной сигнал ЦАП 8. Через некоторое время, определяется максимальновозможным временем переходного процесса на выходе ЦАП 8, устанавливается новое значение аналогового сигнала на нходе преобразователя б. Вэтом состоит выполнение такта аналоговой коррекции между первым и вторым так тами преабразав ани ч .Такт аналоговой коррекции заканчивается н момент изменения сигналана первом или втором выходах преобразователя б, инициировавшего этукоррекцию.Затем блок 3 выполняет второйтакт считывания кода с выходов преобразователя 7 н регистр 11 черезблок 13. Далее код с выходов счетчика 9 и регистаа 11 перезапи:ынаетсян соотвествующую ячейку блока 2, чемзаканчивается выполнение полнатактного преобразования аналогового сигнала по данному каналу,После выполнения днухтактных преобразований по всем каналам коммутатора 1 и записи кодов их результатовв ячейки блока 2 блок 3 переходит квыполнению следующего цикла преобразования. Начиная са второго цикла,н системе выполняется толька второйтакт преобразования. Причем выполнение этого такта начинается с записикода предыдущего результата преабразонания из соответствующей ячейкиблока 2 н счетчик 9 через блок 10 ив регистр 11 через блок 13.При этом,в отличие от прототипа, в рассматри -ваемой системе в старший разряд 12регистра 11 код записывается инверс -ным по отношению к значению разряда,поступающему по к-му выходу блока 2.Операция инверсной записи н старший разряд регистра выполняется спомощью выведенных элементон 22, 23,24, 26 и 27. При значении 0 вэтом разряде сигнал с выхода элемента 23 поступает также через элемент25 на четвертый вход счетчика 9,уменьшая его содержимое на единицу.В результате этих операций код, установленный в счетчике 9 и регистре11, меньше на 2 -1 значения кода,Кхранящегося в соответствующей ячейке блока 2Это приводит к относительному смещению уровней сравнения на входах компараторов преобразователя б на величину, равную половине шкалы и позволяет исключить необходимость выполнения аналоговой коррекции после записи кода результата предыдущего преобразования в случае, если входной сигнал за время предыдущего цикла изменился на величину .12 -1 квантов.кИтак, введение в систему триггера блока одноразрядной записи, элементов задержки и элементов И и ИЛИ приводит к существенному поведению -ее пропускной способности, так как практически исключаются такты аналоговой коррекции, начиная со второго цикла преобразований,Формула изобретенияСистема многоканального приема и преобразования в код аналоговых сигналов, содержащая коммутатор, соединенный адресными входами с первыми выходами блока управления, вторые выходы которого соединены с первыми входами блока памяти, аналого-цифровой преобразователь параллельно-последовательного типа,в котором аналоговый вычитатель соединен первым входом с выходом коммутатора, вторым входом - с выходом цифро-аналогового преобразователя, третьим входом - с третьим выходом блока управления и выходом - с входом преобразователя считывания,35 соединенного первым и вторым выходами соотв етств ен но с первым и в торым входами блока управления и третьими выходами - с входами преобразователя код-код, выходы которого соединены с Ю первыми входами первого и второго блоков записи, выходы первого из которых соединены с первыми входами реверсивного счетчика, первые выходы второго блока записи соединены с первыми входами регистра, выходы блока памяти соединены со вторыми входами первого и второго блоков записи, третьи входы блоков записи соединены с четвертым выходом блока управления, пятый и шес той выходы которого соединены соответственно с четвертыми входами первого и второго блоков записи, выходы реверсивного счетчика соединены с первыми входами цифро-аналогового преобразова- теля и вторыми входами блока памяти, третьи входы которого соединены с выходами старшего разряда и кодовыми выходами регистра и со вторыми входами цифро-аналогового преобразователя, вторые входы регистра и реверсивного счетчика соединены с седЬмым выходом блока управления, восьмой выход которого соединен с третьим входом реверсивного счетчика, о т л и ч а ющ а я с я тем, что, с целью повышенияпропускной способности, в нее введенытриггер, одноразрядный блок записи,элементы задержки, элементы И и элементы ИЛИ, причем нулевой вход триггера соединен с выходом первого элемента задержки, выход второго эле -мента задержки соединен с третьимвходом блока управления, четвертыйвход которого соединен с выходомтриггера и с первыми входами элементов И, второй вход первого элементаИ соединен с четвертым входом второго блока записи, выходы второго итретьего элементов И соединены соответственно с входами первого и второго элементов задержки, вторые входы второго и третьего элементов Исоединены соответственно с выходамипервого и второго элементов ИЛИ, первый из которых первым входом соединенс третьим входом реверсивного счетчика, входы третьего и четвертого элементов задержки соединены соответственно с нулевым и единичным выходамиодноразрядного блока записи, соединенного первым входом с выходомстаршего разряда регистра, вторымвходом - с выходом блока памяти,третьим входом - с единичным входомтриггера и с третьим входом первогоблока записи, четвертым входом - с выходом первого элемента И, выход третьего элемента ИЛИ соединен с четвертым входом реверсивного счетчика,первый вход третьего элемента ИЛИсоединен со вторым входом первогоэлемента ИЛИ и с девятым выходом блока управления, выходы четвертого ипятого элементов ИЛИ соединены соответственно с единичным и нулевым входами старшего разряда регистра, выход третьего элемента задержки соединен со вторым входом третьего элемента ИЛИ и с первыми входамивторо -(го и четвертого элементов ИЛИ, второйвход последнего из которых соединенсо вторым выходом второго блока записи, третьим выходом соединенного сс первым входом пятого элемента ИЛИ,второй вход которого соединен с выходом четвертого элемента задержкии вторым входом второго элемента ИЛИ.Источники информации,принятые во внимание при экспертизе1. Шушков Е,И. и Цодиков М,Б.Многоканальные аналого-цифровые преобразователи, Л., Энергия, 1975,с.118, рис.5-б.2. Помехи в цифровой технике -71. Тезисы докладов Всесоюзной научно-технической конференции, Вильнюс, 1971, с,167, рис.1,758511 Составитель Л.БеляеваТ,Иванова Техред К. Гаврон Корректор Н,григорук едакт аэ 5653/50 Тираж 995 ИПИ Государствен по делам изобрете 35, Москва, ЖПодписноого комитета СССРий и открытийРаушская наб., д, 4/ Филиал ПППфПатент , г,ужгород, ул,Чроектыая, 4

СмотретьЗаявка

2636694, 23.06.1978

ПРЕДПРИЯТИЕ ПЯ Г-4128

ВОИТЕЛЕВ АЛЕКСАНДР ИЛЬИЧ, ЛУКЬЯНОВ ЛЕВ МИХАЙЛОВИЧ, ВОДАР ДМИТРИЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: H03K 13/02

Метки: аналоговых, код, многоканального, преобразования, приема, сигналов

Опубликовано: 23.08.1980

Код ссылки

<a href="https://patents.su/5-758511-sistema-mnogokanalnogo-priema-i-preobrazovaniya-v-kod-analogovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Система многоканального приема и преобразования в код аналоговых сигналов</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Параллельно-последовательный аналогоцифровой преобразователь

Случайный патент: Устройство для групповой клепки ступенчатого пакета