Параллельно-последовательный аналогоцифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

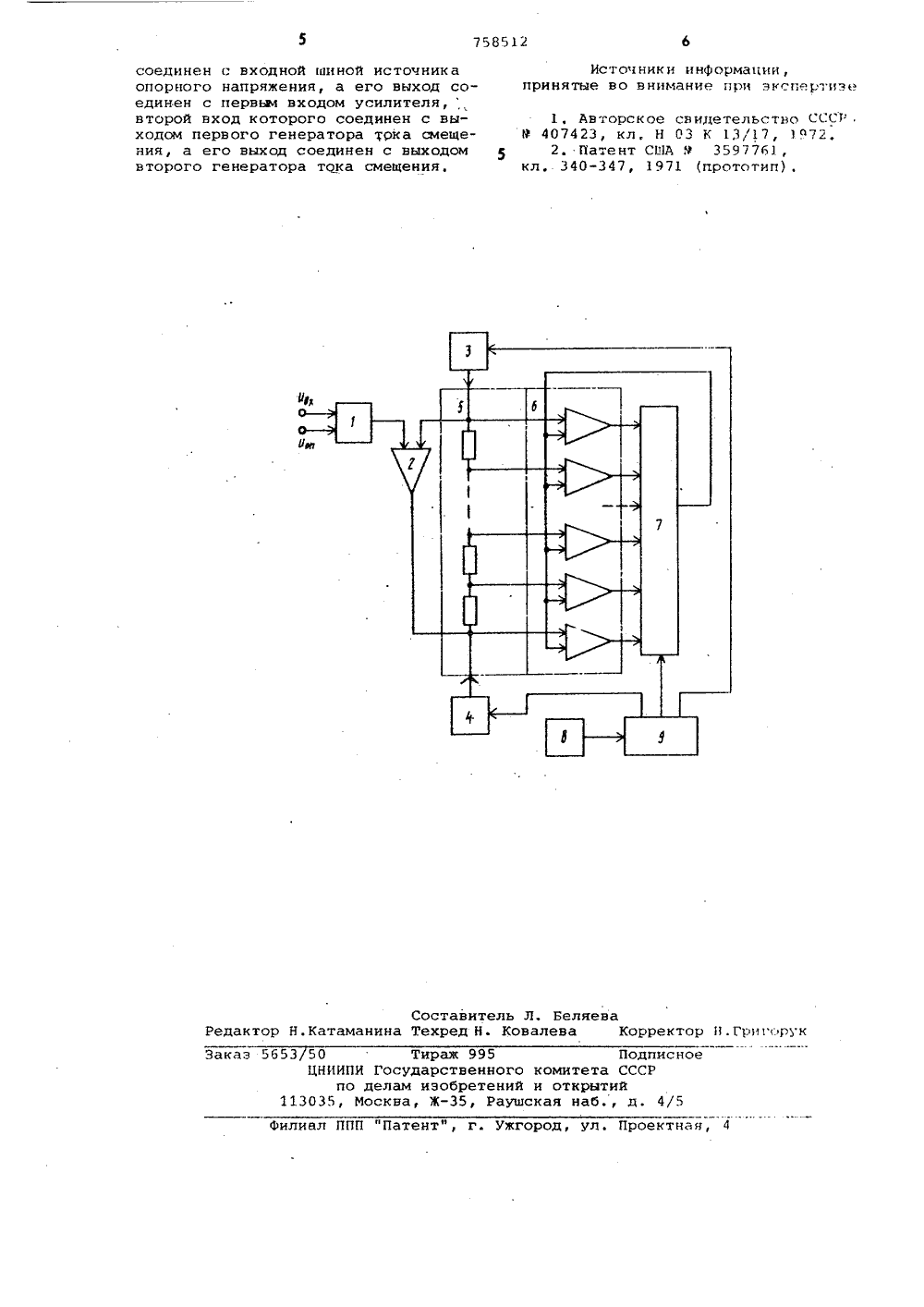

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз Советских Социалистических Республик(22) Заявлено 200677 (21) 2497736/18-21с присоединением заявки Мо(51)М. Кл. Н 03 К 13/17 Государственный комитет СССР по делам изобретений и открытийДата опубликования описания 230880(72) Авторы изобретения О,И.Булавкин, Э.И.Подольный и В,Е.Ямный Белорусский ордена Трудового Красного Знамени государственный университет им.В.И.ЛенинаИзобретение относится к области электронной измерительной техники.Известен аналого-цифровой преобразователь параллельно-последовательного действия, содержащий набор компараторов, последовательный делитель, выходы которого подключены к первым входам компараторов, блок цифроаналогового преобразователя, входы которого соединены с выходами компараторов, а выход подключен ко вторым входам компараторов, тактовый генератор и блок управления 1)Недостатком известного устройства является погрешность преобразования, 15 возникающая вследствие существования входных токов компараторов по цепи последовательного делителя.Наиболее близким по техническому решению является преобразователь (2),О содержащий набор компараторов, выходы которых подключены к входам блока цифроаналогового преобразователя, первые входы подключены к"5 последовательному делителю, а вторые -5 входы объединены и подключены к выходу блока;цифроаналогового преобразователя, генераторы тока смещения, подключенные к верхнему и нижнему концам делителя, причем источник сигнала соединен с одним из концов делителя.Недостатком этого устройства является погрешность преобразования, возникающая вследствие существования входных токов компаратора по цепи делителяЦелью изобретения является повышение точности преобразователя. Поставленная цель достигается тем, что в параллельно-последовательный амплитудно-цифровой преобразователь, содержащий компараторы, первые входы которых подсоединены к последовательному делителю, вторые входы объединены и подсоединены к выходу цифроаналогового преобразователя, а выходы подсоединены к входам цифро-аналового преобразователя, выходы генераторов токов смещения "подсоединены к противоположным концам последовательного делителя, вход первого генератора тока смещения соединен с первым выходом блока управления, второй выход которого соединен со входом цифроаналогового преобразователя, приче,л третий выход со входом второго генератора тока смещения, а вход соединен с выходом тактового генератора, дополнительно введен усилитель и суммирующий блок, первый вход которого соединен со входной шиной источникасигнала, второй вход соединен с входной шиной источника опорного напряжения а его выход соединен с пер 1 5вым входом усилителя, второй входкоторого соединен с выходом первогогенератора тока смещения, а еговыход соединен с выходом второгогенератора тока смещения,На чертеже представлена структурная схема параллельно-последовательного цифро-аналогового преобразователя, содержащего суммирующийблок 1, усилитель 2, генераторы тока смещения 3, 4; делитель 5, кэмпараторы б, блок цифро-аналогового преобразователя 7, тактовый генератор8 и блок управления 9.Устройство работает следующимобразом.20На пе рвый в ход сумми рующ его бло-ка. подключено опорное напряжение,При этом на том конце последовательного делителя, к которому подключенинвертирующий вход усилителя установится напряжение, равное опорному спогрешностью, равной, где к - коКэффициент усиления усилителя, Величина тока смещения через последовательный делитель устанавливаетсягенераторами смещения тока 3 и 4 и,тем сатым, задается величина начальных порогов преобразователя, С тактового генератора поступают импульсы на блок управления, который вырабатыв ает импульсы з анесения кодовв регис тр с тарших и младших разрядов цифро-аналогового Преобразователя и так товые импульсы. Вначальном состоянии на входнойшине источника сигнала потенциал40рав ен нулю, потенциалы выходовкбмпара торов равны нулю, потенциалы выходов блока 7. тоже равнынулю, По роги компара торов установлены таким образом, что при начале4 эраооты происходит определение кодастарших разрядов. Например, в случае 8 -ми разрядного двухтактногопреобразователя, первым тактом блока управления устанавливается величина тока смещения через последовательный делитель такой, что при этомопределяется код первых (старших)четырех разрядов, который занесется в старший разряды блока 7, По 55этому коду блок 7 вырабатывает напряжение, которое изменит потенциалвторых входов компараторов. Вторымтактовым импульсом управляющего устройства изменится ток смещения генераторов смещения тока 3 и 4 в 1 б фраз так, что ширина шага преобразователя станет равной - предыдущего1 Ьзначения.Теперь преобразователь будетогределять код остаточного напряже ния, т,е. тото, которое равно разности ОХ"цт 1 л , Приведенная последовательность операций преобразователяничем не отличается от работы обычного последовательно-параллельногопреобразователя с одним набором компараторов и одним входным устройством,Смещение всей шкалы после.1 овательного делит ля объясняется тем, чтосуммарное сопротивление делителямного меньше выходного сопротивления генераторов смещения токов 3 и 4,поэтому любое изменение напряженияв любой точке делителя приведет ктакому же сдвигу по напряжению кон -цов делителя. Усилитель восприметэтот сдвиг, как сигнал ошибки, который и будет скомпенсирован. Окончательная ошибка будет в к раз меньше.Компенсация происходит за счет увеличения тока 3, тока компенсациидля обеспечения линейного режимаусилителя, при этом поскольку компенсируются входные токи сработавших компараторов, то ЬО ошибки навходе последнего сработавшего компаратора будет скомпенсировано практически полностью, а на входе ранеесработавших компараторов сигналошибки будет перекомпенсирован,Однако это уже не имеет значения,поскольку перекомпенсация возникает после того, как эти компараторывыполнили свою функцию.При исполь з овании в схеме к омпен-, сации усилителя с коэффициентом усиления 50, погрешность преобразования не превышает величины + -младшего разряда.Формула изобретенияПараллельно-последовательный ана- лого-цифровой преобразователь, содержащий комараторы, первые входы которых подсоединены к последовательному делителю, вторые входы объединены и подсоединены к выходу цифроаналогового преобразователя, а выходы подсоединены к входам цифроаналогового преобразователя, выходы генераторов токов смещения подсоединены к противоположным Концам последовательного делителя, вход первого генератора тока смещения соединен с первым выходом блока управления, вто рой выходкоторого соединен со входом цифроаналогового преобразователя, причем третий выход со входомвторого генератора тока смещенИя, а вход соединен с выходом тактового генератора, о т л и ч а ю щ и й с я тем, что, с целью повышения точности в него дополнительно введен усилитель и суммирующий блок, первый вход которого соединен со входной шиной источника сигнала, второй вход75 В 512 Составитель Л. БеляеваРедактор Н.Катаманина Техред Н. Ковалева Корректор Н.Грнго Тираж 995 Подписнодарственного комитета СССРизобретений и открытийЖ, Раушская наб., д, 4/5 акаэ лиал ППП "Патент", г. Ужгород, ул. Проектная соединен с входной щиной источникаопорного напряжения, а его выход соединен с первьи входом усилителя,второй вход которого соединен с выходом первого генератора тока смещения, а его выход соединен с выходомвторого генератора тока смещения. 653 50 цНИИПИ Госу по делам 113035, МоскваИсточники инФормации,принятые ВО Внимание при экспертиве

СмотретьЗаявка

2497736, 20.06.1977

БЕЛОРУССКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИМ. В. И. ЛЕНИНА

БУЛАВКИН ОЛЕГ ИВАНОВИЧ, ПОДОЛЬНЫЙ ЭДУАРД ИОВОВИЧ, ЯМНЫЙ ВИТАЛИЙ ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: H03K 13/17

Метки: аналогоцифровой, параллельно-последовательный

Опубликовано: 23.08.1980

Код ссылки

<a href="https://patents.su/3-758512-parallelno-posledovatelnyjj-analogocifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналогоцифровой преобразователь</a>

Предыдущий патент: Система многоканального приема и преобразования в код аналоговых сигналов

Следующий патент: Система передачи и приема сигналов с дифференциальной импульсно-кодовой модуляцией

Случайный патент: Устройство для удаления и улавливания пыли и газов, образующихся при работе очистного комбайна