Устройство для решения систем дифференцильных уравнений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

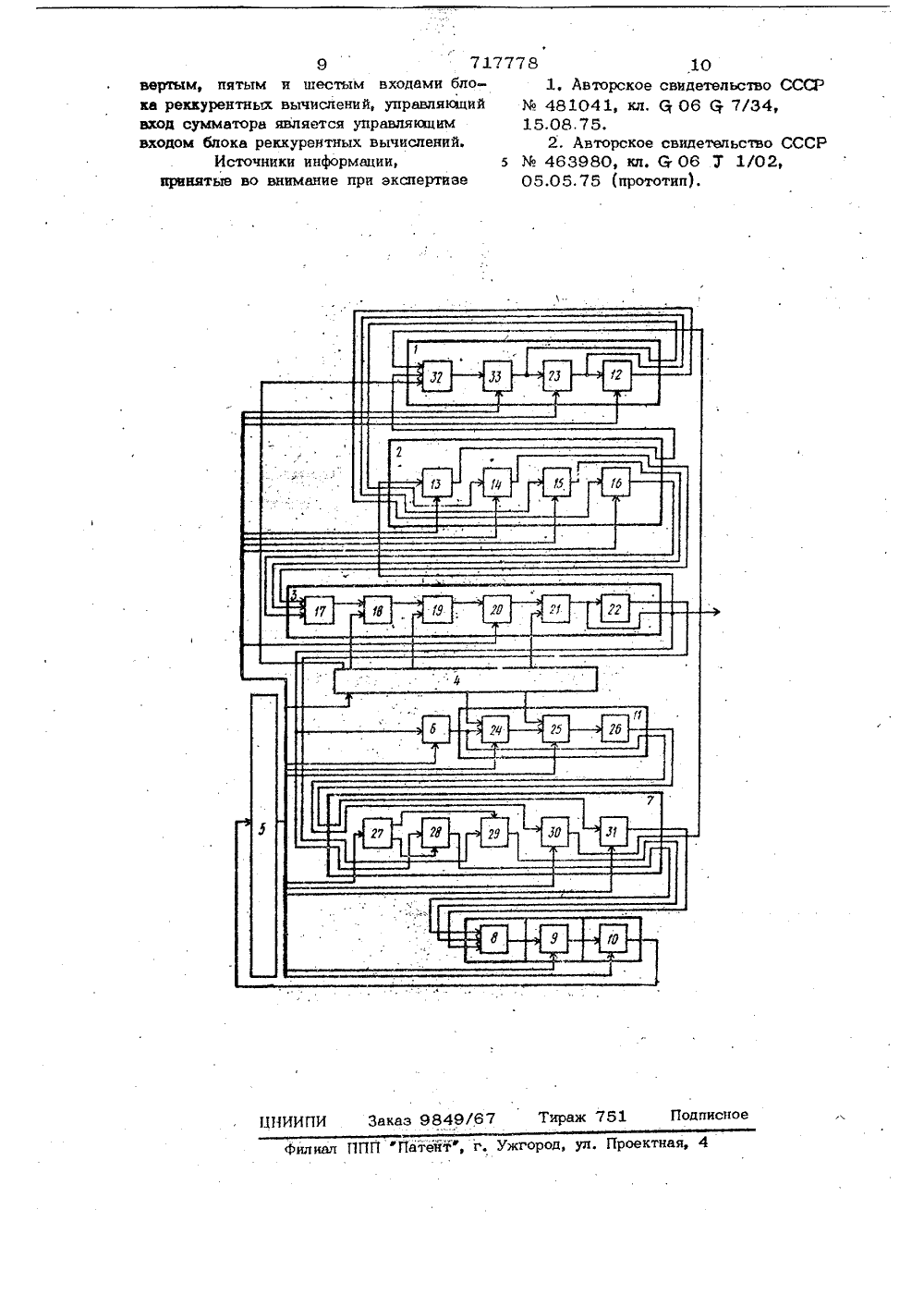

ОП ИСАНИЕИЗЬЬееЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советски кСоциалистическикРвснубяин 17778 Дон лнятельиое к авт, сеид-вуено 03,10.77 (21)2529949/18 2. Кл. 006 Г ниеее заявки соед ный наинтет Всувв 3) Приопубликоваи ата опубли 72) Авторы изобретени Н. Во Г, Е. Пухо о лектродинамики АН Украинской ССР исти(7 ) Заявит ЕРЕН Н 4 АЛЪНЫХ ЕНИЯ СИСТЕМУРАВНЕНИЙ 4) УСТРОЙСТВО ДЛЯ относится к области выики и может быть приения с высокой точностью енных дифференциальных имер в системах параметфикаюни и управления сложми системами и обьекИзобретениечислительной технменено для решсистем обыкновуравнений, напррической идентиными динамически яв ф известного устрой очность получаем достатко реляется ншенин. ее бли изобретеее блок и второй остаткомнизкая зким по технической сущнию является устройство,управления, блок памяти,коммутаторы 2.известного устройстваточность работы устрой Наиболности ксод ержащпервый Целью изобретения является повышение точности работы устройства.Поставленная пель достигается тем, то в устройство дополнительно введены первый и второй блоки сдвига, блок рвк курентных вычислений, первый и второй сумматора, элемент ИЛИ и блок сравнения, причем первый, второй и третий выоды блока памяти подключены соответ ственно к первому, второму и третьему ходам блока реккурентных вычислений, ервый выход которого соединен с первым ходом первого коммутатора, первый выод которого подключен к первому входу тами. Недявля етсИзвестны устройства (вычислитвльныв, ства. структуры) для решении систем обыкно- / венных дифференциальных уравнений, содвржашие блок управления, блок памяти,блоки коммутаторов (управляемых ключей), ч блоки умножителей, сумматоров, интеграторов и функпиональных преобразователейЫИ зввсчные вычислительные структурыпозволяют находить решения систем. обык- х новеннык дифференпиальных уравнений пер-ро вого порядка путем предварительного оп- в ределения вектора правых частей системы и и последукклего его интегрирования для в получения вектора решения. х3 717778,4первого блока сдвига, первый, второй и ИЛИ являются соответственно четвертым,третий выходы которого соединены с вто- пятым и шестым входами блока реккурензрым, третьим и четвертымвходами пер- ных вычислений, управляющий вход сумма-вого коммутатора, второй, третий и чег- тора является управляющим входом блокавертый выходы которого подключены к5 реккурентных вычислений.четвертому, пятому и шестому входам бло- На чертеже представлено предлагаека реккурентных вычислений, второй вы- мое устройство:ход которо 1 о соединен с первым входом второ. Устройство содержит блок 1 сдвигагокоймутатора,второйвходкоторогоподклю- информации, блок 2 коммутаторов, блокчен к входу первого сумматора и к перво- о 3 реккурентных вычислений, блок 4 памяму выходу блока реккурентных вычисле- ти, блок 5 управления, сумматор 6, блокний, выход первого сумматора соединен 7 коммутаторов, элемент ИЛИ 8, сумма с первым входом второгоблока сдвйга и тор 9, блок 10 сравнения и блок 11 сдвис .вторым входом второго коммутатора, га, Блок 1 сдвига информации состоит изпервый, второй и третий выходы которого : элементов ИЛИ 32, запоминакщих регионподключены к первому, второму и третье- ров 12, 23 и ЗЗ.му входам элемента ИЛИ, выход которога Блок 2 коммутаторов состоит из элесоединен с входом второго сумматора, ментов И 13-16.выход которого подключен к входу блока Блок 3 реккурентных вычислений состосравнения, выход которого соединен с вхо. И ит из элементов ИЛИ 17, первого блокадом блока управления, четвертый и пяалый 18 умножителей,элементов ИЛИ 19, бловыходы блока памяти подключены соответ ка 20 наканливающих сумматоров; блока.второго блока сдвига, выход которого сое Блок 11 сдвига состоит из запоминадинен с третьим входом второго коммута ющих регистров 24 и 25 и блока 26 ин"25тора, четвертый входкотороГо подключен верторов знака.к второму выходу блока реккурентных вы Блок 7 коммутаторов состоит из упчислений, четвертый восход второго ком- равляющего триггера 27 и коммутаторовмутатора соединен с вторым входом пер-31вого коммутатора, третий вход котороготретий вход которого, зО Работа предлагаемой вычислительной"подключен к шестому выходуму выходу блока памя- системы поясняется на примере решенияти упр е в"" авляющае входы первого и второго систем дифференциальных уравнений видак- Ьблока сдвигов, блока памяти, блока Рек-А Х=68;кО=Хкурентныхвычислений, первого и второго яосйяЗФоров; первого и второго коммутато З гд (О р35 где х(Овектор Неизвестных;ров, блЬкь сравнения соединены с соотгбл " " ы оот Ю матрица переменных коэффициветствукацими выходами блока управления.Я 1) - вектор правых частей;Кр ме б к ре курен ыхвычилений содеРжит блоки УмножениЯф сУмма е Х(О) - начальное значение Х(+) при=О.тор, инвертор и элементы ИЛИ выходИ:юльзуя Т-преобразование Тейлора,первого из которых подключен к первому данная система приводится к видувходу первого блока умножения, второй Ивход"ро е пр входом бл -"-"- Х(М)+Е А.,(Е)Х СК-Е).К(К),Х,(О)=ХрН)ка реккурентных вычислений, выход бюка 4, Н Е-"оуМнбженйя подключен Ы"первому" входу вто. где Х К) - вектор Ъ -х дискрет, нзобрарого элемента ИЛИ, вьйод"которого" сое жающий вектор Х 1вектор" "дийей"с входом суЮ 4 атора, выход которо функции;го подкл 1 оченкпервому входу второгоЦМ- вектор К -х дискрет, изобраблока уййойВния; виход которого являет жающий вектор 111) векторся первым выходом блока реккурентных функции;вычислений и соединей с входом инвертоАЯВ)- матрица-х дискрет, изобража" - ра, вшаод которогоявляется вторым выющая матрицу АКС) матричнойходом блока реккурентных вычислений функции.Работа вычислительной системы начинавторые входы второго элемента ИЖ иы вычиго бл умножения являются соот ется с вйдачи снгналов управления с выя на ляющиеветственно вторым и третьим входами ходов блока 5 управления на управблокареккурентных вычивычислений первый, входы блока 4 памяти и запоминающихвторой и третий входы первого элемента регистров 24 и 25. При поступлении этих7 71777 сжному выше, регистров 33, 23 и 12 сумматоров 20, 6 и 9 бпокв 10 сравнения и управляющего триггера (возврат в метку % 1), и производится следующий шаг вычислений: определяется вектор дис крет Х.+ Ь)/й вЕсли условие окончания не выполнено, то осуществляется установка в руль блока 20 накаппивакицихсумматоров и измейенае состоянии уцравлякщ его триггера 1 О 27 на противоположное - единичный сигнал с его прямого выхода открывает второй элемент И 29, а нулевой с инверс го коммутатора, второй, третий и четвертый выходы которого подключены к чувертому, пятому и шестому входам блокареккурентных вычислений, второй выходкоторого соединен с первым входом второго коммутатора, второй вход которогоподключен к входу первого сумматора ик первому. выходу блока реккурентных вычислений, выход первого сумматора, сое динен с первым входом второго блока сдвига и с вторым входом второго коммутатора,первый, второй и третий выходы которого подключены к первому, второму и третьему входам элемента ИЛИ, выход которого соединен с входом второго сумматора, выход которого подключен к входублока сравнения, выход которого соединенс входом блока управления, четвертый ипятый выходы блока памяти подключенысоответсженно к второму и третьему входам второго блока сдвига, выход которого соединен с третьим входом второгокоммутатора, четвертый вход которогоподключен к второму выходу блока реккурентных -вычислений, четвертый выходвторого коммутатора соединен с вторымвходом первого коммутаторатре жй входкоторого подключен к шестому выходублока памяти, упрввляккцие входы первоблока реккурентных вычислений, первого и второго сумматора, первого и второго коммутатора, блока сравнения соединены с соответствукицими выходами блока управления,2, Устройство по п, 1, о т л и ч аного выхода - закрывает первый элемент И 28 коммутатора 7 в следующем цикле вычислений, на вход сумматора 9 поступает инверсное значение вектора дискрет с выходов блока 22 инверторов. По сиг,налу упрввления из блоке 5 открывается элемент И 13 коммутатора 2 и значение Ю вектора дискрет Х 1 Я/1-с с вторых вы ходов блока 3 реккурентных вычислений через открытый элемент И 13 поступает нв вторые входы блока 1 сдвига информации. После этого осуществляется возврат в метку М. 2 алгоритма работы системы: в регистр 23 блока 1 записывает ся значение вектора дискрет Хо, в регистр 33 - значение вектора дискрет 1(ОЯ 1 и аналогично описанному выше вычисляется вектор дискрет Хо ( 2).Описываемое устройство благодаря на личию новых элементов и связей между ними позволяет повысить точность решения систем дифференциальных уравнений. го и второю блока сдвиюв, блока памятир/ 1. Устройство для решения систем дифОференциальных уравнений, содержащее блокуправления, блок памяти, первый и второйкоммутаторы, о т л и ч а ю щ е е с ятем, что, с целью повышения точностиустройства, в него дополнительно введены 15первый и второй блоки сдвига, блок реккурентных вычислений, первый и второйсумматоры, элементы ИЛИ и блок сравнения, причем первый, второй и третийвыходы бпокв памяти жщключены аоот- Овек;"женно к первому, второму и третьему входам блока реккурентяых вычислений,первый выход которого соединен с первым:входом первого коммутатора, первый вие55ход которого подключм к первому входупервого блока сдвига, первый, второй итретий выходы которого соединены с вто" рым, третьим и четвертым входами перро ю щ е е с я тем, что блок реккурентныхвычислений содержит блоки умножения,сумматор, инвертор и элементы ИЛИ, выход первого из которых подключен к первому входу первого блока умножения, вто рой вход которою является первым входом блока реккурентных вычислений, выход блока умножения подключен к первому входу второю элемента ИЛИ, выход которого соединен с входом сумматора, выход которою подключен к первому вхо-, ду второго блока умножения, выход которою является первым выходом блока реккурентных вычислений и соединен с входом инвертора, выход которого является вторым выходом блока реккурентных вы числений, вторые входы второго элемента ИЛИ и второго блока умножение являют-, ся аоответстееоно вторым и третьим вхбдами блока реккурентных вычиспений, пер. вый, второй и третий входы первого элемента ИЛИ являются соответственно четираж 751 Подписи з 9849/67 ШИИ ейт роектна илкал 11 П жгород,9 717778 10вертим, пятым и кестым входами бло. Авторское свидетельство СССРка реккурентньас вычислений, управляющий % 481041, кл. Я 06 Ст 7/34,вход сумматора является управлякщим 15.08, 75,входом блока реккуреитных вычислений. 2. Авторское свидетельство СССРИсточники информации, 5 % 463980, кл. 6 06 Т 1/02,принятые во внимание при экспертизе 05.05,75 (прототип).

СмотретьЗаявка

2529949, 03.10.1977

ИНСТИТУТ ЭЛЕКТРОДИНАМИКИ АН УКРАИНСКОЙ ССР

ПУХОВ ГЕОРГИЙ ЕВГЕНЬЕВИЧ, ВОЙТЕНКОВ ИГОРЬ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 17/13

Метки: дифференцильных, решения, систем, уравнений

Опубликовано: 25.02.1980

Код ссылки

<a href="https://patents.su/5-717778-ustrojjstvo-dlya-resheniya-sistem-differencilnykh-uravnenijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для решения систем дифференцильных уравнений</a>

Предыдущий патент: Модель узла графа

Следующий патент: Устройство для вычисления собственных чисел корреляционных матриц

Случайный патент: Устройство для автоматической сварки сильфона