Устройство для адаптивного преобразования аналоговых сигналов в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

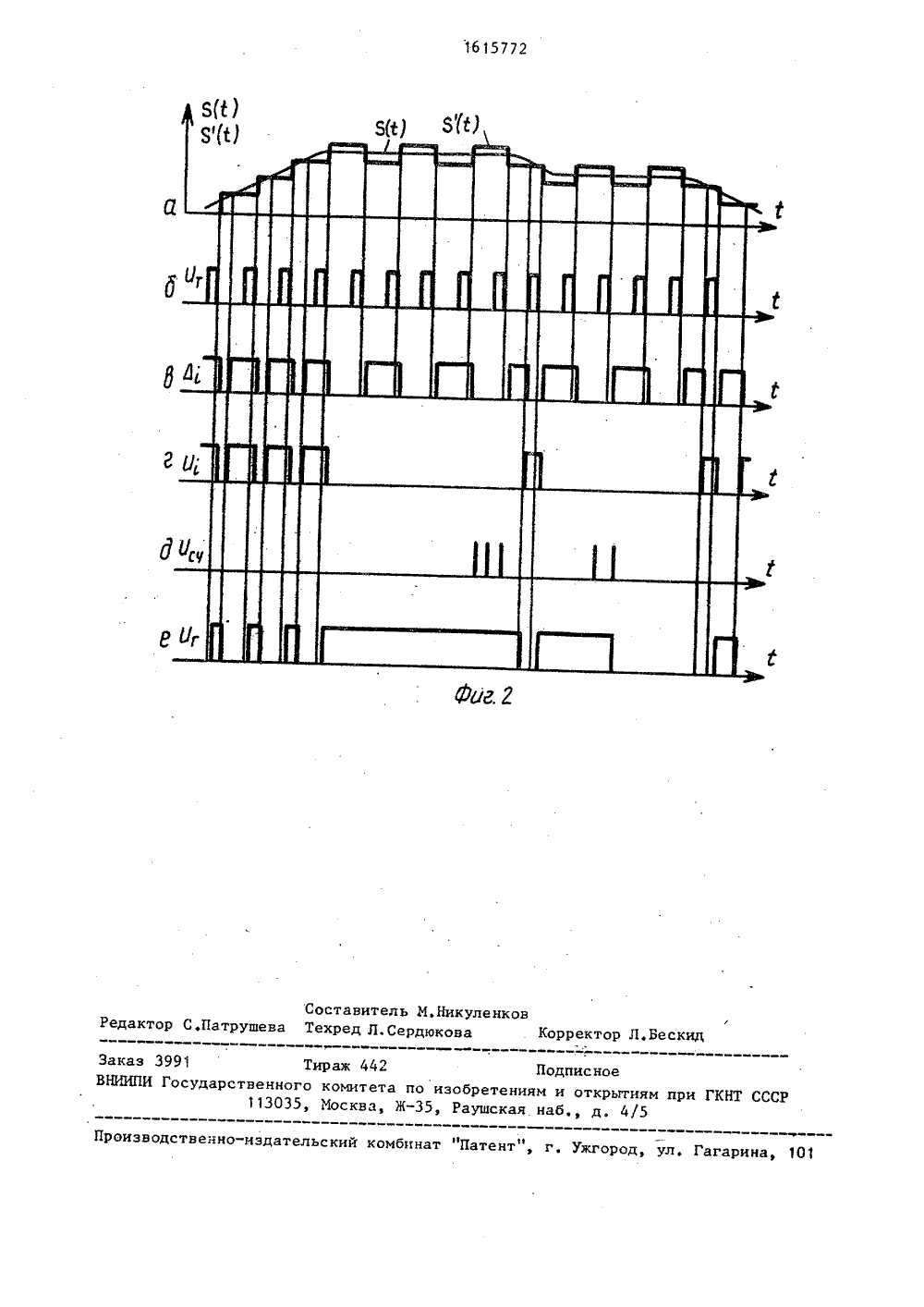

(ге а) 15772 А 1 08 С 19/28 ПИСАНИЕ ИЗОБРЕТЕН г ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЭОБРЕТЕНИЯМ И ОТНРЬГИЯМПРИ ГКНТ СССР(56) Авторское свидетельство СССР У 1123045, кл. С 08 С 19/28, 1984.Авторское свидетельство СССР В 1206958, кл, Н 03 М 3/02, 1984.(54) УСТРОЙСТВО ДЛЯ АДАПТИВНОГОПРЕОБРАЗОВАНИЯ АНАЛОГОВЫХ СИГНАЛОВ В КОД(57) Изобретение относится к автоматике, телемеханике и может использоваться в адаптивных телеметрических , системах. Устройство осуществляет 1 преобразование в дискретные моментывремени входного аналогового сигналав код, эапоминание существенных значений выборок преобразованного сигнала и выдачу запомненных существенныхвыборок по запросу на выходы 18, чтоуменьшает информационную избыточностьпреобразуемого сигнала и повышает информативность устройства Устройствосодержит компаратор 1, элементы НК 210, элементы И 3, 4, 9, 13, элементИСКЛЮЧАВШЕЕ ИЛИ-НЕ 5, триггер 6, счетчики 7, 11, цифроаналоговый преобразователь 8, блок 12 оперативной памяти,информационные и тактовые входы 14,15 и 16, 17, информационные и управляющий выходы 18 и 19, 2 нл,Изобретение относится к автоматике, 1 елемеханике и может использоваться з адаптивных телеметрических системах.5Цель изобретения - повышение информативности устройства.На фиг.1 показана функциональная хема устройства; на Фиг.2 - времене диаграммы, поясняющие его работу. 10Устройство содержит (фиг.1) компаатор 1, первый элемент НЕ 2, второйпервый элементы И 3 и 4, элемент СКЛКИАКЩЕЕ ИЛИ-НЕ 5, триггер 6, перый реверсивный.счетчик 7, цифро налоговый преобразователь 8, третий лемент И 9, второй элемент НЕ 10, торой реверсивный счетчик 11, блок 2 оперативной памяти, четвертый лемент И 13, второй и первый инфор О ационные входы 14 и 15, первый и торой тактовые входы 16 и 17, инфорационные и управляющий выходы 1819.Преобразование входного сигнала 25 .(С) (Фиг .2 а) в двоичный код осущетвляется методом следящего уравновевания, заключающегося в поочередном 6 равнении преобразуемого сигнала на 1"м такте временной дискретизации Ю суммой образцовых дискретных вели 1 ин, определяемой ФормулойБ ("1)= Дцв,Е "2=о 135р - величина шага квантования;К - коэффициент для двоичной3системы счисления, равный0 или 1 в зависимости отрезультатов сравнения на 40х-м такте временной дискретизации;и - разрядность двоичного кодапреобразования;Б (С) - восстановленный аналоковый 45сигнал, соответствующийс заданной погрешностьювходному на х-м такте временной дискретизации.В процессе преобразования сигнала 8(С) Формируется последовательность дельта-сигналов Ь, (фиг.4 в), котоРые. Формируются по правилу1 при. Б(С) ) Б(С);1 О при Б(С) с Б(С), Сигнал Б (С) формируется цифроаналоговым преобразователем 8 (фиг,2 а) из двоичного кода счетчика 7 разрядностью и и отражает исходный сигнал тде ВН с заданной погрешностью, Величина этой погрешности определяется числом разрядов двоичного кода, используемого для восстановления сигнала Б (С), и может регулироваться в необходимых пределах количеством разрядов двоичного кода, подаваемого с выхода счетчика 7 в цифроаналоговый преобразователь 8.Для определения адаптивных выборок дельта-сигналы подвергаются логической обработке, в результате которой Формируется сигнал 13, (фиг.2 г)=1 при Ь; =Д,Темп обработки дельта-сигналов определяется входной тактовой частотой импульсов Г (фиг.2 б), которая назначается с учетом динамических и частотных свойств преобразуемого сигнала.Двоичные коды сформированных адаптивных выборок и коды времени, соответствующие моментам их формирования, записываются в блок 12 памяти. Временная привязка адаптивных выборок при передаче их в асинхронном режиме позволяет восстанавливать исходный сигнал Б(С) без искажений его формы.Информационная емкость блока 12 зависит от количества запоминаемых адаптивных выборок в течение отрезка времени, определяемого внешним устройством, погрешности преобразования, определяемой количеством разрядов счетчика 7, и точности временной привязки, определяемой количеством разрядов кода времени на входе 14.Для выдачи кодов преобразованного сигнала Б(С) из блока 12 на выходы 18 на вход 17 поступают импульсы считывания 0 (Фиг,2 д), которые формируются внешним устройством при наличии сигнала готовности на выходе 19 П- (Фиг.2 е), В свою очередь, сигнал готовности Б формируется только при наличии в блоке 12 двоичного кода хотя бы одной адаптивной выборки, При этом в моменты Формирования и записи адаптивных выборок он не Формируется, так как считывание информации из блока 12 в эти моменты времени приведет к потере формируемой адаптивной выборки.Устройство работает следующим образом.2щийся в данный момент времени в счетчике 7,является избыточным, Сигнал тивной выборке и, поступая на входблока 12, переводит его в режим записи информации. Фронтом тактовогоимпульса, поступакщего на вход 16,двоичный код входного сигнала с выходов счетчика 7 и двоичный код времени с входа 1 ч записываются в ячейкиблока 12 памяти по адресу, определяемому двоичньпк кодом, поступающимс выходов счетчика 11,После записи информации спадом20 тактового импульса производится инкрементирование адреса ячеек блока 12памяти, Единичный сигнал Б, =1 поступает на вход элемента И 9, и спадтактового импульса через открытый25 элемент И 9 поступает на инкрементирующий вход счетчика 11. В результате двоичное число в счетчике 11 увеличивается на 1, подготавливая очередные ячейки блока 12 памяти к записи двоичного кода последующей адаптивной выборки,Одновременно с логической обработкой дельта-сигналов и записью информации в блок 12 Формируется сигнал35готовности устройства Б к выдаче. кодов входного сигнала из блока 12на выходы 18., Для этого на втором выьходе счетчика 11 формируется единичньп сигнал, если в блоке 12 находитсякод хотя бы одной адаптивной выборкиподлежащей выдаче.:, В противном;:случае, когда на адресные входы блока12 с первых выходов счетчика 11 поступает адрес нулевой ячейки, что соответствует отсутствию в блоке 12кодов адаптивных выборок, на второмсчетчике 11 формируется нулевой сиг- .,нал. Этот сигнал через элемент И 13поступает на выход 19, На другой входэлемента И 13 через элемент НЕ 10поступает сигнал О;, который:запрещает прохождение сигнала с второго выхода счетчика 11 в моменты формирования и записи адаптивных выборок . Сформированный сигнал готовности с выходаэлемента И 13 поступает на выход 19Таким образом, сигнал готовности Ог=1формируется только в том случае, кода в блоке 12 находится код хотя бы 5 16157Сигнал Ы(С) с входа 15 поступаетна первый вход компаратора 1, на второй вход которого подается восстановленный сигнал ЯИ), отображающийвходной сигнал Я(Т) с требуемой точностью. Компаратор 1 сравнивает сигналы Я(С), Я Ы) и в зависимости отрезультатов сравнения на, его выходеФормируются дельта-сигналы; Ь, =1,если ЯЙ) )Я И), и 1=0, если Я61с Я . Предположим, что сигналЯИ) ) Я (1), тогда сигнал Ь; =1 свыхода компаратора 1 открывает элемент И 4 и обеспечивает поступлениес входа 1 б тактовых импульсов наинкрементирующий вход счетчика 7,увеличивая его содержимое, Если ЯЯ (С), то на выходе компаратора 1Формируется сигнал Ъ, =О, который,инвертируясь элементом НЕ 2, открывает элемент И 3, и тактовые импульсыпоступают на декрементирующий входсчетчика 7, уменьшая его содержимое.Таким образом, двоичный код в счет счетчике 7 в каждый момент временипропорционален входному сигналу Я.Для формирования сигнала Ядвоич:нЖ код из счетчика 7 поступает вцифроаналоговый преобразователь 8;а также на информационные входы блока12 оперативной памяти ..входного сигнала Я(С) в двоичный кодосуществляется логическая обработкадельта-сигналов Ь;. На информационныйвход триггера 6 поступает последовательность дельта-сигналов, отображаю-щих текущие изменения входного сигнала. ;о спаду очередного тактовогоимпульса в триггере б запоминаетсяпредыдущее значение дельта-сигналаи формируется сигналЭтисигналы поступают на входы элемента 5ИСКЛВИАЮЩЕЕ ИЛИ-НЕ 5, на выходе кото,рого формируется сигнал Ы, . При совпадении двух подряд следующих сигналов, что соответствует изменению9сигнала Я(г) (Ь;, =6,=1 - его возрастанию, Ь; =6; =О - его убыванию), навыходе элемента ИСКЛЮЧАКЩЕЕ ИЛИ-НЕ 5появляется, единичный логический уровень.При чередовании дельта-сигналов(о, 1 Ф 6,) на выходе элемента ИСКЛЮЧАЩЕЕ ИЛИ-НЕ 5 формируется нулевойлогический уровень, свидетельствующийо том, что входной сигнал в данныймомент времени не изменяется и двоичный код регулярной выборки, находяУ,=О, поступая на вход блока 12, поддерживает его в режиме считывания инФормации, и запись данного кода регулярной выборки в блок 12 не происходит. Сигнал Б;=1 соответствует адап 1 б 15772оной адаптивной выборки и когда отсутствует процесс формирования и залси очередной адаптивной выборки.Процесс накопления адаптивных выборок с соответствующими им кодами времени в блоке 12 происходит до техпор, пока на вход 17 не поступят импульсы считывания информации. Импуль. ссчитывания с входа 17 проходят на екрементирующий вход счетчика 11 иеньшают двоичное число в счетчике 11, обеспечивая обратное переключение5ресов ячеек блока 12 памяти, в коорых хранятся коды предыдущих адапивных выборок. При этом коды адапвных выборок из блока 12 поступают а выходы 18,Процесс считывания происходит до ех пор, пока вся информация из блока 2 2 не будет выдана либо пока не начется формирование очередной адаптивой выборки,Таким образом, на выходах 18 поомандам от внешнего устройства фор ируют двоичные коды значений входного сигнала 8(й), только в случае его озрастания или убьвания, что позвояет уменьшить информационную избыточность преобразуемого сигнала а а счет сохранения всех его существенных значений в блоке памяти иовыить информативность устройства.з обру л оУ стройство для адаптивного преобРазования аналоговых сигналов в код,одержащее компаратор, первый входоторого является первым информацион-,О ным входом устройства, выход компара 1 ора соединен непосредственно с ин-:и Формационным входом триггера, первым входом первого элемента И и через первый элемент НЕ с первым входа второго элемента И, выходы первого и второго элементов И соединены соответственно с суммирующим и вычтающим входами первого счетчика, выходыкоторого соединены с одноименнымивходами цифроаналогового преобразователя, выход которого соединен с вторым входом компаратора, третий ичетвертый элементы И, выход четвертого элемента И является управляющимвыходом устройства, тактовый входтриггера объединен с вторыми входамипервого и второго элементов И и является первым тактовым входом устройства, о т л и ч а ю щ е е с я тем,что, с целью повышения информативности устройства, в него введены элементИСКЛИЧАКЩЕЕ ИЛИ-НЕ, второй элементНЕ, блок оперативной памяти и второйсчетчик, вычитающий вход которого является вторым тактовым входом устройства, выход триггера соединен с пер-вым входом элемента ИСИПОЧАЯЦЕЕ ИЛИНЕ, второй вход которого подключен квыходу компаратора, выход элементаИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ соединен непосредственно с первым управляющим входомоперативной памяти, первым входомтретьего элемента И и через второйэлемент НЕ с первым входом четвертогоэлемента И, второй вход третьего элемента И объединен с вторым управляющим входом блока оперативной памятии подключен к первому тактовому входуустройства, выход третьего элементаИ соединен с суммирующим входом второго счетчика, первые и второй выходыкоторого соединены соответственно содноименными адресными входами блокаоперативной памяти и вторым входомчетвертого элемента И,. первые и вторые информационные входы блока оперативной .памяти соответстввнно являютея вторыми информационными входамиустроиства и подключены к одноименнымвыходам первого счетчика, выходыблока оперативной памяти являютсяинформационными выходами устройства.1615772Составитель М.Никуленков Редактор С .Патрушева Техред Л.Сердюкова Корректор Л,Бескид Заказ 3991 Тираж 442 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д. 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

СмотретьЗаявка

4680343, 18.04.1989

ВОЙСКОВАЯ ЧАСТЬ 11284

НАЗАРОВ ВИТАЛИЙ ВИКТОРОВИЧ, АРХИПОВ АНДРЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G08C 19/28

Метки: адаптивного, аналоговых, код, преобразования, сигналов

Опубликовано: 23.12.1990

Код ссылки

<a href="https://patents.su/5-1615772-ustrojjstvo-dlya-adaptivnogo-preobrazovaniya-analogovykh-signalov-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для адаптивного преобразования аналоговых сигналов в код</a>

Предыдущий патент: Способ передачи дискретной информации и устройство для его осуществления

Следующий патент: Устройство для передачи и приема информации с подвижного объекта

Случайный патент: Способ получения растительного масла из маслосодержащих плодов