Устройство для логического дифференцирования булевых функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

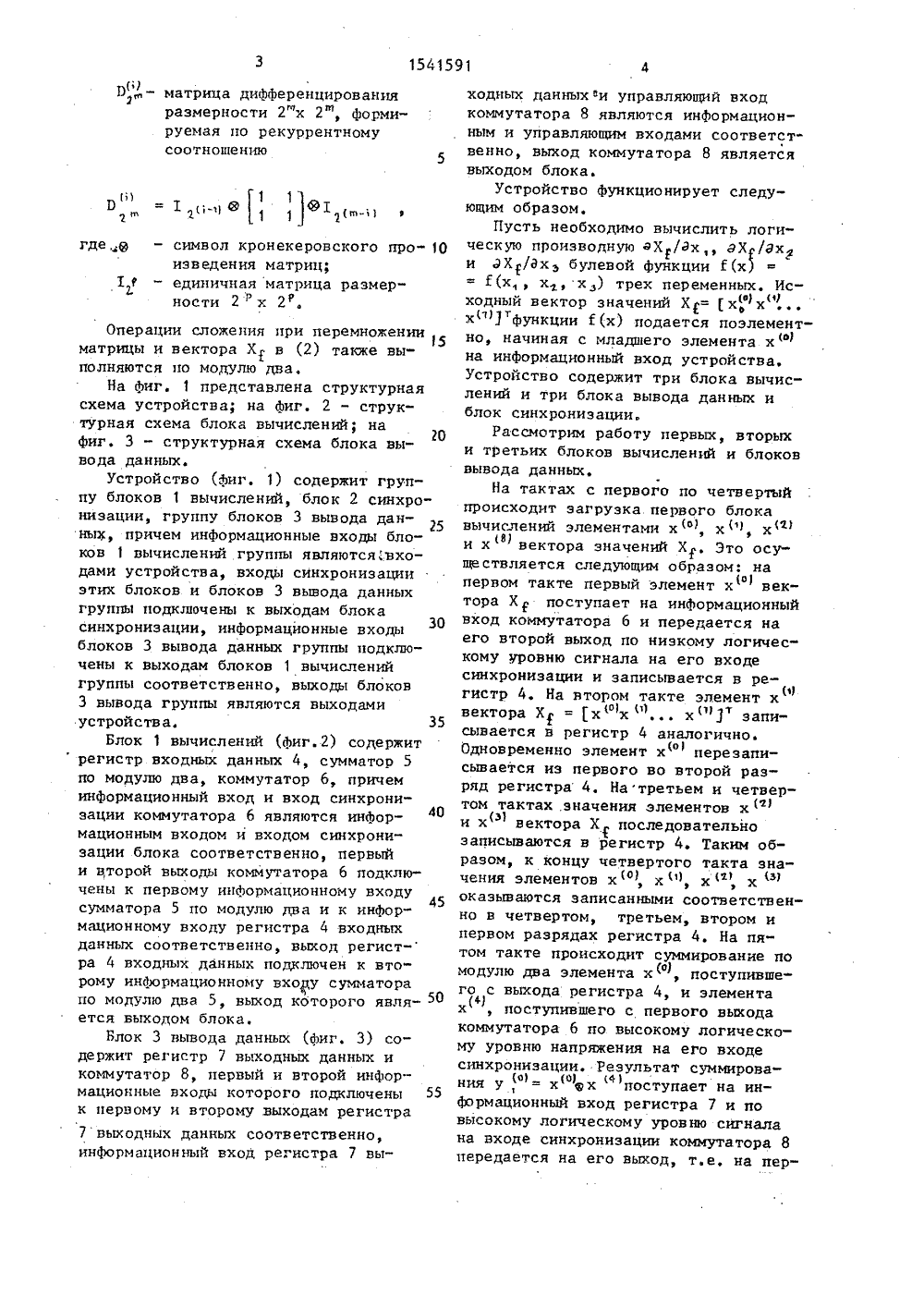

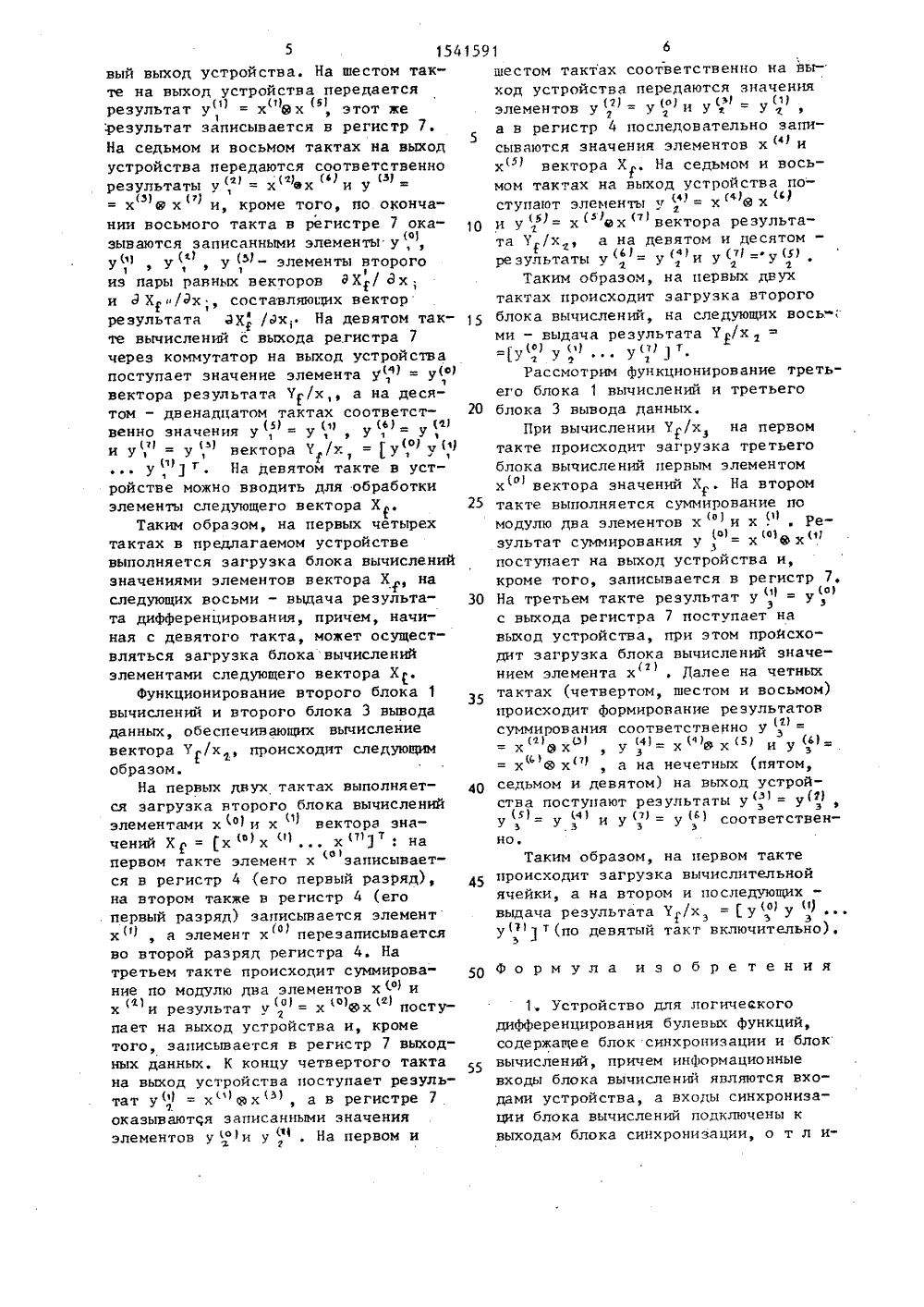

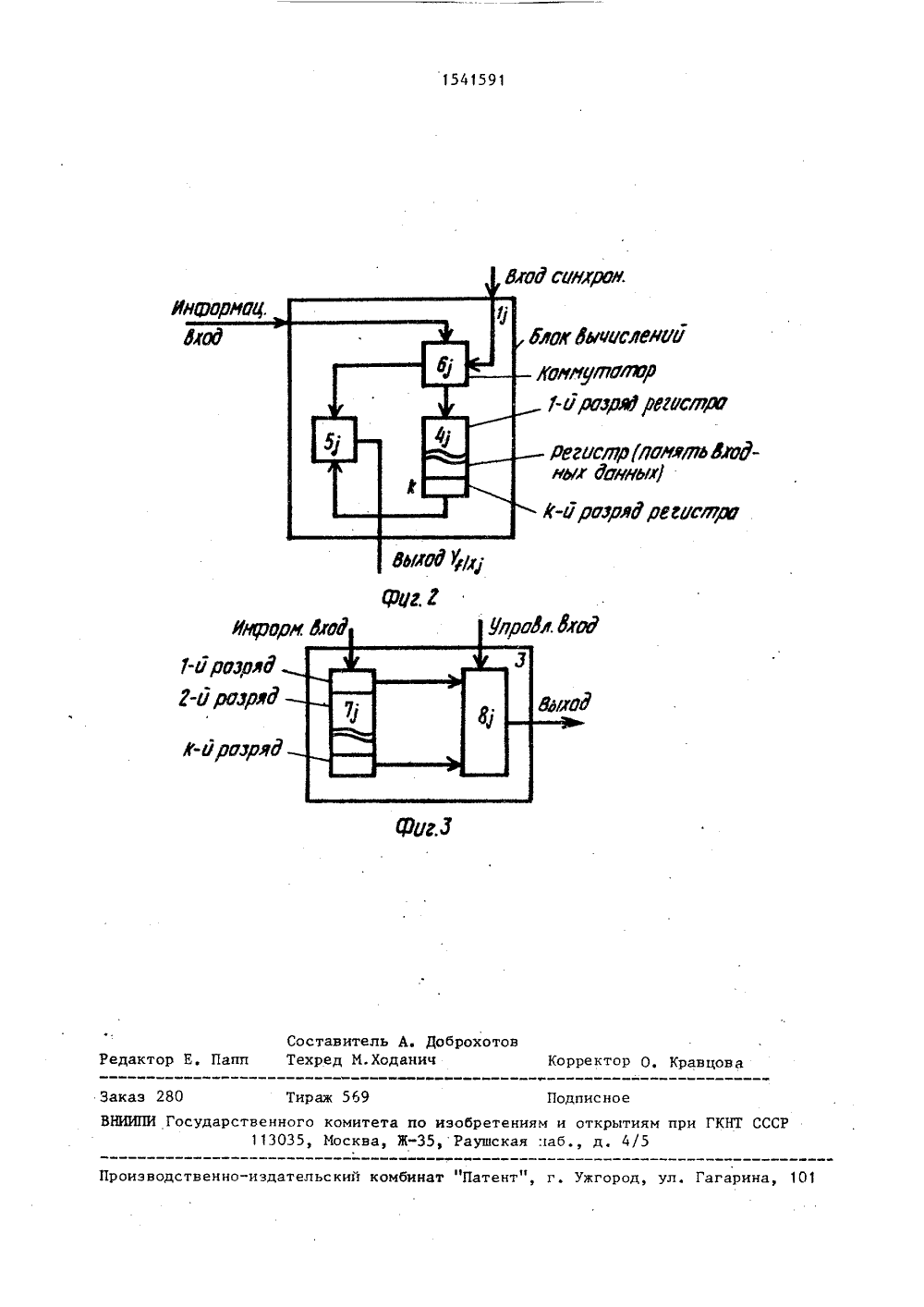

(5 ОБРЕТЕНИЯЕЛЬСТВУ ОПИСА вой вычислительной, технике и можетбыть использовано для аппаратнойподдержки вычислений в системах ав- И томатизированного анализа и синтезацифровых автоматов при их диагностике и контроле, в системах генерирования и синтеза изображений, управления роботами-манипуляторами. В устройство, содержащее блок синхронизации и блок вычислений, с целью повышения быстродействия за счет распараллеливания вычислений значений логической производной булевой функцИи покаждой из переменных, дополнительновведены Мблок вычислений и М блоков вывода данных. 2 з,п.ф-лы, 3 ил ин ничес Е.Н,ШмеркоАвторское свидете Р 1277089, кл, С 06 (54) УСТРОЙСТВО ДЛЯ ДИФФЕРЕНЦИРОВАНИЯ НУЛЕ (57) Устройство отноЮемого изобрете= Изобретение относится к области цифровой вычислительной техники и может быть использовано для аппаратной поддержки вычислений в системах автоматизированного анализа и синтеза цифровых автоматов, при их диагностике и контроле, в системах генерирования и синтеза изображений, управления роботами-манипуляторамиЦель изобретения - повышение быстродействия за счет распараллеливания вычислений значений логической производной булевой функции по каждой из переменных,Суть изобретения заключается в организации однородного процесса вычисления логических производных булевой функции по каждой из переменных на принципах параллельной обработВ основ ожены следуюели функциои устройствческая проиЕ(х) = Е(хных по перем о математиче ки оирования компв целом.водная булево нентов Логкции емен х хной х ( = Гшением ется соотно (х х; определаК(х)дх х,)6у В матричн представляет кой моделью: дЕ (х) ( ах. 1= Гх"х" х(13,ин ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГКНТ СССР АВТОРСКОМУ СВИДЕТ(56) Авторское свидЯф 1168925, кл, Г 06 м виде данная процедура я следующей математичес 1541591)1 1 1ц1, - символ кронекеровского произведения матриц;- единичная матрица размерности 2х 2,гдее Операции сложения при перемноженииматрицы и вектора Х в (2) также выполняются по модулю два,На Фиг. 1 представлена структурнаясхема устройства; на Фиг, 2 - структурная схема блока вычислений; нафиг. 3 - структурная схема блока вывода данных.Устройство (фиг. 1) содержит группу блоков 1 вычислений, блок 2 синхронизации, группу блоков 3 вывода данньп, причем информационные входы блоков 1 вычислений группы являютсявходами устройства, входы синхронизацииэтих блоков и блоков 3 вывода данныхгруппы подключены к выходам блокасинхронизации, информационные входыблоков 3 вывода данных группы подключены к выходам блоков 1 вычисленийгруппы соответственно, выходы блоков3 вывода группы являются выходамиустройства. 35Блок 1 вычислений (Фиг. 2) содержитрегистр входных данных 4, сумматор 5по модулю два, коммутатор 6, причеминформационный вход и вход синхронизации коммутатора 6 являются инфор Омационным входом и входом синхронизации блока соответственно, первыйи второй выходы коммутатора б подключены к первому информационному входу45сумматора 5 по модулю два и к информационному входу регистра 4 входныхданных соответственно, выход регист-ра 4 входных данных подключен к второму информационному вхоуу сумматорапо модулю два 5, выход которого явля Оется выходом блока,Блок 3 вывода данных (фиг. 3) содержит регистр 7 выходных данных икоммутатор 8, первый и второй информационные входа которого подключены 55к первому и второму выходам регистра7 выходных данных соответственно,информационный вход регистра 7 выходных данных фи управляющий входкоммутатора 8 являются информационным и управляющим входами соответственно, выход коммутатора 8 являетсявыходом блока.Устройство функционирует следующим образом,Пусть необходимо вычислить логи"ческую производную Х/дх зХ/дхи ЗХ/дх булевой фуйкции Г(х)= 1(х, х, х) трех переменных, Исходный вектор значений Х=х")х"),.х")3 функции Г(х) подается поэлементно, начиная с младшего элемента х )на информационный вход устройства,Устройство содержит три блока вычислений и три блока вывода данных иблок синхронизации.Рассмотрим работу первых, вторыхи третьих блоков вычислений и блоковвывода данных.На тактах с первого по четвертыйпроисходит загрузка первого блокавычислений элементами х ), х "), х)и х вектора значений Хт. Это осу 3)ществляется следующим образом: напервом такте первый элемент х вектора Х поступает на информационныйвход коммутатора б и передается наего второй выход по низкому логическому уровню сигнала на его входесинхронизации и записывается в регистр 4. На втором такте элемент хвектора Х = х"х 1 х"3" записывается в регистр 4 аналогично.Одновременно элемент х перезапи(осывается из первого во второй разряд регистра 4. На третьем и четвертом тактах .значения элементов хи хф вектора Х последовательноХзаписываются в регистр 4Таким образом к концу четвертого такта значения элементов хо) х с 1 х, сз)оказываются записанными соответственно в четвертом, третьем, втором ипервом разрядах регистра 4. На пятом такте происходит суммирование помодулю два элемента х), поступивше(о)го с выхода регистра 4, и элемента(Фх , поступившего с первого выходакоммутатора 6 по высокому логическому уровню напряжения на его входесинхронизации. Результат суммирования у= х )рхпоступает на информационный вход регистра 7 и повысокому логическому уровню сигналана входе синхронизации коммутатора 8передается на его выход, т.е, на пер1591 6 50 55 5 154 вый выход устройства. На шестом такте на выход устройства передается результат у = х Эх , этот же результат записывается в регистр 7. На седьмом и восьмом тактах на выход устройства передаются соответственно результаты у (,2) = х ( )е х и у= х в х и, кроме того, по окончании восьмого такта в регистре 7 ока(а) зываются записанными элементы у1)Э у(ч, у (, у- элементы второго из пары равных векторов д Х/ а)х; и д Х /дх , составляющих вектор результата )Хф /дх, На девятом такте вычислений с выхода ре,гистра 7 через коммутатор на вьжод устройства поступает значение элемента у 4) у(а вектора результата У/х а на десятом - двенадцатом тактах соответст(2)гу,г. На девятом такте в устройстве можно вводить для обработки элементы следующего вектора ХТаким образом, на первых четырех тактах в предлагаемом устройстве выполняется загрузка блока вычислений значениями элементов вектора Х , на следующих восьми - выдача результата дифференцирования, причем, начиная с девятого такта, может осуществляться загрузка блока вычислений элементами следующего вектора Х.Функционирование второго блока 1 вычислений и второго блока 3 вывода данных, обеспечивающих вычисление вектора У/х , происходит следующим образом.На первых двух тактах выполняется загрузка второго блока вычислений элементами х(а и хвектора зна(чений Х = х(а)х 1 ., х(7)т, насо)первом такте элемент х записывается в регистр 4 (его первый разряд), на втором также в регистр 4 (его первый разряд) записывается элемент х, а элемент х ) перезаписывается во второй разряд регистра 4, На третьем такте происходит суммирование по модулю два элементов х а) и(21х и результат у ) = х)Ех ) поступает на выход устройства и, кроме того, записывается в регистр 7 выходных данных, К концу четвертого такта на выход устройства поступает результат у(, = х") эх, а в регистре 7 оказываются записанными значения элементов у(о)и у", . На первом и 5 10 15 20 25 30 35 40 45 шестом тактах соответственно на вьгход устройства передаются значенияэлементов у (2) = у ф) и у (, = у, ),а в регистр 4 последовательно записываются значения элементов х (ф) их( вектора Х . На седьмом и восьГмом тактах на выход устройства по (с)ступают элементы у ф) = х ( )й хи у(2)= х( ах(7 вектора результата У/х, а на девятом и десятом -результаты у (с: у(7): О)2Таким образом, на первых двухтактах происходит загрузка второгоблока вычислений, на следующих восьми - выдача результата У/х 2у(а) у (1) у (2))Рассмотрим функционирование третьего блока 1 вычислений и третьегоблока 3 вывода данных,При вычислении У/х на первомтакте происходит загрузка третьегоблока вычислений первым элементомх(вектора значений Х . На второмтакте выполняется суммйрование помодулю два элементов х )и х , Ре(а) (а) (цзультат суммирования у ( = х ) х("поступает на выход устройства и,кроме того, записывается в регистр 7.(а)На третьем такте результат у= у зс выхода регистра 7 поступает навыход устройства, при этом пройсходит загрузка блока вычислений значением элемента х . Далее на четныхтактах (четвертом, шестом и восьмом)происходит формирование результатовсуммирования соответственно у (= хх"), а на нечетных (пятом,седьмом и девятом) на выход устройства поступают результаты уу( ф4) у (2) у ( ) соответственно.Таким образом, на нервом тактепроисходит загрузка вычислительнойячейки, а на втором и последующих -выдача результата у,/х = у(а) уу(по девятый такт включительйо),Формула из обре тения 1, устройство для логического дифференцирования булевых функций, содержащее блок синхронизации и блок вычислений, причем информационные входы блока вычислений являются входами устройства, а входы синхронизации блока вычислений подключены к выходам блока синхронизации, о т л и 1541591чающее с я тем, что, с целью повьюения быстродействия за счет распараллеливания вычислений значений логической производной булевой функции по каждой иэ переменных, в5 устройство введены Мблоков вычислений и М блоков вывода данных, где М - количество переменных причем информационные входы блоков вывода данных подключены к выходам блоков вычислений, входы синхронизации блоков вывода данных подключены к выходам блока синхронизации, а выходы блоков вывода данных являются выходами устройства.2, Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок вычислений содержит сумматор по модулю два, регистр входных данных и коммутатор, щ причем первый выход коммутатора соединен с первым информационным входом сумматора по модулю два, второй выход коммутатора подключен к информационному входу регистра входных данных, выход которого подключен к второму информационному входу сумматора по модулю два, причем информационным входом и входом синхронизации блока являются соответственно информационный вход и вход синхронизации коммутатора, а выход сумматора по модулю два - выходом блока.3. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок вывода данных содержит регистр выходных данных и коммутатор, первый и второй информационные входы которого подклю" чены соответственно к первому и второму выходам регистра выходных данных, вход которого является информационным входом блока, а вход синхронизации коммутатора - входом синхронизации блока, выход коммутатора является выходом блока.1541591 конкущалаИроаИ и роюрВ рейцсорю Па Корре к акт Кравцов а Заказ 280ВНИИПИ Госуд Подписно ираж КНТ СССР ственного комитет 113035, Москва,о изобретениям и открытия 35, Раушская лаб., д, 4/5 Производственно-издательский комбинат "Патент ород, ул. Гагарина, 1 1-йюрядГй 7 дОУУ 4-о разряд Составитель А. ДоброхотоТехред М. Ходанич Реосерпокяпв Ва 3 еа данныю)

СмотретьЗаявка

4378636, 12.02.1988

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ЯНУШКЕВИЧ СВЕТЛАНА НИКОЛАЕВНА, ЗАЙЦЕВА ЕЛЕНА НИКОЛАЕВНА, КУХАРЕВ ГЕОРГИЙ АЛЕКСАНДРОВИЧ, ШМЕРКО ВЛАДИМИР ПЕТРОВИЧ

МПК / Метки

МПК: G06F 15/31, G06F 7/00

Метки: булевых, дифференцирования, логического, функций

Опубликовано: 07.02.1990

Код ссылки

<a href="https://patents.su/5-1541591-ustrojjstvo-dlya-logicheskogo-differencirovaniya-bulevykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для логического дифференцирования булевых функций</a>

Предыдущий патент: Устройство для вывода информации

Следующий патент: Устройство для логического дифференцирования и интегрирования булевых функций

Случайный патент: Устройство для разделки мелкой рыбы