Устройство для сбора диагностической информации о формировании адресов переходов микропрограмм

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1290328

Автор: Пшеницын

Текст

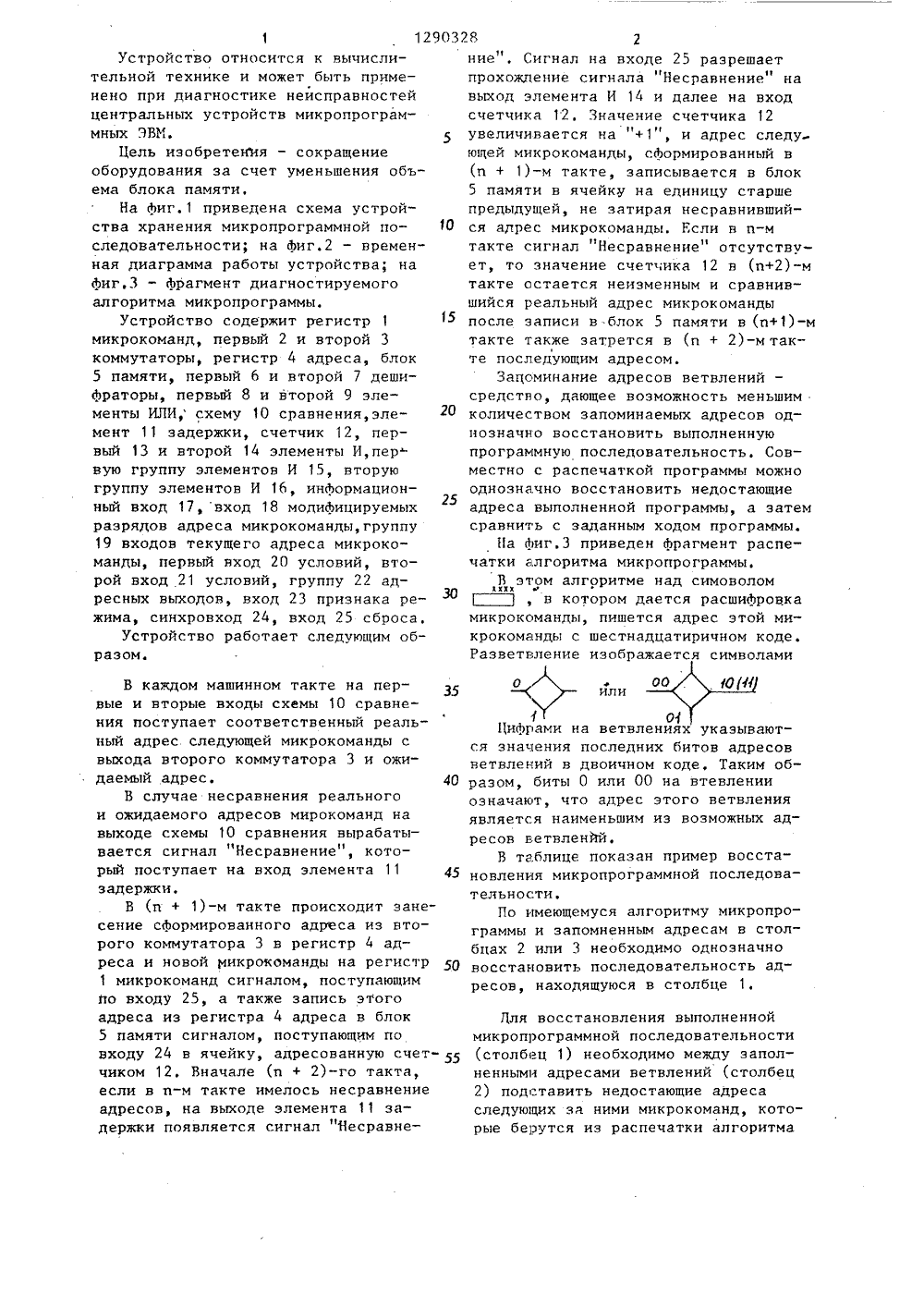

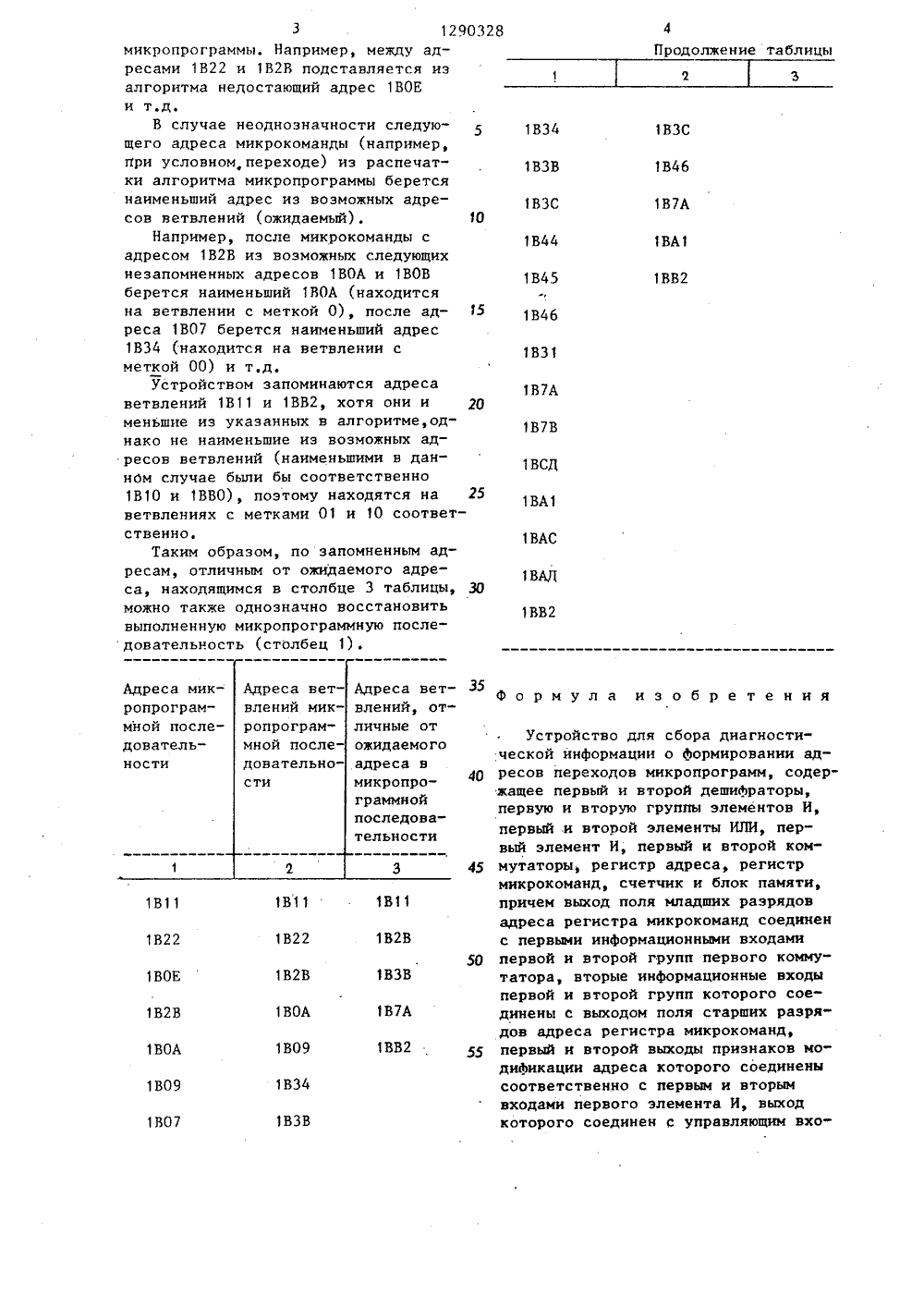

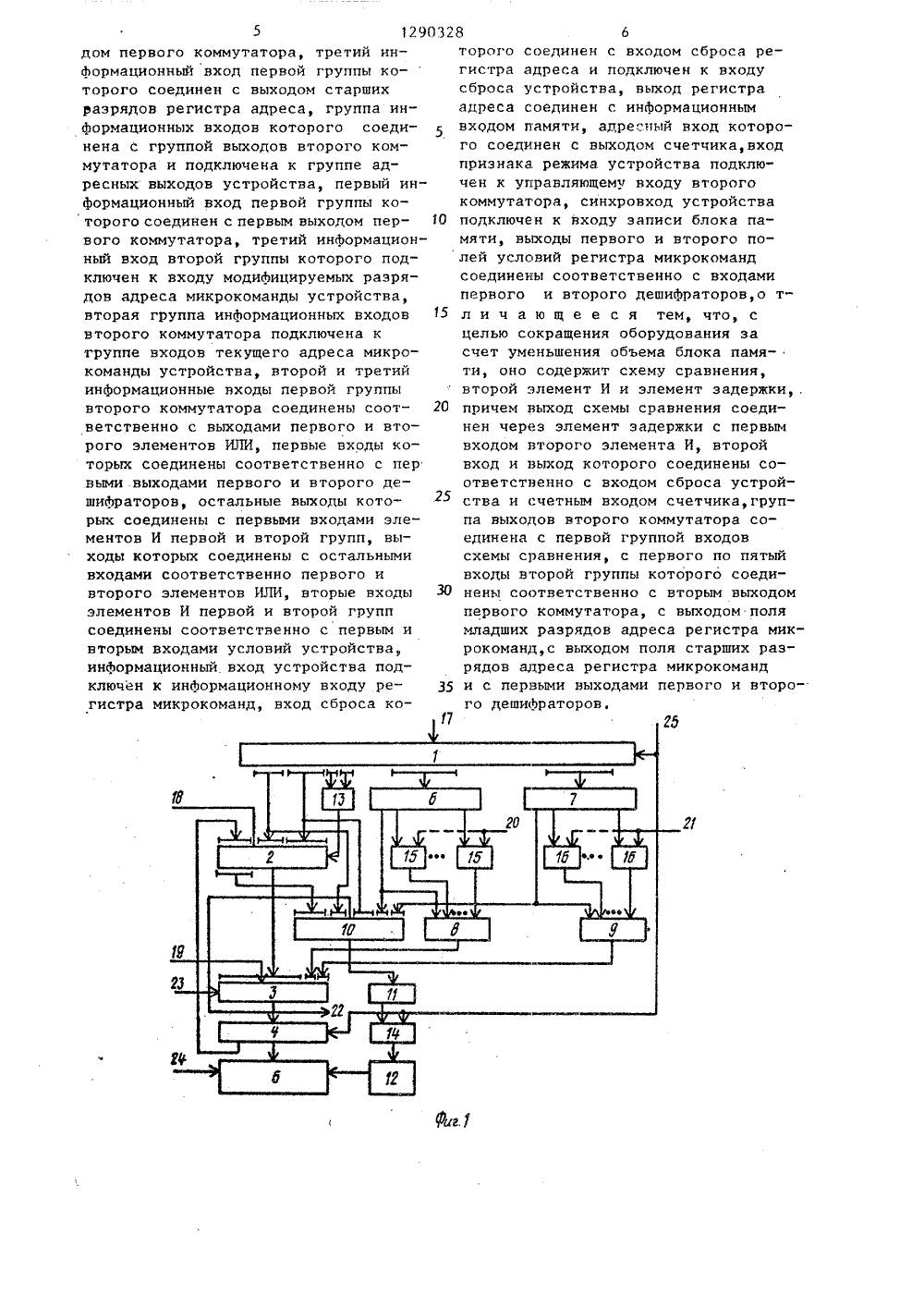

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 1% 011 С 06 Г 11 00 9 22 ОПИСАНИЕ ИЗОБРЕТЕ ВТОРСНОМУ ЕТЕЛЬСТВ ГОСУДАРСТВЕННЬ 1 Й КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ ИОТКРЫТИЙ(54) УСТРОЙСТВО ДЛЯ СБОРА ДИАГНОСТИ ЧЕСКОЙ ИНФОРМАЦИИ О ФОРМИРОВАНИИ АДРЕСОВ ПЕРЕХОДОВ МИКРОПРОГРАММ (57) Изобретение относится к области вычислительной техники и может применяться при диагностике неисправностей центральных устройств мик ропрограммных ЭВМ. Целью изобретения является сокращение оборудования за счет уменьшения объема блока. Устройство содержит схему сравнения, элемент задержки, два элемента И, два элемента ИЛИ, две группы эле-, ментов И, два дешифратора, регистр микрокоманд, два коммутатора, регистр адреса, блок памяти и счетчик. Указанная совокупность признаков позволяет достигнуть цель изобретения.3 ил., 1 табл.1 12Устройство относится к вычислительной технике и может быть применено при диагностике неисправностей центральных устройств микропрограммных ЗВК.Цель изобретенЪя - сокращение оборудования за счет уменьшения объема блока памяти,На фиг.1 приведена схема устройства хранения микропрограммной последовательности; на фиг.2 - временная диаграмма работы устройства; на Лиг.3 - фрагмент диагностируемого алгоритма микропрограммы.Устройство содержит регистр 1 микрокоманд, первый 2 и второй 3 коммутаторы, регистр 4 адреса, блок 5 памяти, первый 6 и второй 7 дешифраторы, первый 8 и второй 9 элементы ИЛИ, схему 1 О сравнения,элемент 11 задержки, счетчик 12, первый 13 и второй 14 элементы И,пер вую группу элементов И 15, вторую группу элементов И 16, информационный вход 17,вход 18 модифицируемых разрядов адреса микрокоманды,группу 19 входов текущего адреса микрокоманды, первый вход 20 условий, второй вход 21 условий, группу 22 адресных выходов, вход 23 признака режима, синхровход 24, вход 25 сбросаУстройство работает следующим образом. 90328 2ние". Сигнал на входе 25 разрешаетпрохождение сигнала "Несравнениен навыход элемента И 14 и далее на входсчетчика 12. Значение счетчика 12увеличивается на "+1", и адрес следующей микрокоманды, сформированный в(и + 1)-м такте, записывается в блок5 памяти в ячейку на единицу старшепредыдущей, не затирая несравнивший ся адрес микрокоманды. Если в п-мтакте сигнал "Несравнение" отсутствует, то значение счетчика 12 в (и+2)-мтакте остается неизменным и сравнившийся реальный адрес микрокомандыпосле записи в блок 5 памяти в (и+1)-мтакте также затрется в (и + 2)-м такте последующим адресом.Зацсминание адресов ветвлений -средство, дающее возможность меньшимколичеством запоминаемых адресов однозначно восстановить выполненнуюпрограммную последовательность, Совместно с распечаткой программы можнооднозначно восстановить недостающиеадреса выполненной программы, а затемсравнить с заданным ходом программы,На фиг.3 приведен фрагмент распечатки алгоритма микропрограммы,В этом алгоритме над симоволомККХК ав котором дается расшифровкамикрокоманды, пишется адрес этой микрокоманды с шестнадцатиричном коде.Разветвление изображается символамитакте на перхемы 10 сравне аждом машинно вторые входы ступает соотв ые ия тственныи реальмикрокоманды статора 3 и ожиадрес следующеида второго коммй адрес. ныи да В случае несравнения реальногои ожидаемого адресов мирокоманд навыходе схемы 10 сравнения вырабатывается сигнал "Несравнение, который поступает на вход элемента 11задержки,В (и + 1)-м такте происходит занесение сформированного адреса из второго коммутатора 3 в регистр 4 адреса и новой микрокоманды на регистр1 микрокоманд сигналом, поступающимпо входу 25, а также запись этогоадреса из регистра 4 адреса в блок5 памяти сигналом, поступающим повходу 24 в ячейку, адресованную счетчиком 12. Вначале (и + 2)-го такта,если в и-м такте имелось несравнениеадресов, на выходе элемента 11 задержки появляется сигнал "Яесравне Фили на ветвлениях последних би 1 ийра в двоичном кодты 0 или 00 на что адрес этог ветвления можных ад ляется наименьшим из ресов ветвленйи,В таблице показан пример восстановления микропрограммной последова ельности,По имеющемуся алгоритм раммы и запомненным адр цах 2 или 3 необходимо осстановить последовате есов, находящуюся в сто у микропросам в столднозначноьность адбце 1,ля восстановлени ыполненнои икропрограм столбец 1) ой последовательност еобходимо ами ветвл ежду заполий (столбец ие адреса команд, кото ки алгоритма недостаю ими микр з расп ся значеветвлени0 разом, бозначают ненными адр 2) подстави следующих з рые берутся укаэываютов адресовТаким об- тевлении3 1290328 микропрограммы, Например, между адресами 1 В 22 и 1 В 2 В подставляется изалгоритма недостающий адрес 1 ВОЕи т,д.В случае неоднозначности следую 1 В 34 щего адреса микрокоманды (например,при условном, переходе) из распечатки алгоритма микропрограммы беретсянаименьший адрес из возможных адресов ветвлений (ожидаемый). 1 ОНапример, после микрокоманды с 1 В 44 адресом 1 В 2 В из возможных следующихнезапомненных адресов 1 ВОА и 1 ВОВ 1 В 45 берется наименьший 1 ВОА (находитсяна ветвлении с меткой 0), после ад 1 В 46 реса 1 В 07 берется наименьший адрес1 В 34 (находится на ветвлении с1 В 31 меткой 00) и т.д.Устройством запоминаются адресаветвлений 1 В 11 и 1 ВВ 2, хотя они и 20меньшие из указанных в алгоритме,од В 7 В нако не наименьшие из возможных адресов ветвлений (наименьшими в данном случае были бы соответственно1 В 10 и 1 ВВО), поэтому находятся на 25ветвлениях с метками 01 и 10 соответПродолжение таблицы 1 ВЗС 1 В 46 1 ВЗС 1 В 7 АВА 1 1 ВВ 2 1 В 7 А 1 ВСД ственно,Таким образом, по запомненным адресам, отличным от ожидаемого адреса, находящимся в столбце 3 таблицы, 30 можно также однозначно восстановить выполненную микропрограммную после довательность (столбец 1). 1 ВАС 1 ВАц 1 ВВ 2 35 Формула изобретения Устройство для сбора диагностической информации о формировании ад 4 р ресов переходов микропрограмм, содержащее первый и второй дешифраторы,первую и вторую группы элементов И,первый и второй элементы ИЛИ, первый элемент И, первый и второй ком мутаторы, регистр адреса, регистрмикрокоманд, счетчик и блок памяти,причем выход поля младших разрядовадреса регистра микрокоманд соединенс первыми информационными входами 50 первой и второй групп первого коммутатора, вторые информационные входыпервой и второй групп которого соединены с выходом поля старших разрядов адреса регистра микрокоманд, 55 первый и второй выходы признаков модификации адреса которого соединенысоответственно с первым и вторымвходами первого элемента И, выходкоторого соединен с управляющим вхоВ 111 В 1 В 11 2 В 1 В 2 1 В 22 1 ВЗВ 1 В 2 1 ВОЕ 1 В В 2 В 2 1 В 1 В 1 В 09 ЗВ129032 дом первого коммутатора, третий информационный вход первой группы которого соединен с выходом старших разрядов регистра адреса, группа информационных входов которого соединена с группой выходов второго коммутатора и подключена к группе адресных выходов устройства, первый информационный вход первой группы ко торого соединен с первым выходом пер вого коммутатора, третий информационный вход второй группы которого подключен к входу модифицируемых разрядов адреса микрокоманды устройства, вторая группа информационных входов 5 второго коммутатора подключена к труппе входов текущего адреса микро- команды устройства, второй и третий информационные входы первой группы второго коммутатора соединены соот ветственно с выходами первого и второго элементов ИЛИ, первые входы которых соединены соответственно с пер выми выходами первого и второго дешифраторов, остальные выходы которых соединены с первыми входами элементов И первой и второй групп, выходы которых соединены с остальными входами соответственно первого и второго элементов ИЛИ, вторые входы ЗО элементов И первой и второй групп соединены соответственно с первым и вторым входами условий устройства информационный вход устройства подключен к информационному входу ре гистра микрокоманд, вход сброса коУ 7 8 6торого соединен с входом сброса регистра адреса и подключен к входу сброса устройства, выход регистра адреса соединен с информационным входом памяти, адресный вход которого соединен с выходом счетчика, вход признака. режима. устройства подключен к управляющему входу второго коммутатора, синхровход устройства подключен к входу записи блока памяти, выходы первого и второго полей условий регистра микрокоманд соединены соответственно с входами первого и второго дешифраторов,о тл и ч а ю щ е е с я тем, что, сцелью сокращения оборудования засчет уменьшения объема блока памяти, оно содержит схему сравнения,второй элемент И и элемент задержки,.причем вьгход схемы сравнения соединен через элемент задержки с первымвходом второго элемента И, второйвход и выход которого соединены соответственно с входом сброса устройства и счетным входом счетчика, группа выходов второго коммутатора соединена с первой группой входовсхемы сравнения, с первого по пятыйвходы второй группы которого соединены соответственно с вторым выходомпервого коммутатора, с выходом полямладших разрядов адреса регистра микрокоманд,с выходом поля старших разрядов адреса регистра микрокоманди с первыми выходами первого и второго дешифраторов,

СмотретьЗаявка

3704009, 19.12.1983

ПРЕДПРИЯТИЕ ПЯ Р-6380

ПШЕНИЦЫН ЮРИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 11/00

Метки: адресов, диагностической, информации, микропрограмм, переходов, сбора, формировании

Опубликовано: 15.02.1987

Код ссылки

<a href="https://patents.su/5-1290328-ustrojjstvo-dlya-sbora-diagnosticheskojj-informacii-o-formirovanii-adresov-perekhodov-mikroprogramm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сбора диагностической информации о формировании адресов переходов микропрограмм</a>

Предыдущий патент: Устройство формирования сигнала прерывания

Следующий патент: Устройство для отладки программно-аппаратных блоков

Случайный патент: Устройство для пространственного отклонения светового пучка