Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

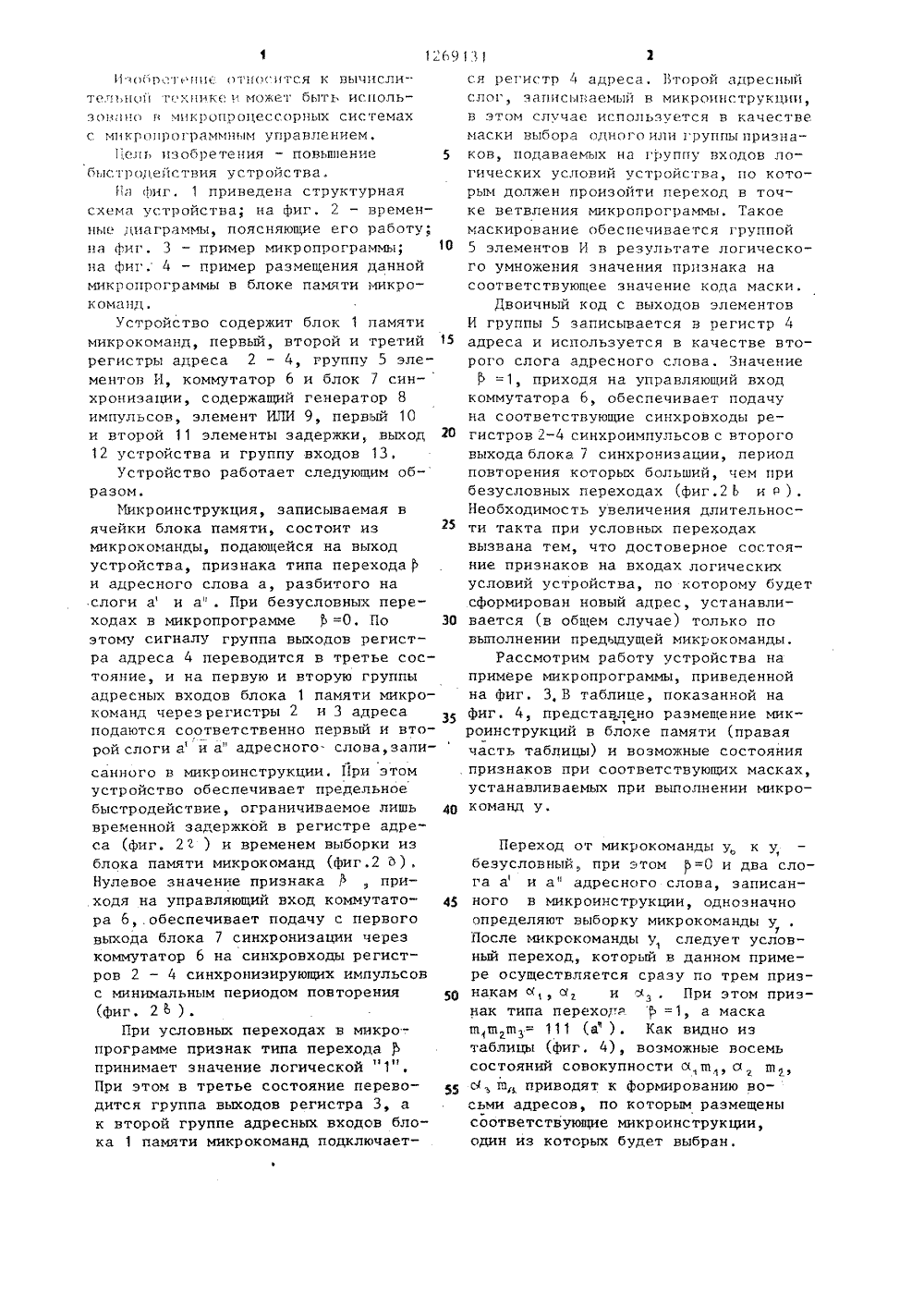

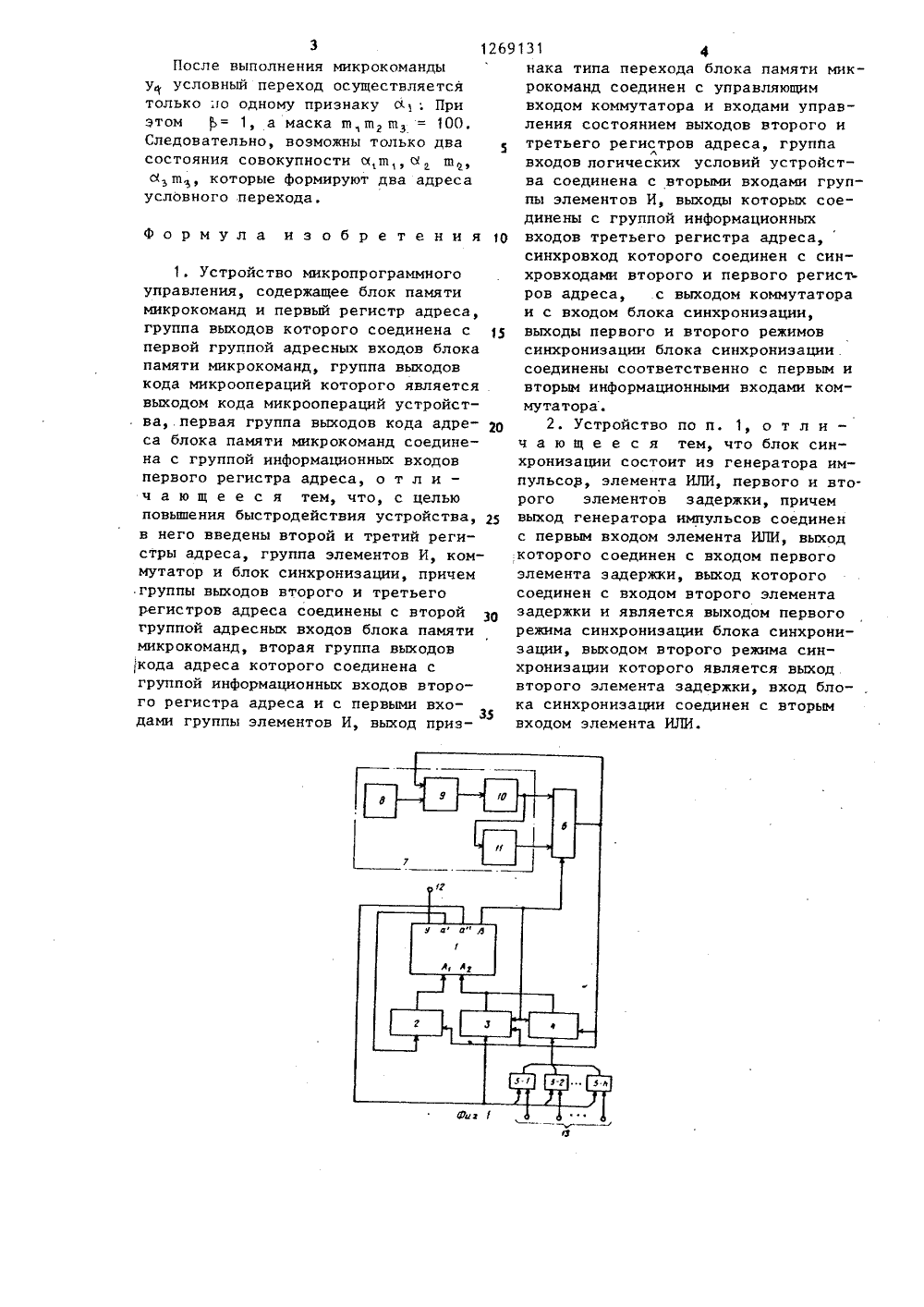

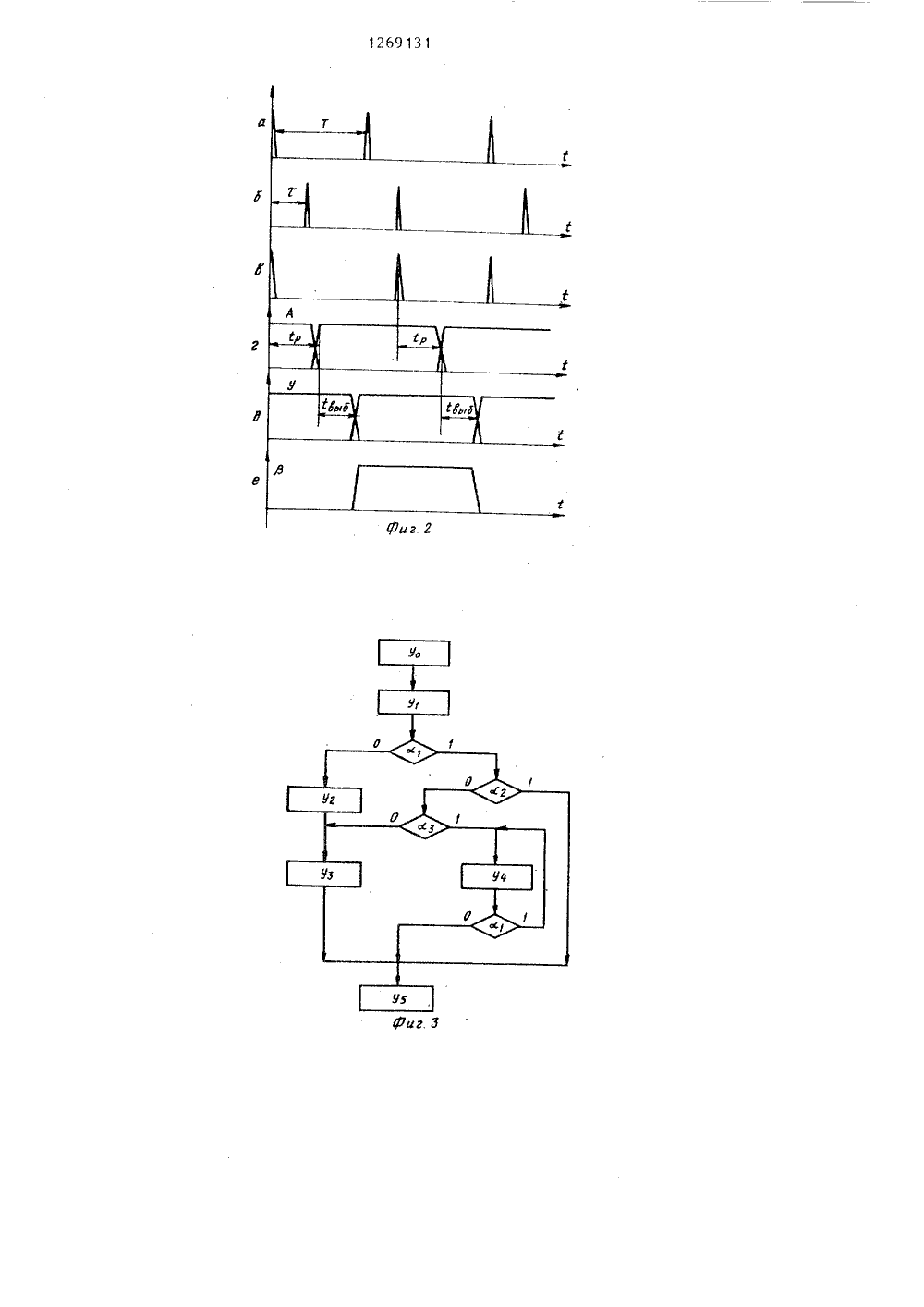

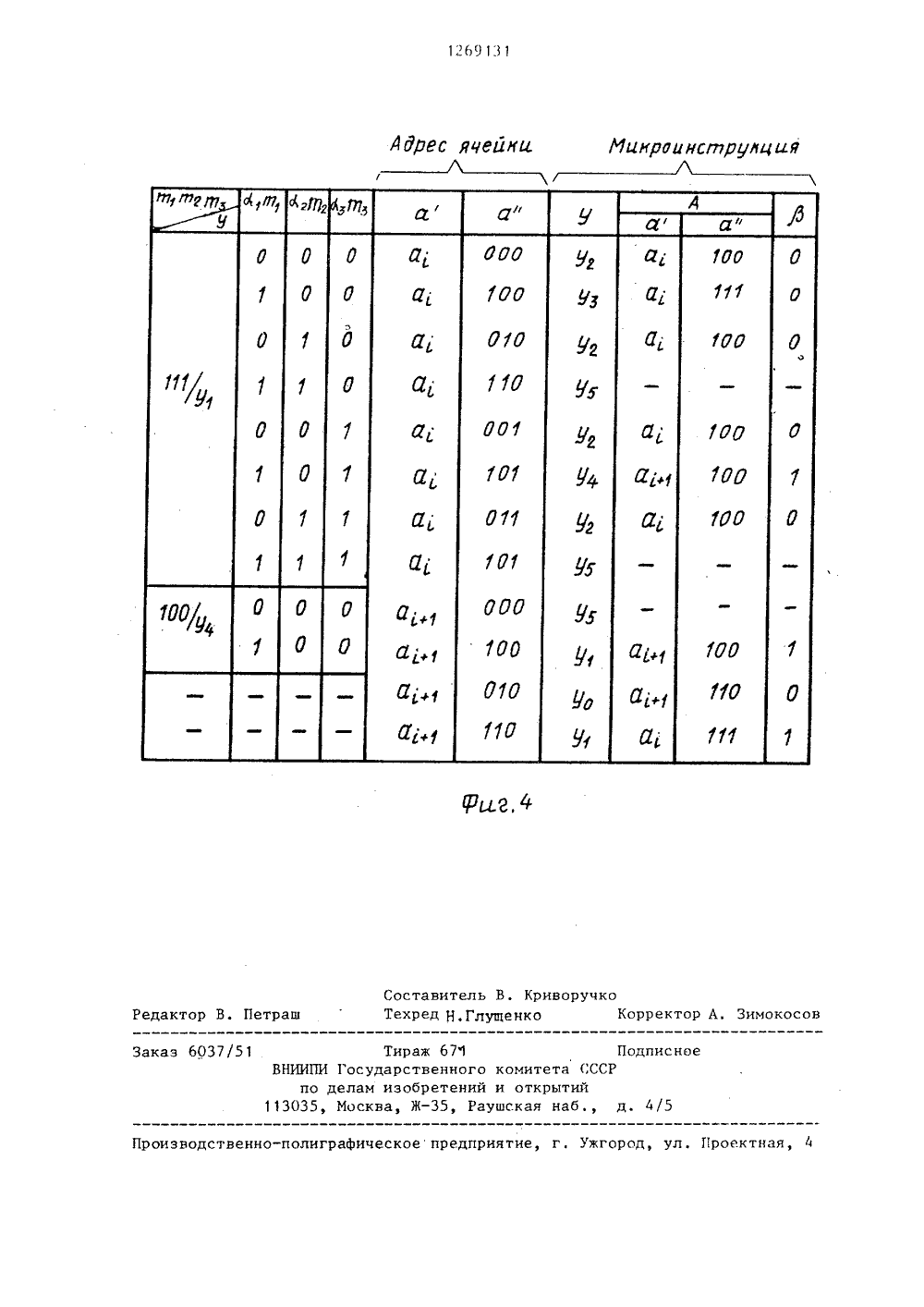

,126913 19) 6 Р 9/2 4 ОЛИСАНИЕ ИЗОБРЕТЕНИЯ ВТОРСНОМУ С 8 ИД ЬС СТВО МИКРОПРОГРАММН-Л.: Ма рис. 1 328 ф р Структ1979,10.1 м ил ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ, 11.86.В. ГалкПопов1.325(0йоров Сура ЭВМ.314,же, с. ение относится к вычисхнике и может быть исоцессорных сисммным управлени - повышениеойства, Устройстмяти микрокоманд,группу элеменблок синхронизаия достигаетсяой обработки несусловий в устройпользовано в микропртемах с микропрограем. Цель изобретениябыстродействия устрво содержит блок патри регистра адресатов И, коммутатор иции. Цель изобретенИ э о(1 т 1;.те 111 с о Т 11 ог ится к вычислительной технике и может быть использовано н микропроцессорных системах с мнкро 11 рограммнь 1 м управлением,1;е 11 изобретения - повьпиение 5 быстродействия устройстваНа фиг. 1 приведена структурная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу; на фиг, 3 - пример микропрограммы; 10 на фиг, 4 - пример размещения данной микропрограммы в блоке памяти микрокоманд.Устройство содержит блок 1 памятимикрокоманд, первый, второй и третий 15регистры адреса 2 - 4, группу 5 элементов И, коммутатор 6 и блок 7 син-хронизации, содержащий генератор 8импульсов, элемент ИЛИ 9, первый 10и второй 11 элементы задержки, выход 2012 устройства и группу входов 13.Устройство работает следующим образом,Микроинструкция, записываемая вячейки блока памяти, состоит измикрокоманды, подающейся на выходустройства, признака типа перехода Ри адресного слова а, разбитого наслоги а и а. При безусловных переходах в микропрограмме р =О. По 30этому сигналу группа выходов регистра адреса 4 переводится в третье состояние, и на первую и вторую группыадресных входов блока 1 памяти микрокоманд через регистры 2 и 3 адресаподаются соответственно первый и второй слоги а и а" адресного- слова,записанного в микроинструкции, При этомустройство обеспечивает предельноебыстродействие, ограничиваемое лишьвременной задержкой в регистре адреса (фиг. 2 ) и временем выборки изблока памяти микрокоманд (Фиг.2 д ) .Нулевое значение признака, приходя на управляющий вход коммутатора 6,.обеспечивает подачу с первоговыхода блока 7 синхронизации черезкоммутатор 6 на синхровходы регистров 2 - 4 синхронизирующих импульсовс минимальным периодом повторения(фиг. 2 Ь ),При условных переходах в микропрограмме признак типа перехода Рпринимает значение логической " 1",При этом в третье состояние перево- удится группа выходов регистра 3, ак второй группе адресных входов блока 1 памяти микрокоманд подклкчается регистр 4 адреса. Второй адресный слог, записки;аемый в микроинструкции, в этом случае используется в качестве маски выбора одного или группы признаков, подаваемых на группу входов ло - гических условий устройства, по которым должен произойти переход в точке ветвления микропрограммы. Такое маскирование обеспечивается группой 5 элементов И в результате логического умножения значения признака на соответствующее значение кода маски,Двоичный код с выходов элементов И группы 5 записывается в регистр 4 адреса и используется в качестве второго слога адресного слова. Значение=1, приходя на управляющий вход коммутатора 6, обеспечивает подачу на соответствующие синхровходы регистров 2-4 синхроимпульсов с второго выхода блока 7 синхронизации, период повторения которых больший, чем при безусловных переходах (фиг.2 5 и Р ), Необходимость увеличения длительности такта при условных переходах вызвана тем, что достоверное состояние признаков на входах логических условий устройства, по которому будет сформирован новый адрес, устанавливается (в общем случае) только по выполнении предыдущей микрокоманды.Рассмотрим работу устройства на примере микропрограммы, приведенной на Фиг. 3, В таблице, показанной на Фиг. 4, прецставлено размещение микроинструкций в блоке памяти (правая часть таблицы) и возможные состояния признаков при соответствующих масках, устанавливаемых при выполнении микро- команд у. Переход от микрокоманды ук у безусловный, при этом р =О и два слога а и а" адресного слова, записанного в микроинструкции, однозначно определяют выборку микрокоманды у После микрокоманды у следует условный переход, который в данном примере осуществляется сразу по трем признакам б б, и, При этом признак типа перехода Р =1, а маска тптп ш = 111 (а" ). Как видно из таблицы (фиг. 4), возможные восемь состояний совокупности с 1.,ш о 1 ш о 1, та, приводят к Формированию восьми адресов, по которым размещены соответствующие микроинструкции, один из которых будет выбран.1269После выполнения микрокоманды у условный переход осуществляется только по одному признаку й; При этом = 1, а маска втп тп = 100.Следовательно, возможны только два состояния совокупности и,т бт, ов, которые формируют два адреса условного перехода.Формула изобретенияО1. Устройство микропрограммного управления, содержащее блок памяти микрокоманд и первый регистр адреса, группа выходов которого соединена с 15 первой группой адресных входов блока памяти микрокоманд, группа выходов кода микроопераций которого является выходом кода микроопераций устройства,.первая группа выходов кода адре- ро са блока памяти микрокоманд соединена с группой информационных входов первого регистра адреса, о т л и - ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, д в него введены второй и третий регистры адреса, группа элементов И, коммутатор и блок синхронизации, причем ,группы выходов второго и третьего регистров адреса соединены с второй ЗО группой адресных входов блока памяти микрокоманд, вторая группа выходов кода адреса которого соединена с группой информационных входов второго регистра адреса и с первыми входами группы элементов И, выход приз 131 4нака типа перехода блока памяти микрокоманд соединен с управляющим входом коммутатора и входами управления состоянием выходов второго и третьего регистров адреса, группалвходов логических условий устройства соединена с вторыми входами группы элементов И, выходы которых соединены с группой информационных входов третьего регистра адреса, синхровход которого соединен с синхровходами второго и первого регистров адреса, с выходом коммутатора и с входом блока синхронизации, выходы первого и второго режимов синхронизации блока синхронизации. соединены соответственно с первым и вторым информационными входами коммутатора.2. Устройство по п. 1, о т л и - ч а ю щ е е с я тем, что блок синхронизации состоит из генератора импульсов, элемента ИЛИ, первого и второго элементов задержки, причем выход генератора импульсов соединен с первым входом элемента ИЛИ, выход которого соединен с входом первого элемента задержки, выход которого соединен с входом второго элемента задержки и является выходом первого режима синхронизации блока синхронизации, выходом второго режима синхронизации которого является выход второго элемента задержки, вход блока синхронизации соединен с вторым входом элемента ИЛИ.А прес ииейни Иинрсансщрунци й Риг. 4 Составитель В. КриворучкоТехред Н,Глущенко Корректор А. Зимокосов Редактор В. Петраш Тираж 671 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

3896890, 07.05.1985

ОПЫТНО-КОНСТРУКТОРСКОЕ БЮРО НОВГОРОДСКОГО ПОЛИТЕХНИЧЕСКОГО ИНСТИТУТА

ГАЛКИН ГЕННАДИЙ ВЛАДИМИРОВИЧ, МИНУТИН ЛЕОНИД ДМИТРИЕВИЧ, ПОПОВ ОЛЕГ ОЛЕГОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 07.11.1986

Код ссылки

<a href="https://patents.su/5-1269131-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Вычислительное устройство для реализации логических функций

Следующий патент: Двухвходовое устройство приоритета

Случайный патент: Гидростатический нивелир