Система управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1234810

Авторы: Михальченок, Новиков, Сидорович, Суслов

Текст

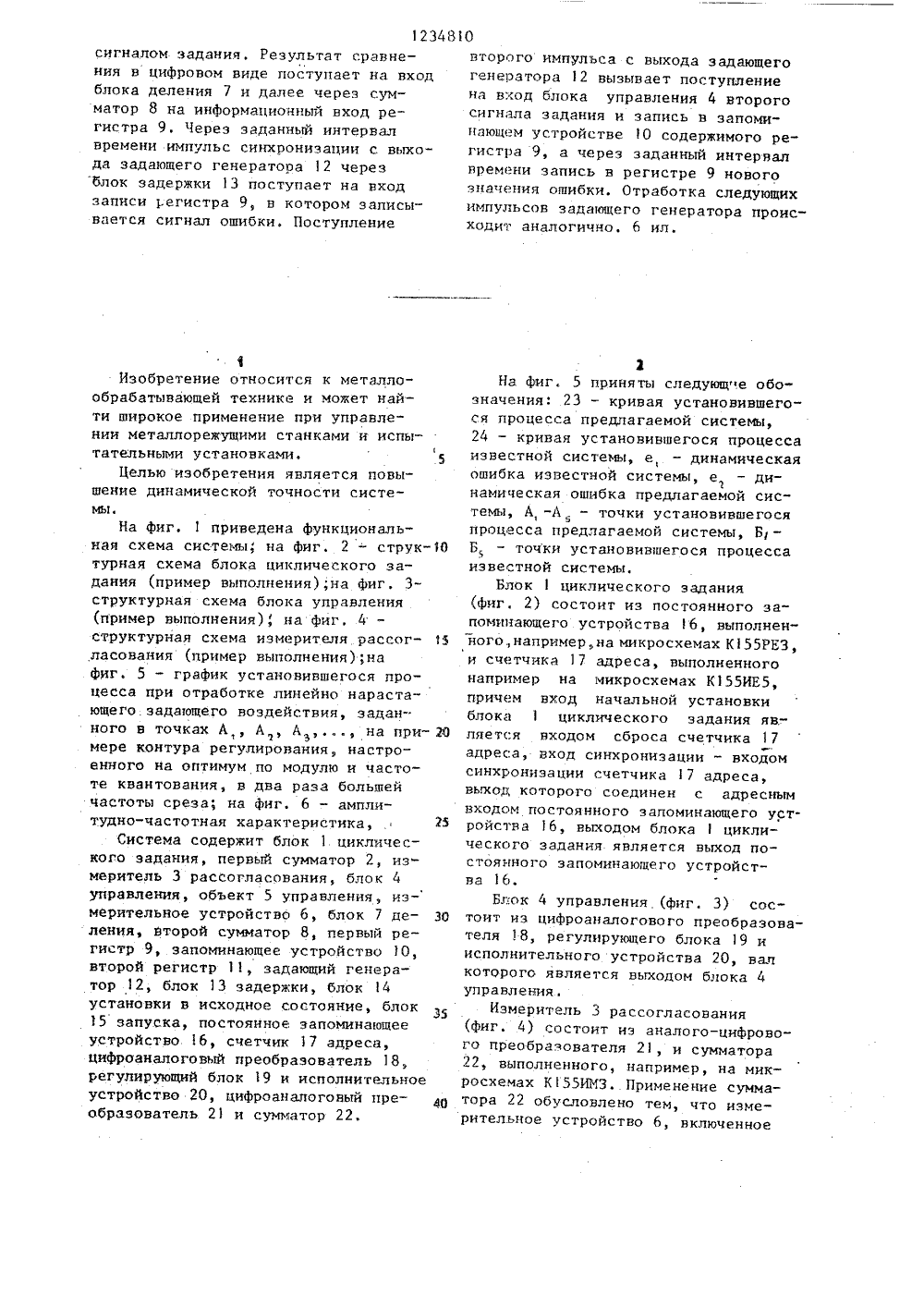

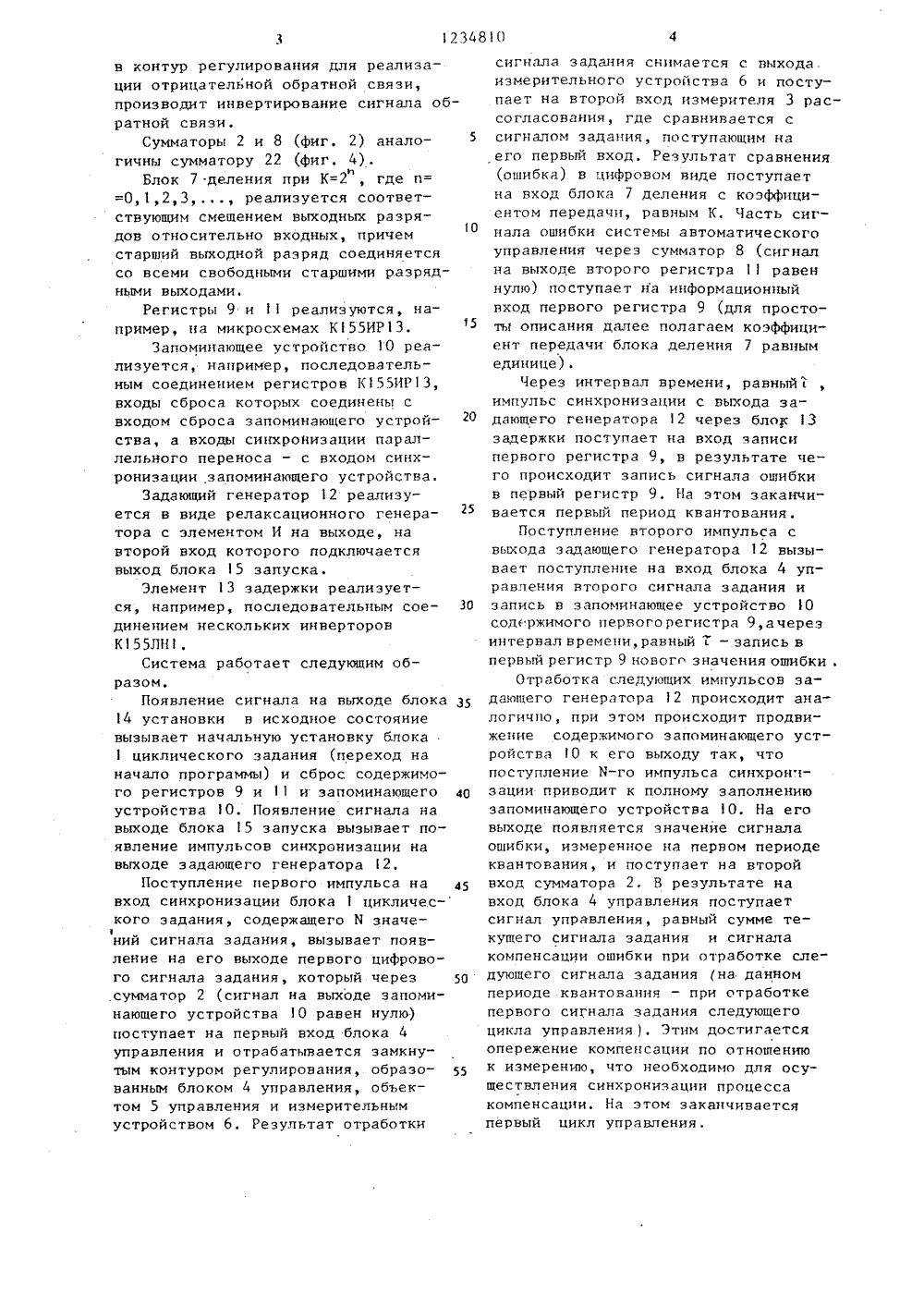

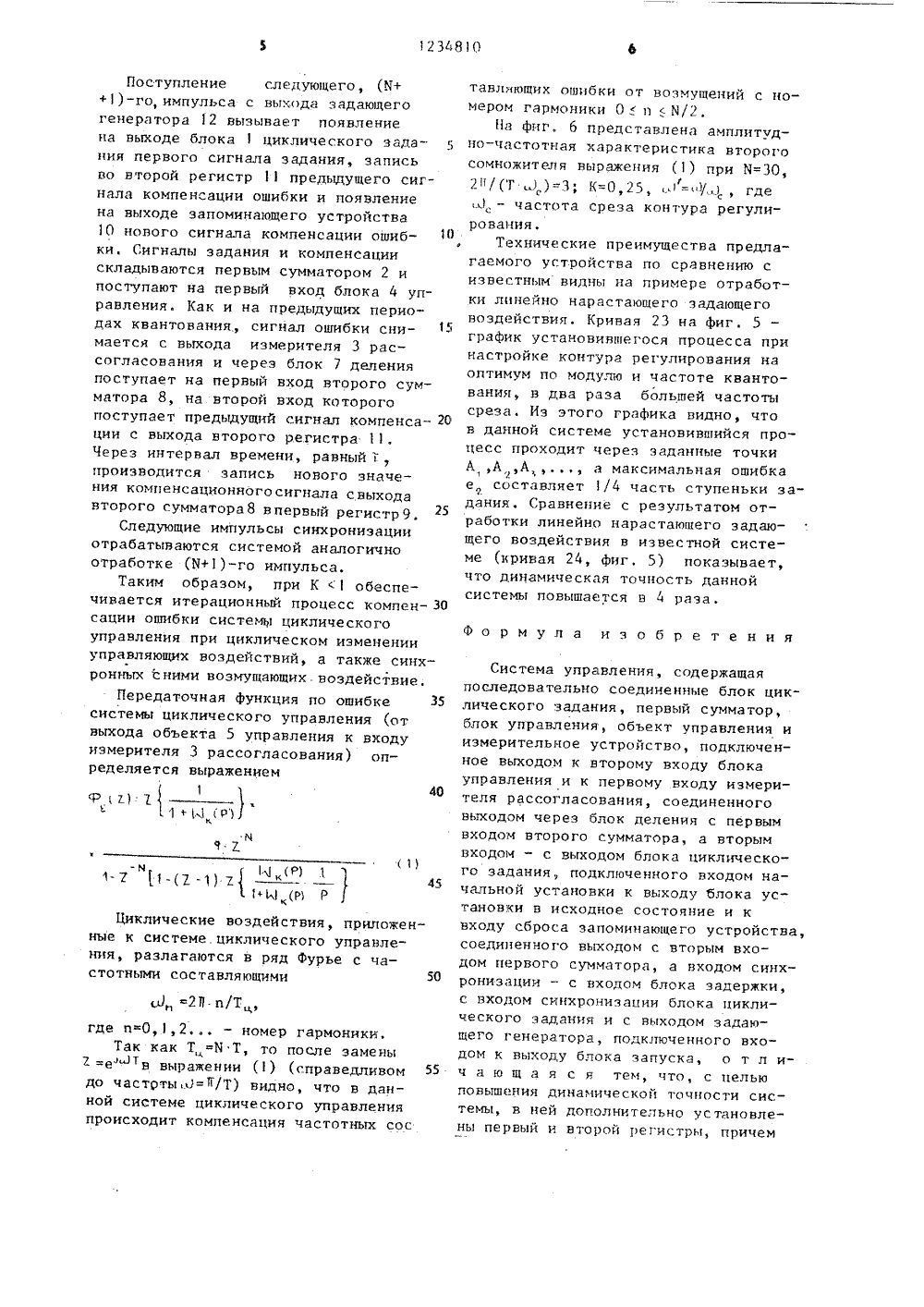

(54) СИСТЕМА У (57) Изобретен ти металлообра для работы в уменаощихся упр рх воздействий е относится к облзсоткн, предназначено ловиях циклически извляющих и возмущаю- и может быть испольСУДАРСТВЕКНЫЙ КОМИТЕТ ССС ПО ДЕЛ ".М ИЗОБРЕТЕНИЙ И ОТНРЬ 1 Т(56) Соломенцев 1 О.М. и дное управление технологицессами. - М.: Машинострс. 113-123.Патент Великобриткл. С 05 В 13/02, оп зовано при построении прециэчонныхсистем программного управления металлорежущими станками и испытательными установками. Повьппение динамической точности системы при отработке циклических управляющих воздействий достигается за счет настройкиконтура регулирования на оптимум помодулю и частоте квантования. Поступление первого импульса на входсинхронизации блока циклическогозадания 1 вызывает появление на еговыходе первого цифрового сигнала задания, который через сумматор 2 поступает на первый вход блока управления 4 и отрабатывается замкнутымконтуром регулирования, образованнымблоком управления 4, объектом управления 5 и измерительным устройством6, Выходной сигнал последнего поступает на второй вход измерителя рассогласования 3, где сравнивается с1234810 сигналом задания. Результат сравнения в цифровом виде поступает на входблока деления 7 и далее через сумматор 8 на информационный вход регистра 9. Через заданный интервалвремени импульс синхронизации с выхода задающего генератора 12 черезблок задержки 13 поступает на входзаписи 1.егистра 9, в котором записывается сигнал ошибки, Поступление Изобретение относится к металлообрабатывающей технике и может найти широкое применение при управлении металлорежущими станками и испытательными установками, 5Целью изобретения является повышение динамической точности системы вНа фиг. 1 приведена функциональная схема системы; на фиг. 2 - структурная схема блока циклического задания (пример выполнения);на фиг. 3- структурная схема блока управления (пример выполнения), на фиг. 4 структурная схема измерителя рассог ласования (пример выполнения);на фиг, 5 - график установившегося процесса при отработке линейно нарастающего.задающего воздействия, заданного в точках А А Ана при Э мере контура регулирования, настроенного на оптимум по модулю и частоте квантования, в два раза большей частоты среза; на фиг. 6 - амплитудно-частотная характеристика 25Система содержит блок 1 циклического задания, первый сумматор 2, измеритель 3 рассогласования, блок управления, объект 5 управления, из- мерительное устройство 6, блок 7 де- Зо ления, второй сумматор 8, первый регистр 9, запоминающее устройство 10, второй регистр 11, задающий генератор 12, блок 13 задержки, блок 14 установки в исходное состояние, блок 15 запуска, постоянное запоминающее устройство 16, счетчик 17 адреса, цифроаналоговый преобразователь 18 регулирующий блок 19 и исполнительное устройство 20, цифроаналоговый преобразователь 21 и сумматор 22. второго импульса с выхода задающегогенератора 12 вызывает поступлениена вход блока управления 4 второгосигнала задания и запись в запоминающем устройстве О содержимого регистра 9, а через заданный интервалвремени запись в регистре 9 новогозначения ошибки. Отработка следующихимпульсов задающего генератора происходит аналогично. 6 ил. аНа фиг. 5 приняты следующ 1 е обозначения: 23 - кривая установившегося процесса предлагаемой системы, 24 - кривая установившегося процесса известной систем, е, - динамическая ошибка известной системы, е - динамическая ошибка предлагаемой системы, А, -А, - точки установившегося процесса предлагаемой системы, Б - Б. - точки установившегося процесса известной системы.Блок 1 циклического задания (фиг. 2) состоит из постоянного запоминающего устройства 6, выполненного, например, на микросхемах К 155 РЕЗ, и счетчика 17 адреса, выполненного например на микросхемах К 155 ИЕ 5, причем вход начальной установки блокациклического задания является входом сброса счетчика 17 адреса, вход синхронизации - входом синхронизации счетчика 7 адреса, выход которого соединен с адресным входом постоянного запоминающего устройства 6, выходом блокациклического задания является выход постоянного запоминающего устройства 16.Бгок 4 управления (фиг. 3) состоит иэ цифроаналогового преобразователя 18, регулирующего блока 19 и исполнительного устройства 20, вал которого является выходом блока 4 управления.Измеритель 3 рассогласования (фиг. 4) состоит из аналого-цифрового преобразователя 21, и сумматора 2, выполненного, например, на микросхемах К 55 ИИЗ. Применение сумматора 22 обусловлено тем, что измерительное устройство 6, включенное1 О в контур регулирования для реализации отрицательной обратной связи,производит инвертирование сигнала обратной связи,Сумматоры 2 и 8 (фиг. 2) аналогичны сумматору 22 (фиг. 4).Блок 7 деления при К=2 , где и==0,1,2,3 реализуется соответствующим смещением выходных разрядов относительно входных, причемстарший выходной разряд соединяетсясо всеми свободными старшими разрядными выходами.Регистры 9 и 11 реализуются, например, на микросхемах К 55 ИР 13.Запоминающее устройство 10 реализуется, например, последовательным соединением регистров К 155 ИР 13,входы сброса которых соединены свходом сброса запоминающего устрой -стна, а входы синхронизации параллельного переноса - с входом синхронизации запоминающего устройства.Задаюший генератор 12 реализуется в виде релаксационного генератора с элементом И на выходе, навторой вход которого подключаетсявыход блока 15 запуска.Элемент 13 задержки реализуется, например, последовательным соединением нескольких инверторовК 155 ЛН 1.Система работает следующим образом,Появление сигнала на выходе блока З 514 установки в исходное состояниевызывает начальную установку блока1 циклического задания (переход наначало программы) и сброс содержимого регистров 9 и 11 и эапоминаюшего 40устройства 10. Появление сигнала навыходе блока 15 запуска вызывает появление импульсов синхронизации навыходе задающего генератора 2.Поступление первого импульса на 45вход синхронизации блока 1 цикличес-кого задания, содержащего И значе 1ний сигнала задания, вызывает появление на его выходе первого цифрового сигнала задания, который через 50сумматор 2 (сигнал на выходе запоминающего устройства 10 равен нулю)поступает на первый вход блока 4управления и отрабатывается замкнутым контуром регулиронания, образованным блоком 4 управления, объектом 5 управления и измерительнымустройством 6. Результат отработки сигнала задания снимается с выхода. измерительного устройства 6 и поступает на второй вход измерителя 3 рассогласования, где сравнивается с сигналом задания, поступающим на его первый вход, Результат сравнения(ошибка) в цифровом виде поступает на вход блока 7 деления с коэффициентом передачи, равным К. Часть сигнала ошибки системы автоматического управления через сумматор 8 (сигнал на выходе второго регистра 11 равен нулю) поступает на информационный вход первого регистра 9 (для простоты описания далее полагаем коэффициент передачи блока деления 7 равным единице).Через интервал времени, равныйимпульс синхронизации с выхода задающего генератора 12 через блок 13 задержки поступает на вход записи первого регистра 9, н результате чего происходит запись сигнала ошибки в первый регистр 9, На этом заканчивается первый период квантования.Поступление второго импульса с выхода задающего генератора 12 вызывает поступление на вход блока 4 управления второго сигнала задания и запись в запоминающее устройство О содержимого первогорегистра 9,ачерез интернал времени, равный Т - запись в первый регистр 9 нового значения ошибки .Отработка следующих импульсов задающего генератора 2 происходит аналогично, при этом происходит продвижение содержимого запоминакчцего устройства 10 к его выходу так, что поступление Х-го импульса синхрон 1- зации приводит к полному заполнению запоминающего устройства О, На его выходе появляется значение сигнала ошибки, измеренное на первом периоде квантования, и поступает на второй вход сумматора 2, В результате на вход блока 4 управления поступает сигнал управления, ранный сумме текущего сигнала задания и сигнала компенсации ошибки при отработке следующего сигнала задания (на данном периоде квантования - при отработке первого сигнала задания следующего цикла управления). Этим достигается опережение компенсации по отношению к измерению, что необходимо для осуществления синхронизации процесса компенсации. На этом заканчивается первый цикл управления.Поступление следующего, (И+ +1)-го,импульса с выхода задающего генератора 12 вызывает появление ца выходе блокациклического зада-ция первого сигнала задания, запись во второй регистр 11 предыдущего сигнала компенсации ошибки и появление на выходе запоминающего устройства 10 нового сигнала компенсации ошибки. Сигналы задания и компенсации складываются первым сумматором 2 и поступают на первый вход блока 4 управления. Как и на предыдущих периодах квантования, сигнал ошибки снимается с выхода измерителя 3 рассогласования и через блок 7 деления поступает на первый вход второго сумматора 8, на второй вход которого поступает предыдущий сигнал компенса ции с выхода второго регистра 11. Через интервал времени, равный Т, производится запись нового значения компецсационногосигнала свыхода второго сумматора 8 впервый регистр 9.Следующие импульсы синхронизации отрабатываются системой аналогично отработке (И+1)-го импульса.Таким образом, при К с 1 обеспечивается итерационный процесс компен- ЗО сации ошибки системЫ циклического управления при циклическом изменении управляющих ноздействий, а также синхронных сними возмущающих воздействие.Передаточная функция по ошибке 35 системы циклического управления (от выхода объекта 5 управления к входу измерителя 3 рассогласования) оп" ределяется выражениемР 11Циклические воздействия, приложенные к системе. циклического управления, разлагаются в ряд Фурье с частотными составляющимигде и"0,1,2 - номер гармоники.Так как Т=И Т, то после замены 7- =е" тв выражении (1) (справедливом 55 до частОты .0=/Т) видно, что в данной системе циклического управления происходит компенсация частотных сос тавляющих ошибки от возмущений с номером гармоники 0иЫ/2.Иа фиг. 6 представлена амплитудно-частотцая характеристика второго сомножителя выражения (1) при И=30, 2 п/(Т "3,).=3 К=0,25, .1="1/,) где -1, - частота среза контура регулирования.Технические преимущества предлагаемого устройства по сравнению с известным видны ца примере отработки линейно нарастающего задающего воздействия. Кривая 23 ца фиг. 5 график установившегося процесса при настройке контура регулирования на оптимум по модулю и частоте квантования, в два раза большей частоты среза. Из этого графика видно, что н данной системе установившийся процесс проходит через заданные точки А ,АА, а максимальная ошибка) Фе составляет 1/ч часть ступеньки зайдания. Сравнение с результатом отработки линейно нарастающего задающего воздействия н известной системе (кривая 24, фиг. 5) показывает, что динамическая точность данной системы повышается нраза.Ф о р м у и а и э о б р е т е н и яСистема управления, содержащая последовательно соединенные блок циклического задания, первый сумматор, блок управления, объект управления и измерительное устройство, подключенное выходом к второму входу блока управления и к первому входу измерителя рассогласования, соединенного ныходом через блок деления с первым входом второго сумматора, а вторым входом - с выходом блока циклического задания, подключенного входом начальной установки к выходу блока установки в исходное состояние и к входу сброса запоминающего устройства, соединенного выходом с вторым входом первого сумматора, а входом синхронизации - с входом блока задержки, с входом синхронизации блока циклического задания и с выходом задающего генератора, подключенного входом к выходу блока запуска, о т л ич а ю щ а я с я тем, что, с целью поньппеция динамической точности системы, в ней дополнительно установлены первый и второй регистры, причем.Веселовская Техред О.Гортвай Реда Корректор Е.Р Заказ 2984/50 Тираж 836 ВНИИНИ Государственного коми по делам изобретений и отк 113035, Москва, Ж, Раушская иПодписна СССРий афическое предприятие, г. Ужгород, ул. Проектна роизводственно информационный вход первого регистра соединен с выходом, второго сумматора, вход сброса - с выходом блокаустановки в исходное состояние ивходом сброса второго регистра, входзаписи - с выходом блока задержки,а выход - с информационным входом 0 8запоминающего устройства, подключенного выходом к информационному входувторого регистра, соединенноговходом записи с выходом задающего генератора, а выходом - свторым входом второго сумматора.

СмотретьЗаявка

3817007, 23.11.1984

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

МИХАЛЬЧЕНОК ГЕРМАН ФЕДОРОВИЧ, НОВИКОВ ВЛАДИСЛАВ АЛЕКСАНДРОВИЧ, СИДОРОВИЧ ЕВГЕНИЙ АНДРЕЕВИЧ, СУСЛОВ ВАЛЕРИЙ ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G05B 13/02

Метки:

Опубликовано: 30.05.1986

Код ссылки

<a href="https://patents.su/5-1234810-sistema-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Система управления</a>

Предыдущий патент: Задатчик скорости

Следующий патент: Цифровая система управления

Случайный патент: Гидравлическая разгрузочная пята