Дешифратор для запоминающего устройства с резервированием

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1213503

Авторы: Ахмеджанов, Лазаренко, Лушников, Романов, Хван

Текст

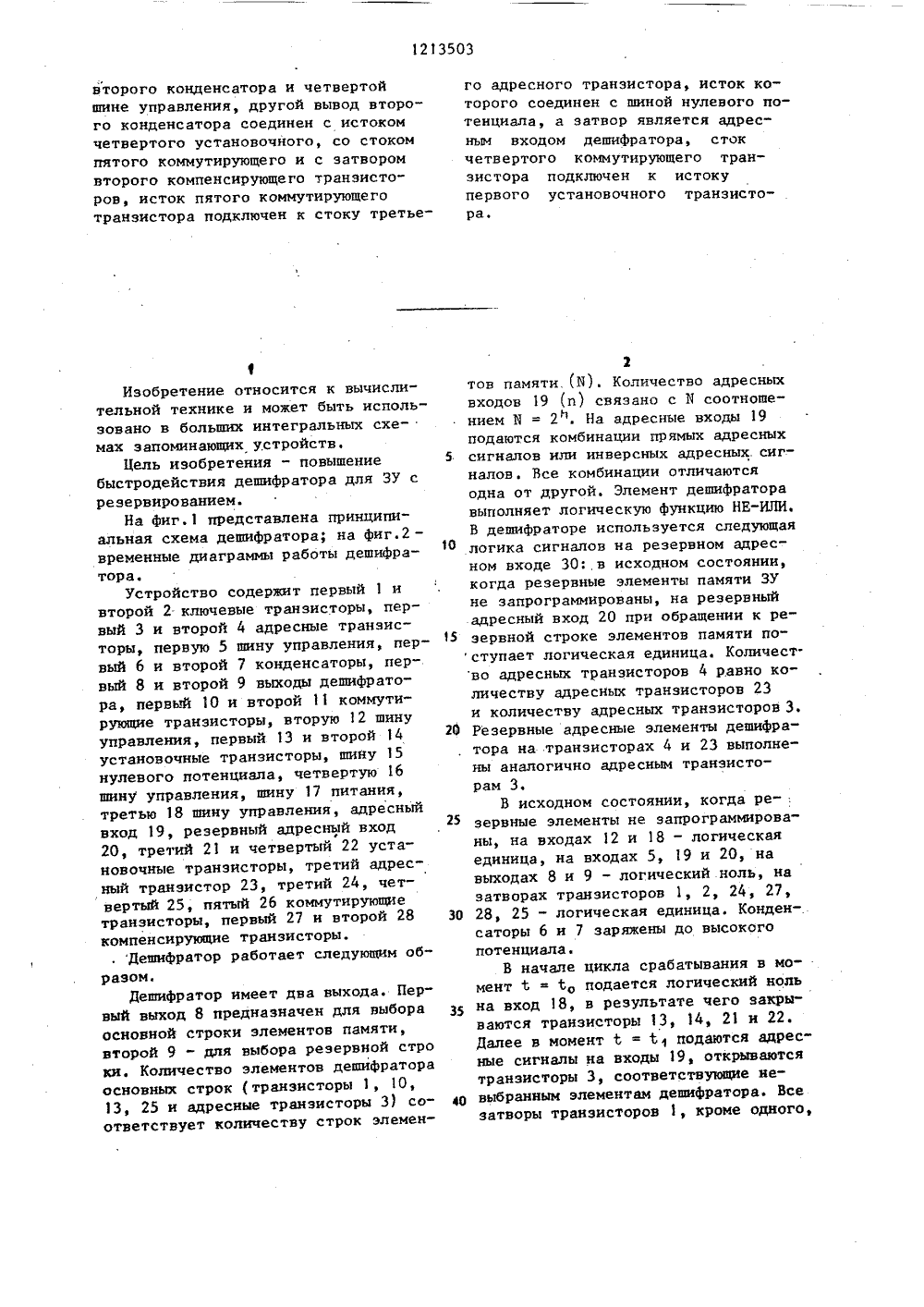

(Ю (ИС 11 С 11/40ЮфСТИЕННИЙ КОМИТЕТ СССРЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ АНИЕ ИЗОБРЕТЕНИ(54)(57) ДЕП 1 ИФРАТОР ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА С РЕЗЕРВИРОВАНИЕМ, содержащий первый и второй ключевые транзисторы, первый и второй установочные транзисторы, первый и второй коммутирующие транзисторы, первый и второй адресные транзисторы, шину питания, шину нулевого потенциала, шины. управления, причем стоки ключевых транзисторов подключены к первой шине управления, истоки первого и второго ключевых транзисторов являются соответственно первым и вторым выходами дешифратора, за-. твор первого ключевого транзистора соединен со стоком первого комьютиРующего транзисторазатвор второго ключевого транзистора подключен к стоку второго коммутирующего транзистора, затворы первого и второго коммутирующих транзисторов объединены и подключены к второй шине управления, исток первого коммутирующего тРанзистора соединен со стоком первого адресного и истоком первого установочного транзисторов, исток второго коммутирующего транзистора подключен к стоку второго адресного ш истоку второго установочного транзисторов, истоки первого н второгоадресных транзисторов соединены сшиной нулевого потенциала, стокипервого и второго установочных транзисторов подключены к шине питания,затворы первого и второго установочных транзисторов подключены к третьей шине управления, затворы первого и второго адресных транзисторов являются адресными входамн дешифратора, о т л и ч а ю щ и й с ятем, что, с целью повьппення быстродействия дешифратора, он содержиттретий и четвертый установочные транзисторы, третий адресный транзистор, третий, четвертый и пятыйкоммутирующие транзисторы, первый и второй компенсирующие транзисторы,первый и второй конденсаторы, причем затворы третьего и четвертого установочных транзисторов подключенык третьей шине управления, а их стоки соединены с шиной питания, исток третьего установочного транзистора соединен с истоками третьего, четвертого коммутирующих и первого компенсирующего транзисторов, затворытретьего и четвертого коииутируащих транзисторов объединены и подключены к истокам второго установочного и второго компенсирующего транзисторов, стоки комиенсирушщнх транзисторов объединены с затвором пятого ковмуткрующего транзистора н соедн" невы с шивой питания, затвор первого компенсирующего транэшстоуа соединен ео стоком третьего комиутшрую. щего трашзнстора и одним выводом .первого конденсатора, другой выводкоторого подключен к одному выводу1213503 второго конденсатора и четвертойшине управления, другой вывод второго конденсатора соединен с истокомчетвертого установочного, со стокомпятого коммутирующего и с затворомвторого компенсирующего транзисторов, исток пятого коммутирующеготранзистора подключен к стоку третье 1Изобретение относится к вычислительной технике и может быть использовано в больших интегральных схемах запоминающих устройств,Цель изобретения - повышениебыстродействия дешифратора для ЗУ срезервированием.На фиг.1 представлена принципиальная схема дешифратора; на Фиг,2 -временные диаграммы работы дешифратора.Устройство содержит первый 1 ивторой 2 ключевые транзисторы, первый 3 и второй 4 адресные транзисторы, первую 5 шину управления, первый 6 и второй 7 конденсаторы, первый 8 и второй 9 выходы дешифрато"ра, первый 10 и второй 11 коммутирующие транзисторы, вторую 12 шинууправления, первый 13 и второй 14установочные транзисторы, шину 15нулевого потенциала, четвертую 16шину управления, шину 17 питания,третью 18 шину управления, адресныйвход 19, резервный адресный вход20, третий 21 и четвертый 22 установочные транзисторы, третий адресный транзистор 23, третий 24, четвертый 25, пятый 26 коммутирующиетранзисторы, первый 27 и второй 28компенсирующие транзисторы.Дешифратор работает следующим образом,Дешифратор имеет два выхода, Пер"вый выход 8 предназначен для выбораосновной строки элементов памяти,второй 9 - для выбора резервной строки. Количество элементов дешифратораосновных строк (транзисторы 1, 1 О,13, 25 и адресные транзисторы 3) соответствует количеству строк элемен 5 10 15 20 25 30 35 40 го адресного транзистора, исток которого соединен с шиной нулевого потенциала, а затвор является адресным входом дешнфратора, стокчетвертого коммутирующего транзистора подключен к истокупервого установочного транзистора 2тов памяти.(Б). Количество адресныхвходов 19 (п) связано с Б соотношением Б = 2". На адресные входы 19подаются комбинации прямых адресныхсигналов или инверсных адресных. сигналов. Все комбинации отличаютсяодна от другой. Элемент дешифраторавыполняет логическую функцию НЕ-ИЛИ.В дешифраторе используется следующая логика сигналов на резервном адресном входе 30: в исходном состоянии,когда резервные элементы памяти ЗУне запрограммированы, на резервныйадресный вход 20 при обращении к резервной строке элементов памяти поступает логическая единица. Количест. во адресных транзисторов 4 равно количеству адресных транзисторов 23 и количеству адресных транзисторов 3. Резервные адресные элементы дешифратора на транзисторах 4 и 23 выполнены аналогично адресным транзисторам 3.В исходном состоянии, когда ре- . зервные элементы не запрограммированы, на входах 12 и 18 - логическая единица, на входах 5, 19 и 20, на выходах 8 и 9 - логический ноль, на затворах транзисторов 1, 2, 24, 27, 28, 25 - логическая единица. Конденсаторы 6 и 7 заряжены до высокого потенциала.В начале цикла срабатывания в момент 1 = Со подается логический ноль на вход 18, в результате чего закрываются транзисторы 13, 14, 21 и 22. Далее в момент 1 = 1 1 подаются адрес" ные сигналы на входы 19, открываются транзисторы 3, соответствующие не- выбранным элементам дешифратора. Все затворы транзисторов 1, кроме одного,разряжаются через транзисторы 1 О и 3до уровня нулевого потенциала. Одновременно с сигналом 19 подается логическая единица на резервный адресный вход 20, затвор транзистора 2разряжается через транзисторы 11 и 4до нулевого потенциала, затворы транзисторов 24 и 25 " через транзистор4, затвор транзистора 28 - черезтранзисторы 26 и 23 до уровня нулевого потенциала. После этого подается логическая единица на вход 5 ичерез единственный открытый транзистор 1 заряжается выбранная выходная шина 8 до высокого потенциала,Для нормальной работы дешифратора необходимо, чтобы на истокахтранзисторов 21 и 25 оставался высокий потенциал при подаче резервныхадресных сигналов 20, т.е. уменьшение потенциала на затворах транзисторов 25 через транзистор 4 должнопроисходить быстрее, чем на истокахтранзисторов 13 через транзисторы3. В противном случае, откроютсятранзисторы 25 и разрядят узловуюемкость на истоке транзистора 21,что приведет к снижению потенциалавыбранного элемента дешифратора наистоке транзистора 13 и к нарушениюнормальной работы дешифратора. Выполнить данное условие достаточнотяжело, так как в ЗУ узловые емкости истоков транзисторов 13 разряжаются большим количеством транзисторов 3, а емкости большого числазатворов транзисторов 25 разряжаются в общем случае всего одним транзистором 4, Дополнительное ускорение разряда узловой емкости истокатранзистора 21 вызывается влияниемсуммарной емкостной связи затвор -исток транзисторов 25. Кроме того,значительный разброс в БИЧ такихпараметров, как пороговое напряжение, крутизна транзисторов и вел.чина емкостей не дает возможностигарантировать отсутствие паразитного разряда выбранного элемента дешифратора Наличие внутренних помехпо земле, питанию и подложке ещеболее осложняет ситуацию. Для предотвращения такого параэитного разряда используются транзисторы 24 и27 и конденсатор 6, Одновременнос сигналами 19 и 20 подается логическая единица на вход 16, В этот 10 15 20 25 30 35 40 45 50 55 момент потенциал на затворе транзистора 24 не выше, чем на его истоке и транзистор 24 закрыт. В результате емкостной связи конденсатора 6 потенциал на затворе транзистора 27 превышает потенциал напряжения питания плюс пороговое напряжение транзистора 27, в результате чего транзистор 27 открыт и заряжает узловую емкость на истоке транзистора 21 до напряжения источника 17 питания, препятствуя паразитному снижению по" тенциала на истоке транзистора 21 через открытй транзистор 25. После этого подается логическая единица на вход 5 и через единственный от- крытый транзистор 1 заряжается выбранная выходная шина 8 до высокого потенциала, На входе 12 поддерживается постоянный высокий потенциал.При программировании резервных элементов памяти изменяется логика резервных адресных сигналов 20. При совпадании адреса на входе ЗУ с адресом дефектного элемента памяти на всех входах 20 - логический ноль, при несовпадении (хотя бы на одном входе 20) - логическая единица. Когда на входе 20 - логическая единица, дешифратор работает аналогично случаю неэапрограммированного ЗУ.Рассмотрим случай, когда в запрограммированном ЗУ адреса на входе ЗУ совпадают с запрограммированным адресом, на всех входах 20 - логический нольВ начале цикла срабатывания на входах 18, 12 - логическая единица, на входах 5, 16, 19, 20 - , логический ноль, на затворах транзисторов 1, 2, 24, 27, 28, 25 - логическая единица. Конденсаторы б и 7 заряжены до высокого потенциала. На вход 18 подается логический ноль, закрываются транзисторы 13, 14, 2 и 22, подаются адресные сигналы на входы 19, открываются транзисторы 3, соответствующие невыбранным элементам дешифратора. Все затворы транзисторов 1, кроме одного, разряжаются через транзисторы 10 и 3 до уровня нулевого потенциала. Так как на входе 20 - логический ноль, на затворах транзисторов 25 остается высокий логический уровень, узловая емкость на истоках транзисторов 25 разряжается через транзисторы 24 и 3 до уровня нулевого потенциала и единственный выбранный элемент дешифраторатакже разряжается через транзистор25 до уровня нулевого потенциала,Через транзистор 24 разряжается затвор транзистора 27 и конденсатор 6,транзистор 27 закрывается. Таким образом, дефектный основной элементпамяти заблокирован,Далее подается логическая единица на вход 5 и через открытый транзистор 2 поступает на выходе 9 - навыбор резервного элемента памяти.При этом следует учесть следующее.При разряде узловой емкости на истоках транзисторов 25 в результате емкостной передачи исток - затвор транзисторов 25 возникает отрицательнаяпомеха на затворах транзисторов 25,что приводит к снижению потенциалана затворе транзистора 2 и замедлению фронта на выходе 9 при подачелогической единицы на вход 5, в результате ухудшается быстродействиедешифратора, Для предотвращения данного эффекта используются транзисторы 23, 22, 26 и 28 и конденсатор 7,При этом на затворе транзистора 23 -логический ноль, транзистор 23 за"5 крыт. Конденсатор 7 заряжен до высокого потенциала. На вход 16 одновременно с сигналами 19 и 20 подается логическая единица. За счет емкостной связи конденсатора 7 увели 10 чивается потенциал на затворе транзистора 28, при этом заряжается узловая емкость на затворах транзисторов 25 до потенциала источника питания, предотвращая снижение потенциала за счет помехи,Дешифратор может выбирать болееодного пезервного элемента памяти.При этом в элемент дешифратора основных строк включается дополннтель 20 ное количество транзисторов 25, атакже транзисторов 2, 11, 20, 24,27, 14, 22, 23, 26 конденсаторов 6и 1, которые следует подключить всоответствии с предлагаемой схемой% Корректор А.Зимокос едактор Н.Гун 783/59 Тираж 544ВНИИПИ Государственного комитета СССпо делам изобретений и открытий113035, Москва, Ж, Раушская н Зак писноеу Де ал ППП "Патент", г. Ужгород, ул. Проектн

СмотретьЗаявка

3759447, 04.07.1984

ПРЕДПРИЯТИЕ ПЯ Р-6429

АХМЕДЖАНОВ РАМЗЕЙ АБДУЛЛОВИЧ, ЛАЗАРЕНКО ИВАН ПЕТРОВИЧ, ЛУШНИКОВ АЛЕКСАНДР СЕРГЕЕВИЧ, РОМАНОВ СЕРГЕЙ НИКОЛАЕВИЧ, ХВАН ИГОРЬ АЛЬБЕРТОВИЧ

МПК / Метки

МПК: G11C 11/40

Метки: дешифратор, запоминающего, резервированием, устройства

Опубликовано: 23.02.1986

Код ссылки

<a href="https://patents.su/5-1213503-deshifrator-dlya-zapominayushhego-ustrojjstva-s-rezervirovaniem.html" target="_blank" rel="follow" title="База патентов СССР">Дешифратор для запоминающего устройства с резервированием</a>

Предыдущий патент: Буферное запоминающее устройство

Следующий патент: Устройство для фоторазметки линейных шкал

Случайный патент: Туннельная печь для переработки горючих сланцев