Устройство для вычисления функций sin х и cos х

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 974371

Авторы: Бархоткин, Бельц, Васильченко, Генералов, Мотин

Текст

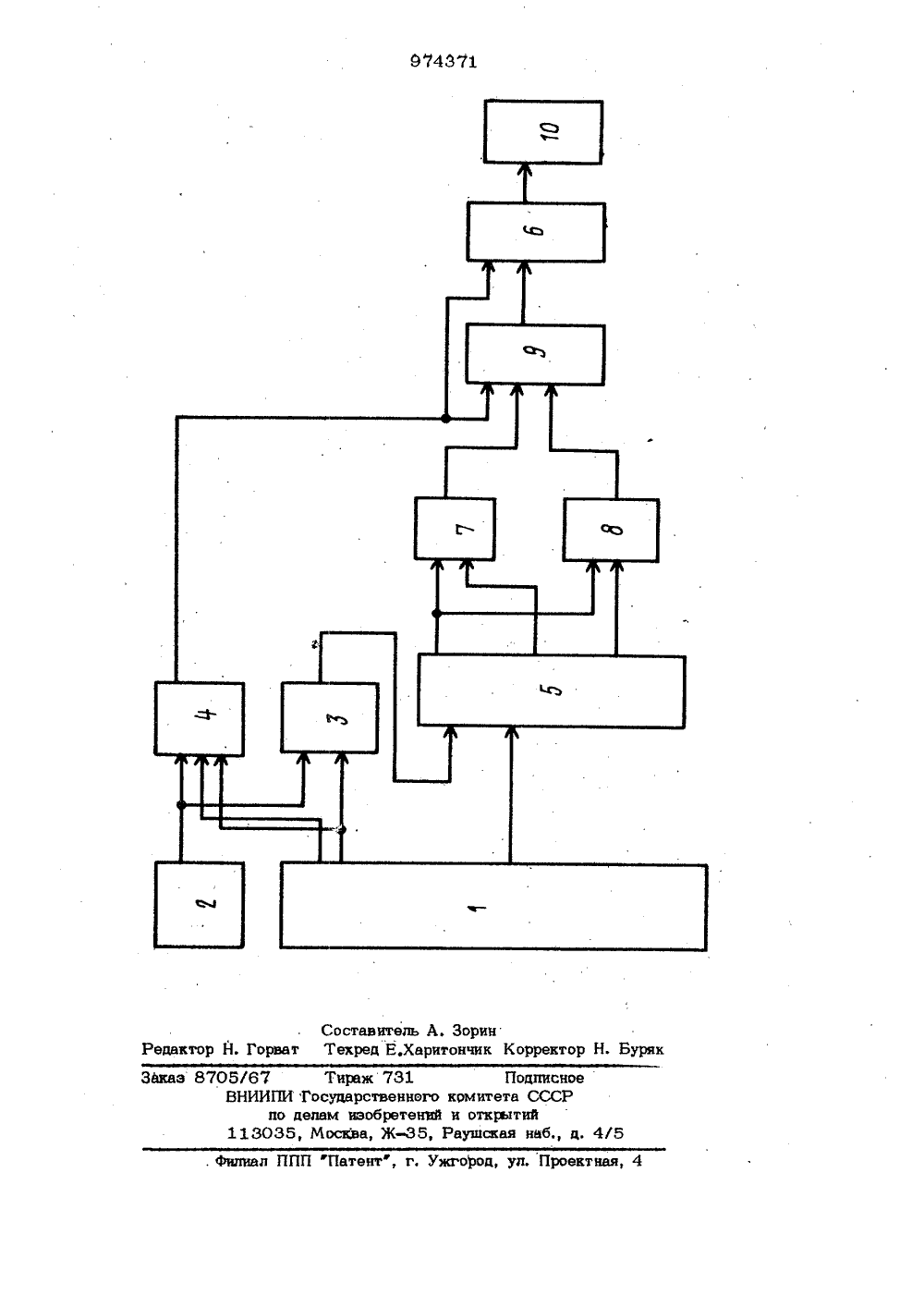

(54) УСТРОЙСТВА ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ51 п Х И со 5 х 1Изобретение относится к вычислительной технике и может быть использованодля аппаратурной реализации функцийБ 1 и х и со 5 х в быстродействующих цифровывычислительных устройствах,Известен цифровой функциональныйгенератор, содержащий блоки для запоминания угловых значений функций и еепроизводной, дешифратор, сумматор, имножительный блок, соединенный с выходом с входом сумматора, группу элементов И, группу элементов ИЛИ и дварегистра, выходы одного из которыхсоединены с входом множительного блокаа выходы второго через дешифратор подключены к первым входам двух группэлементов И, вторые входы которых соединены с выходами соответствующих разрядов блоков запоминания угловых значений функций н ее производной, причем,выходы элементов И через соответствующие элементы ИЛИ подключены соответственно к входу множительного блока ивходу сумматора 13,Недостаток такого генератора заключается в сложности реализации, обуслов ленной наличием блока умножения и н обходимостью использовать блоки памят большей емкости для достижения высоко точности. Наиболее близким к предлагаемому является устройство для вычисления функцийсинуса и косинуса, содержащее входной 10регистр, три блока памяти, два блока умножения, сумматор и выходной регистр,выходы старших разрядов входного регистра подключены к адресаам входам первого и второго блоков памяти, выходымладших разрядов входного регнстра - кпервой группе входов блока умножения,вторая группа входов которого подключена к выходам второго блока памяти, выходы блока умножения подключены к перо вой группе входов сумматора, выход которого подключен к входу выходного регистра, адресные входы второго блока памяти подключены к выходам старшей подгруппы младших разрядов входного реЗдесь 0 с 1 ф = АБ + АР + ВАР,3 9743гистра, выходы третьего блока памяти -к первой группе входов, а выходы первого блока памяти - к второй группе входов втораго блока умножения, выходыкаторга подключены к второй группе входов сумматора 2 3,Однако известное устройство обладаетсложной конструкцией.Целью изобретения является упрощениеустройства. 10Поставленная цель достигается тем,что в устройстве для вычисления функцийб1 К, с о в м, содержащем входной регистр,триггер, сумматор по модулю два, блоканализа квадраНта, .два блока памяти, 1сумматор, два коммутатора и выходнойрегистр, причем выход триггера соединенс первыми входами блока анализа квадранта и сумматора по модулю два, вторыевходы которых соединены с выходом второго разряда входного регистра, выходпервого разряда и выход разрядов с третьего до и -го (где и - разрядность аргумента) которого соединены соответственно с третьим входом блока анализа квад-ранта и информационным входом первогокоммутатора, управляющий вход которогосоединен с выходом сумматора по модулюдва, выход блока анализа квадранта соединен с управляющим входом второгокоммутатора, выход и информационныйвход которого соединены соответственнос входом выходного регистра и выходомсумматора, первый выход первого коммутатора соединен с первыми входами первого и второго блоков памяти, второй итретий выходы первого коммутатора соединены соответственно со вторыми входами первого и второго блоков памяти,выходы которых соединены соответственно с первым и вторым информационными входами сумматорауправляющий вход которого соединен с выходомблока анализа квадранта.На чертеже представлена блок - схема4устройства.Устройство для вычисления функций51 ох и сов х содержит входной регистр 1,триггер 2, сумматор 3 по модулю два,блок 4 анализа квадранта, коммутаторы5 и 6, блоки 7 и 8 памяти, сумматор 9,выходной регистр 10.Сумматор 3 должен вырабатыватьлогическую функцию ф, фБ+ Р, аблок анализа квадранта 4 должен вырабатывать логическую функцию ф,.: 71 4Здесь А и Б - два старших разряда кодаугла, определяющие номер квадранта,Р - код функций (Р=О при вычислениифункции еп к, Г=1 при вычислении функции соя х).Устройство работает следующим образом.В регистр 1 записывается код аргумента, выраженный в единицах - , гдеХ23л - код аргумента в радианах. Квюмутатор 5 пропускает на входы блоков 7 и 8прямой или инверсный код агрумента, взависимости от управляющего сигнала,вырабатываемого сумматором 3.Представим аргумент в виде к = а+в++ Е" (а+Ъ)с,Если произвести разбиение кода аргумента на группы разрядов а, . и с так, чтобы произведениеП = Е (а+Ь)с было меньше единицы младшего разряда,получим Г(Х)=Е (сиЬ)ф+Е (9)д+ Е д2)с,Е(Х) Е (сй+Ь)+Е( )с,. Первый блок 7 вырабатывает код точногозначения функции Б 1 пк., а второй блок 8реализует табличное устройство умножения,С выхода второго блока 8 на входсумматора 9 подается код Е()С т.е. код добавки минус единица младшего разряда, а на третий вход сумматораподается единица, если выходной код небудет преобразовываться в дополнительный, и подается ноль, если выходнойкод будет преобразоваться,При реализации 16-разрядных функцийв группу а входят разряды со второго пошестой, в группу в - разряды с седьмогопо десятый, в группу с - разряды с одиннадцатого по пятнадцатый.Предложенная структура устройствавычисления функций зо к и сов х позволяет отказаться от двух блоков умножения, что снижает аппаратурныезатраты ии сложность иэделия.формула изобретенияУстройство для вычисления функцийВ 1 п х исовх, содержащее входной ре5 9743 гистр, триггер, сумматор по модулю два, блок анализа квадранта, два блока памяти, сумматор, два коммутатора и выходной регистр, прьчем выход триггера соединен с первымн входами блока анализа квадранта и сумматора по модулю два, вторые входы которых соединены с выходом второго разряда входного регистра, выход первого разряда и выход разрядов с третьего до ь-го (где п - разрядность 1 р аргумента) которого соединены соответственно с третьим входом блока аналнза квадранта и информационным входом пер- . Ього коммутатора, управляющий вход которого соединен с выходом сумматора по 5 модулю два, выход блока анализа квадранта соединен с управляющим входом второго коммутатора, выход н информа-, ционный вход которого соединены соответственно с входом выходного регистра 71 Ьи выходом сумматора, первый выходпервого коммутатора соединенс первымивходами первого и второго блоков памяти, о т л и ч а ю щ е е с я тем, что,с целью упрощения устройства, второйи третий выходы первого коммутаторасоединены соответственно со вторымивходами первого и второго. блоков памяти, выходы которых соединены соответственно с первым и вторым информационными входами сумматора, управляющийвход которого соединен с выходом блокаанализа квадранта.Источники информации,принятые во вннмание при экспертиэе1. Авторское свндетельство СССРЖ 504195, кл, 6 06 Р 1 Ю 2, 1975.2. Авторское свидетельство СССРз 8705/67 Тираж 731 Подписное ВНИИПИ Государственного комитета СССР по дедам изобретений и откратий 113035, Москва, Ж, Раушская наб., д. л ППП Патент, г. Ужгород, ул. Проек

СмотретьЗаявка

3285483, 27.02.1981

МОСКОВСКИЙ ИНСТИТУТ ЭЛЕКТРОННОЙ ТЕХНИКИ

БАРХОТКИН ВЯЧЕСЛАВ АЛЕКСАНДРОВИЧ, БЕЛЬЦ ВИКТОР АНДРЕЕВИЧ, ГЕНЕРАЛОВ АНАТОЛИЙ ВИКТОРОВИЧ, ВАСИЛЬЧЕНКО НИКОЛАЙ ВЛАДИМИРОВИЧ, МОТИН ПЕТР ЕРМОЛАЕВИЧ

МПК / Метки

МПК: G06F 7/548

Метки: вычисления, функций

Опубликовано: 15.11.1982

Код ссылки

<a href="https://patents.su/4-974371-ustrojjstvo-dlya-vychisleniya-funkcijj-sin-kh-i-cos-kh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функций sin х и cos х</a>

Предыдущий патент: Устройство для умножения

Следующий патент: Устройство для обработки информации, зарегистрированной на магнитном носителе

Случайный патент: Грузозахватное устройство