Устройство для вычисления логических выражений переменных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 962918

Авторы: Гурьянов, Козюминский, Мищенко, Семашко

Текст

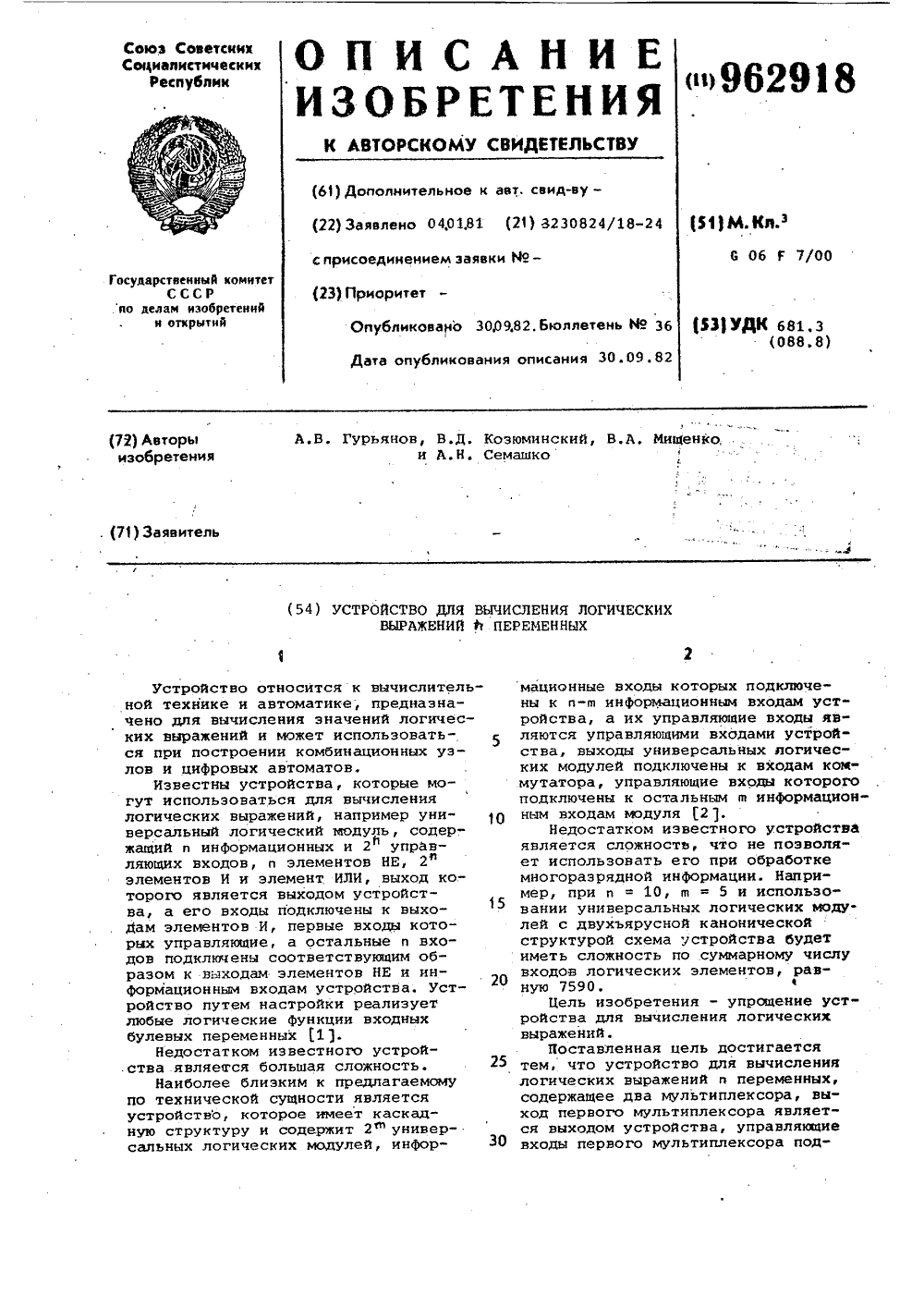

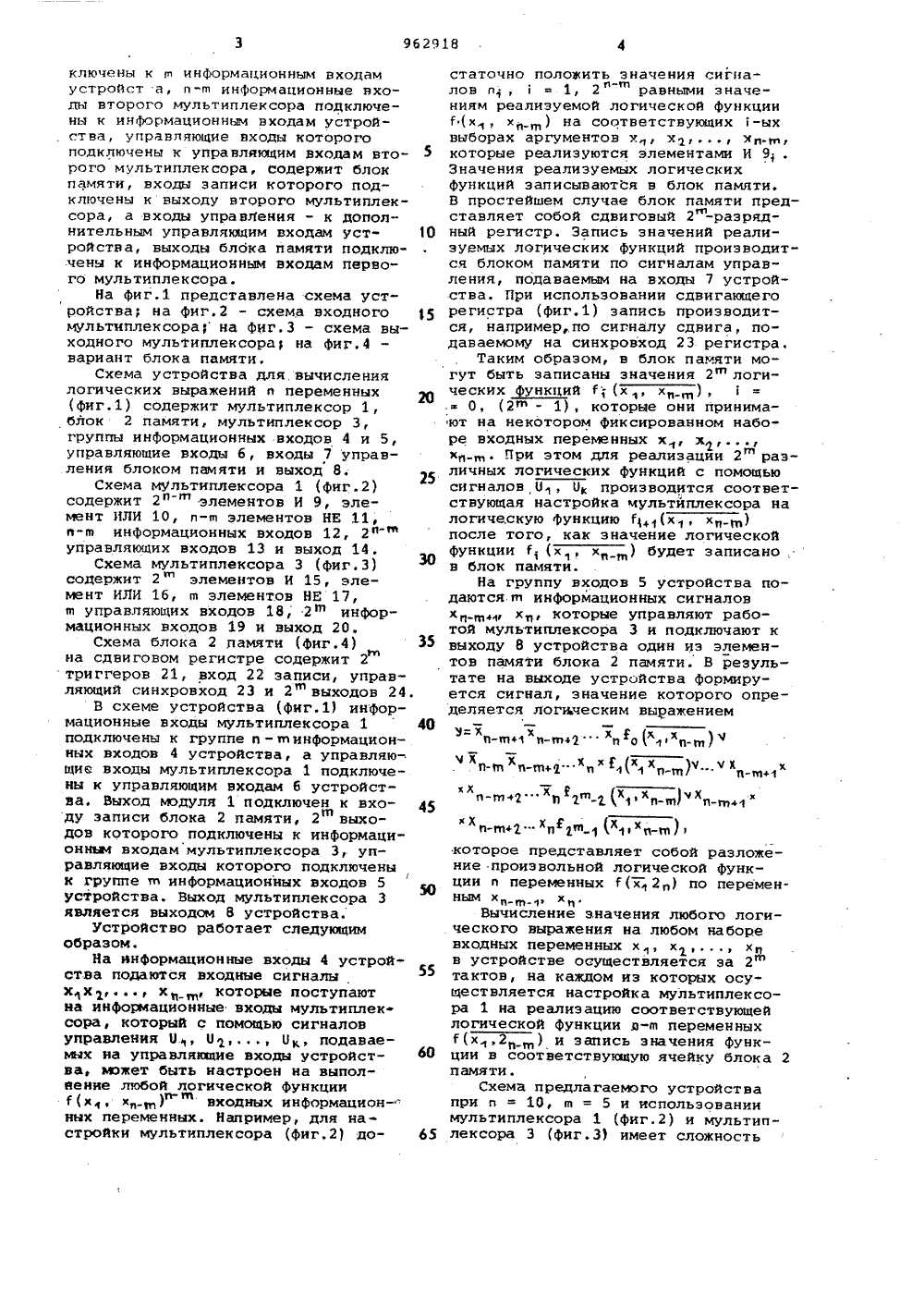

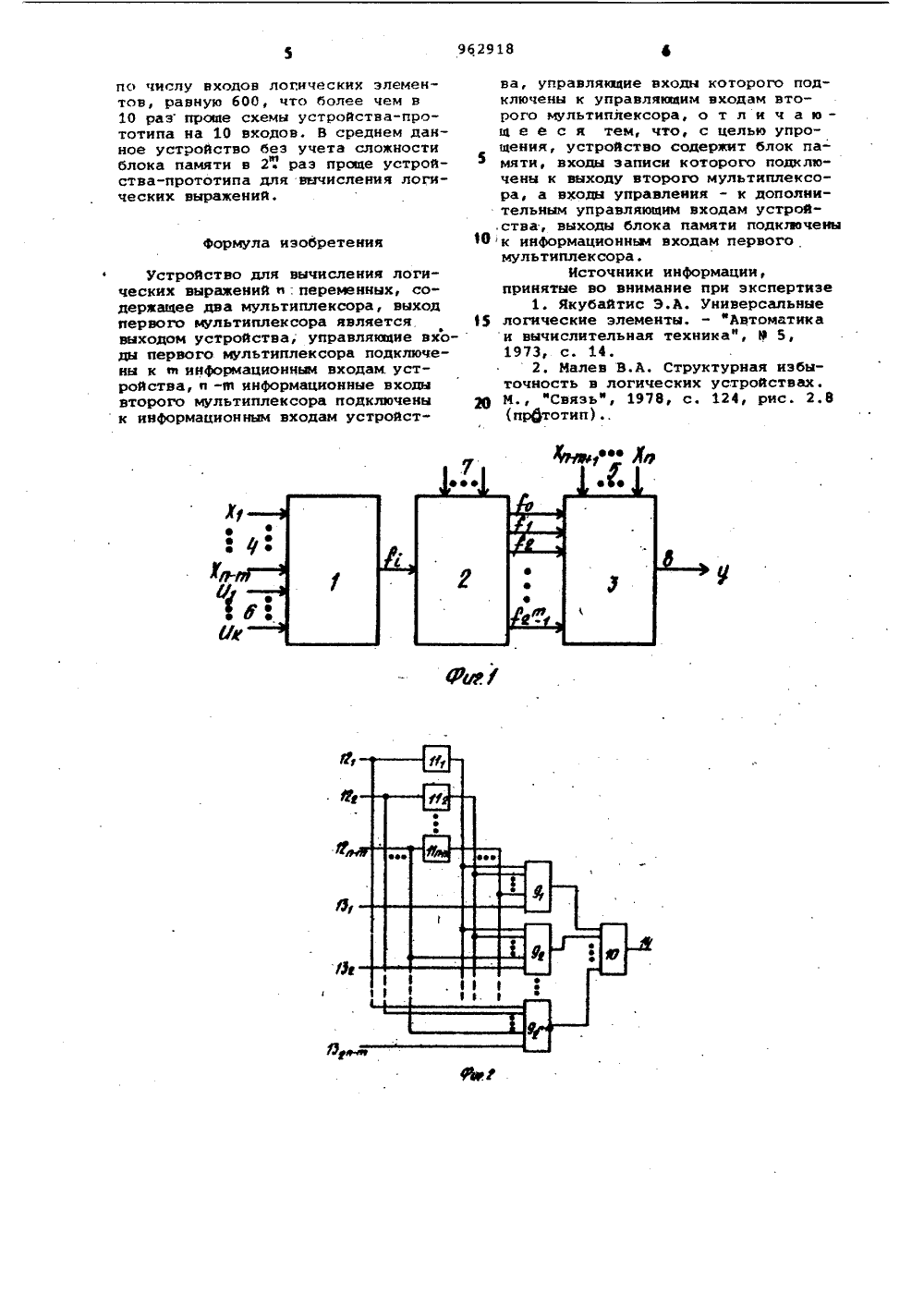

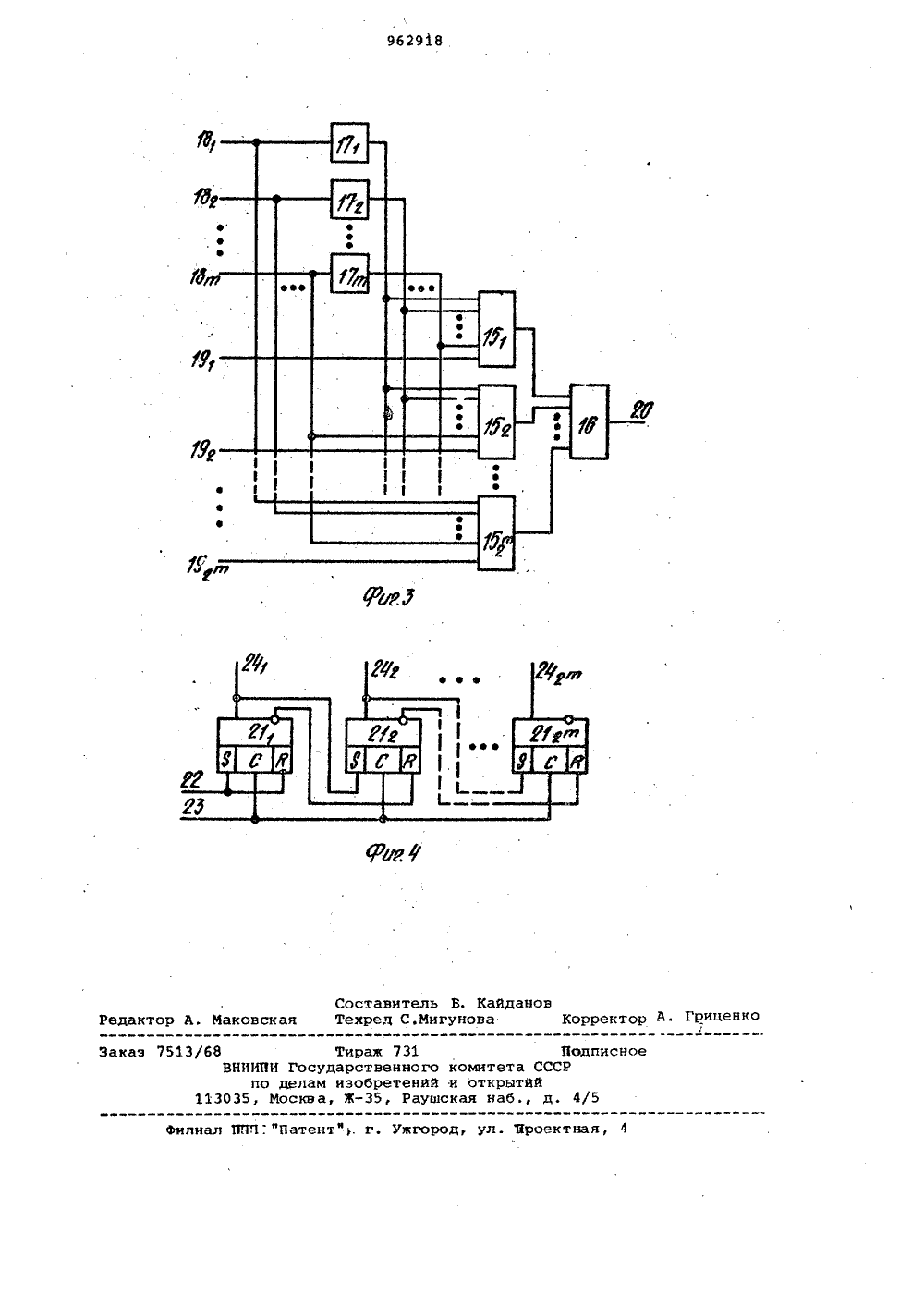

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик оч 962918(ф 11 М Кт Э С 06 Г 7/00 Государственный комитет СССР но делам изобретений н открытийДата опубликования описания 30.09.82(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГИЧЕСКИХ ВЫРАЖЕНИЙ Ь ПЕРЕМЕННЫХУстройство относится к вычислительной технике и автоматике, предназначено для вычисления значений логических выражений и может использоваться при построении комбинационных узлов и цифровых автоматов,Известны устройства, которые могут использоваться для вычисления логических выражений, например универсальный логический модуль, содер-. жащий п информационных и 2 управлляющих входов, и элементов НЕ, 2" элементов И и элемент ИЛИ, выход которого является выходом устройства, а его входы подключены к выходам элементов И, первые входы которых управляющие, а остальные и входов подключены соответствующим образом к выходам элементов НЕ и информационныч входам устройства. Устройство путем настройки реализует любые логические функции входных булевых переменных 1).Недостатком известного устрой.ства является большая сложность. 25Наиболее близким к предлагаемому по технической сущности является устройство, которое имеет каскадную структуру и содержит 2 ф" универсальных логических модулей, инфор мационные входы которых подключены к п-а информационным входам устройства, а их управляющие входы являются управляющими входами устройства, выходы универсальных логических модулей подключены к входам коммутатора, управляющие входы которого подключены к остальным а информационным входам модуля (2 .Недостатком известного устройства является сложность, что не позволяет использовать его при обработке многоразрядной информации. Например, при и = 10, е = 5 и использовании универсальных логических модулей с двухъярусной канонической структурой схема Устройства будет иметь сложность по суммарному числу входов логических элементов, равную 7590.ФЦель изобретения - упрощение устройства для вычисления логических выражений.Поставленная цель достигается тем, что устройство для вычисления логических выражений и переменных, содержащее два мультиплексора, выход первого мультиплексора является выходом устройства, управляющие входы первого мультиплексора под 9 б 291810 15 20 25 35 40 45 6065 ключены кинформационным входамустройст а, и"щ информационные входы второго мультиплексора подключены к информационньм входам устройства, управляющие входы которогоподключены к управляющим входам второго мультиплексора, содержит блокпамяти, входы записи которого подключены к выходу второго мультиплексора, а входы управления - к дополнительным управляющим входам устройства, выходы блбка памяти подключены к информационным входам первого мультиплексора,На фиг.1 представлена схема устройства; на Фиг.2 - схема входногомультиплексора на Фиг,З - схема выходного мультиплексора на Фиг.4вариант блока памяти,Схема устройства для вычислениялогических выражений и переменных(фиг.1) содержит мультиплексор 1,блок 2 памяти, мультиплексор 3,группы информационных входов 4 и 5,управляющие входы б, входы 7 управления блоком памяти и выход 8.Схема мультиплексора 1 (фиг.2)содержит 2 и и элементов И 9, элемент ИЛИ 10, п-щ элементов НЕ 11,и"а информационных входов 12, 2" фуправляющих входов 13 и выход 14.Схема мультиплексора 3 (фиг.3)содержит 2 элементов И 15, элемент ИЛИ 16, в элементов НЕ 17,щ управляющих входов 18, 2 щ информационных входов 19 и выход 20.Схема блока 2 памяти (фиг.4)на сдвиговом регистре содержит 2триггеров 21, вход 22 записи, управляющий синхровход 23 и 2 выходов 24В схеме устройства (фиг.1) информационные входы мультиплексора 1подключены к группе п в тинформационных входов 4 устройства, а управляющие входы мультиплексора 1 подключены к управляющим входам б устройства. Выход модуля 1 подключен к входу записи блока 2 памяти, 2 выходов которого подключены к информационниа входам мультиплексора 3, управляющие входы которого подключенык группе т информационных входов 5устройства. Выход мультиплексора 3является выходом 8 устройства.Устройство работает следующимобразом.На информационные входы 4 устройства подаются входные сигналых 1 х 2 х которые поступаютна информационные входы мультиплексора, который с помощью сигналовуправления О., О 2 О, подаваемых на управляющие входы устройства, манжет быть настроен на выполйение любой логической функцииГ(х, х ,) входных информацион ных переменных. Например, для настройки мультиплексора (фиг.2) достаточно положить значения сигналов и,= 1, 2"равными значениям реализуемой логической функцииГ(х, х) на соответствующих 1-ыхвыборах аргументов х х 2 х-и,которые реализуются элементами И 9 .Значения реализуемых логическихфункций записываются в блок памяти.В простейшем случае блок памяти представляет собой сдвиговый 2-разрядный регистр. Запись значений реализуемых логических функций производится блоком памяти по сигналам управления, подаваемым на входы 7 устройства. При использовании сдвигающегорегистра (фиг,1) запись производится, например,по сигналу сдвига, подаваемому на синхровход 23 регистра.Таким образом, в блок памяти могут быть записаны значения 2 илогических Функций Г;.(х , х и),О, (2 ф" - 1), которые они принимают на некотором фиксированном набо"ре входных переменных х, х 2,,х,. Ври этом для реализацйи 2 различных логических функций с помощьюсигналов О, О производится соответствующая настройка чультйплексора налогическую Функцию Г 1,1(х, "и-в)после того, как значение логическойФункции Г 1(х , х и,) будет записанов блок памятй.На группу входов 5 устройства подаются.т информационных сигналовх и 1 х, которые управляют работой мультиплексора 3 и подключают квыходу 8 устройства один иэ элементов памяти блока 2 памяти. В результате на выходе устройства формируется сигнал, значение которого определяется логическим выражениемЗ=Х Х Х Е 1 х хи-ин 1 и-пн 2 и ои-в)и-в "и-в+2" и ( 1 и-т) -. и-а+1кХ, ,хй 1Х У х Х и-в 2 -"и 2 фф 1 1"1 "о-е)которое представляет собой разложение произвольной логической функции и переменных Г(х 2) по переменным х,и , х,Вычисление значения любого логического выражения на любом наборе входных переменных х, х 2 хи в устройстве осуществляется за 2 и тактов, на каждом из которых осуществляется настройка мультиплексора 1 на реализацию соответствующей логической функции д-а переменных Г(х, 2 ,) и запись значения функции в соответствукщую ячейку блока 2 памяти.Схема предлагаемого устройства при и = 10, в = 5 и использовании мультиплексора 1 (фиг.2) и мультиплексора 3 (Фиг,З) имеет сложностьпо числу входов логических элементов, равную 600, что более чем в 10 раз проще схемы устройства-прототипа на 10 входов. В среднем данное устройство без учета сложности блока памяти в 2раз проще устройства-прототипа для вычисления логических выражений.формула изобретенияф Устройство для вычисления логических выражений е; переменных, содержащее два мультиплексора, выход первого мультиплексора является выходом устройства, управляющие входы первого мультиплексора подключены к е информационным входам. Устройства, н -е информационные входы второго мультиплексора подключены к информационным входам устройства, управлякиаие входы которого подключены к управляющим входам второго мультиплексора, о т л и ч а ю -щ е е с я тем, что, с целью упрощения, устройство содержит блок памяти, входы записи которого подключены к выходу второго мультиплексора, а входы управления - к дополнительным управляющим входам устрой,ства, выходы блока памяти подклочены6 к информационньм входам первогомультиплексора.Источники информации,принятые во внимание при экспертизе1. Якубайтис Э.А. Универсальные5 логические элементы. - фАвтоматикаи вычислительная техникаф, 9 5,1973, с. 14,2. Малев В.А. Структурная избыточность в логических устройствах.щ М., "Связью, 1978, с. 124, рис. 2.8962918 Хю Составитель В. КайданРедактор А. Маковская Техред С,Мигунова Гриценко с 513 к комитета ССи открытййкая наб., д 5 Филиал ЯГГ. "Патентф. г. Ужгород, ул. Яроектна/68 Тираж 731 ВНИИиИ Государственного по делам изобретений 113035, Москва, Ж, Рауш

СмотретьЗаявка

3230824, 04.01.1981

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

ГУРЬЯНОВ АНАТОЛИЙ ВАСИЛЬЕВИЧ, КОЗЮМИНСКИЙ ВАЛЕРИЙ ДМИТРИЕВИЧ, МИЩЕНКО ВАЛЕНТИН АЛЕКСАНДРОВИЧ, СЕМАШКО АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: выражений, вычисления, логических, переменных

Опубликовано: 30.09.1982

Код ссылки

<a href="https://patents.su/4-962918-ustrojjstvo-dlya-vychisleniya-logicheskikh-vyrazhenijj-peremennykh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления логических выражений переменных</a>

Предыдущий патент: Универсальный логический модуль

Следующий патент: Устройство для сравнения чисел

Случайный патент: Ленточный вакуум -фильтр