Устройство для вычисления непрерывно-логических функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1695289

Автор: Шимбирев

Текст

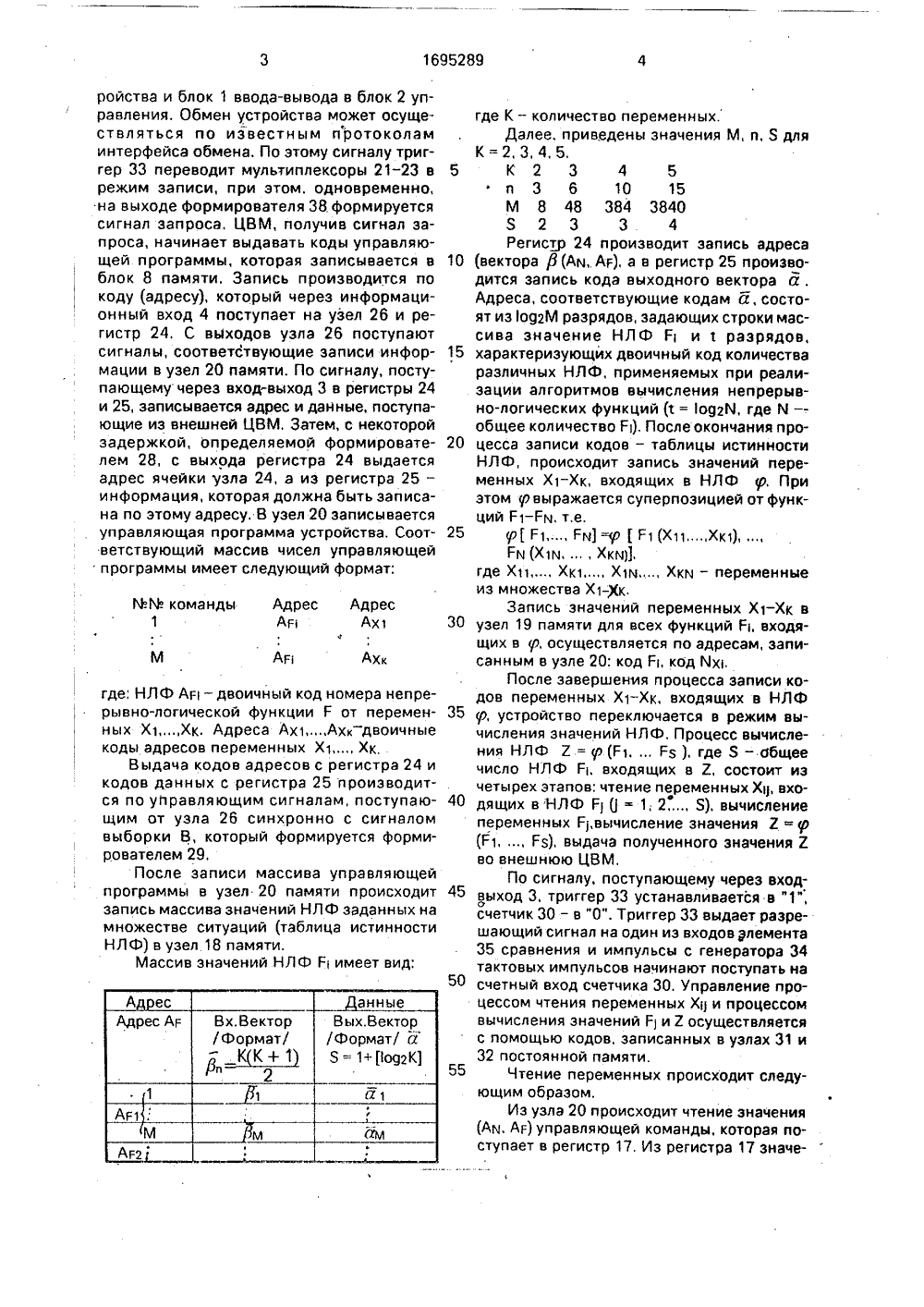

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 16 9 0 06 Е 7/О ОПИ ИЕ ИЗОБРЕТЕНИ ЛЬСТВУ АВТОРСКОМУ СВ тут ав-,ом ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР(56) Авторское свидетельство СССМ 941994, кл, 0 06 Г 7/00, 1981.Авторское свидетельство СССМ 1256010, кл. 6 06 Г 7/00, 1985,Изобретение относится к вычислительной технике и моделирующим системам и предназначено для использования в вычислительных структурах, ориентированных на реализацию непрерывно-логических, расплывчатых и гибридных формул,Цель изобретения - повышение быстродействия и расширение функциональных возможностей устройства за счет вычисления функций гибридной логики, которые могут быть разрывными.На фиг. 1 приведена схема устройства; , на фиг. 2 - схема блока вычисления порогового оператора; на фиг. 3 х то же, блока буферной памяти; на фиг, 4 - то же, блока ввода-вывода; на фиг. 5 - то же, блока управления.Устройство содержит блок 1 ввода-вывода, блок 2 управления, управляющий вход-выход 3 устройства, информационный вход 4 устройства, информационный вход- выход 5 устройства, блок 6 вычисления порогового оператора, коммутатор 7, блок 8 буферной памяти. 54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НЕПРЕ Р Ы В НО-ЛОГИЧ ЕСКИХ ФУНКЦИЙ (57) Изобретение относится к вычислительной технике и моделирующим системам. Цель мзобретения - увеличение быстродействия и расширение функциональных возможностей за счет вычисления функций гибридной логики, которые могут быть разрывными. Поставленная цель достигается тем, что устройство содержит блок 1 ввода- вывода, блок 2 управления, блок 6 вычисления порогового оператора, коммутатор 7 и блок 8 памяти. 1 з,п.ф-лы, 5 ил. Блок 6 вычисления порогового оператора содержит дешифратор 9, К регистров 10, первую группу иэ К элементов 11 сравнения, К коммутаторов 12, вторую группу из К элементов 13 сравнения и регистр 14.Блок 8 буферной памяти содержит с первого по третий регистры 15 - 17, с первого по третий узлы 18-20 памяти, с первого по третий мультиплексоры 21 - 23.Блок 1 авода-вывода содержит регистр 24 адреса, первый регистр 25 данных, узел 26 постоянной памяти, второй регистр 27 данных, первый и второй формирователи 28 и 29.Блок 2 управления содержит счетчик 30, первый узел 31 постоянной памяти, второй узел 32 постоянной памяти, триггер 33, генератор 34 тактовых импульсов, элемент 35 сравнения, с первого по третий формирователи 36 - 38.Устройство работает следующим обра- зом. та начинается по сигналу, подавае ез управляющий вход-выход 3 устройства и блок 1 ввода-вывода в блок 2 управления, Обмен устройства может осуществляться по известным протоколам интерфейса обмена, По этому сигналу триггер 33 переводит мультиплексоры 21 - 23 в режим записи, при этом. одновременно, на выходе формирователя 38. формируется сигнал запроса, ЦВМ, получив сигнал запроса, начинает выдавать коды управляющей программы, которая записывается в блок 8 памяти. Запись производится по коду (адресу), который через информационный вход 4 поступает на узел 26 и регистр 24, С выходов узла 26 поступают сигналы, соответствующие записи информации в узел 20 памяти. По сигналу, поступающему через вход-выход 3 в регистры 24 и 25, записывается адрес и данные, поступающие из внешней ЦВМ. Затем, с некоторой задержкой, определяемой формирователем 28, с выхода регистра 24 выдается адрес ячейки узла 24, а из регистра 25 - информация, которая должна быть записана по этому адресу, В узел 20 записывается управляющая программа устройства, Соответствующий массив чисел управляющей программы имеет следующий формат: Адрес АдресАв Ах 1 ММ команды 1 Ахк Аг где; НЛФ Ар - двоичный код номера непре рывно-логической функции Е от переменных Х 1 Хк. Адреса Ах 1Ах-двоичныекоды адресов переменных Х 1 Хк,Выдача кодов адресов с регистра 24 икодов данных с регистра 25 производится по управляющим сигналам, поступающим от узла 26 синхронно с сигналомвыборки В, который формируется формирователем 29,После записи массива управляющейпрограммы в узел 20 памяти происходитзапись массива значений НЛФ заданных намножестве ситуаций (таблица истинностиНЛФ) в узел 18 памяти.Массив значений НЛФ Е имеет вид;40 45 50 55 5 10152025 30 35 где К - количество переменных.Далее, приведены значения М, и, Я для К = 2, 3, 4, 5,К 2 3 4 5и 3 6 10 15М 8 48 384 38408 2 3 3 4Регистр 24 производит запись адреса (вектора ф(Аи, Ас), а в регистр 25 производится запись кода выходного вектора а . Адреса, соответствующие кодам а, состоят иэоцгМ разрядов, задающих строки массива значение НЛФ Е 1 и 1 разрядов,характеризующих двоичный код количестваразличных НЛФ, применяемых при реализации алгоритмов вычисления непрерывно-логических функций (т =од 2 Й, где й общее количество Е). После окончания процесса записи кодов - таблицы истинности НЛФ, происходит запись значений переменных Х 1-Хк, входящих в НЛФ р. При этом р выражается суперпозицией от функций Е 1 - Еи, т,е.рЕ 1,., Еи) =рЕ 1(Х 11,Хк 1),Еч (Х 1 Хкч 1)где Х 1 Хк 1, Х 1 м Хкм - переменные из множества Х 1-)Ь.Запись значений переменных Х 1-Хк в узел 19 памяти для всех функций Еь входящих в р. осуществляется по адресам, записанным в узле 20: код Еь код йхьПосле завершения процесса записи кодов переменных Х 1-Хк, входящих в НЛФ р, устройство переключается в режим вычисления значений НЛФ. Процесс вычисления НЛФ 2 = р(Е 1, , Еэ ), где 5 - ббщее число НЛФ Еь входящих в 2, состоит из четырех этапов; чтение переменных Хц, входящих в НЛФ Е О - 1, 2, Я). вычисление переменных Е 1,вычисление значения 2 = О (Е 1, , Еэ), выдача полученного значения 2 во внешнюю ЦВМ,По сигналу, поступающему через вход- выход 3, триггер 33 устанавливается в "1", счетчик 30 - в "0". Триггер 33 выдает разрешающий сигнал на один из входов элемента 35 сравнения и импульсы с генератора 34 тактовых импульсов начинают поступать на счетный вход счетчика 30. Управление процессом чтения переменных Хя и процессом вычисления значений Е и 2 осуществляется с помощью кодов. записанных в узлах 31 и 32 постоянной памяти.Чтение перющим образомИз узла 20(Ам, Ае) управлступает в регис еменных происходит следупроисходит чтение значения яющей команды, которая потр 17. Из регистра 17 значе 1695289мационному входу-выходу и к первому управляющему входу-выходу блока ввода- вывода, первый выход блока ввода-вывода и первый выход коммутатора подключены соответственно к информационным входам блошка буферной памяти, первый выход которого подключен к первому управляющему входу коммутатора, второй выход блока ввода-вывода, второй выход коммутатора, первый выход блока управления,ние Аи поступает в блок 6, а значение Ар - на соответствующий вход коммутатора 7, Чтение значения Хл происходит по адресу Ан, поступающему с выхода регистра 17 на адресный вход узла 19, Затем происходит запись Хц из узла 19 в регистр 16, а затем перезапись этого числа из регистра 16 в соответствующий регистр 10, выбранный дешифратором 9. Процесс чтения переменных Х 1, осуществляется последовательно для всех переменных Х 1, 1= 1. 2 К 1, где К - число переменных, входящих в Е 1.После считывания всех значений Их из узла 19 соответствующих функции Е начинается вычисление НЛФ Еь Это происходит в блоке 6. Процесс гибридного непрерывно- логического преобразователя Е (Х 1Хк) осуществляется на элементах 11 сравнения и коммутаторах 12, которые формируют код переменйых Х 1, .Хк, а затем, на элементах 13 сравнения происходит определение кода двоичного вектора ф ВекторВ поступает на адресный вход узла 18 памяти, туда же поступает код функции Е через коммутатор 7 Для этого узел 31 постоянной памяти выдает сигнал чтения Е на адресный вход Аг узла 18, с которого происходит чтение строки таблицы истинности, которая соответствует данной ситуации расположения переменных Х 1 - Хк.Я - разрядный код а, считанный с узла 18, поступает на входы регистра 15. Этот. код является адресом а для выбора требуемой переменной Х 1. Выбранная переменная, которая является результатом вычисления НЛФ Е (Х - Хк) - хь поступает в узел 19. Далее осуществляется последовательное вычисление Е 1, Е 2,., Еи, входящих в у(Е 1, Ед), и все результаты вычислений записываются в узел 19. Затем происходит вычисление самой функции р, где значения Е 1 рассматриваются уже как переменные. Результат вычислений записывается в регистр 27,Формула изобретения 1. Устройство для вычисления непрерывно-логических функций, содержащее коммутатор, блок буферной памяти и блок управления, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия и расширения функциональных возможностей устройства путем вычисления функций гибридной логики, которые могут быть разрывными, оно содержит блок ввода - вывода и блок вычислений порогового оператора, причем информационный вход, информационный и управляющие входы-выходы устройства подключены соответственно к первому информационному входу, к инфор 510 входу дешифратора, вход синхронизации блока - к входу синхронизации дешифрато.ра и к входу записи - считывания регистра, 50 выходы с первого по К-й которого подключе,ны соответственно к входам записи-считывания регистров с первого по К-й, прямой выход с-го регистра(где с = 1 К) подключен к первому входу с-го элемента сравнения первой группы и к первому 55 информационному входу с-го коммутатора,. инверсный выход с-го регистра подключен к второму входу с-го элемента сравнения второй группы и к второму информационному входу с-го коммутатора, второй инвыход блока вычисления порогового оператора и второй выход блока буферной памяти подключены соответственно кадресным входам блока буферной памяти,15 третий выход которого подключен к второму управляющему входу коммутатора и кпервому информационному входу блокавычисления порогового оператора, второйы выход блока управления и третий выход20 блока ввода-вывода подключены соответственно к управляющим входам блока буферной памяти, четвертый выход которогоподключен к второму информационномувходу блока вычисления порогового опера 25 тора и к второму информационному входублока ввода-вывода, второй управляющийвход-выход которого подключен к входувыходу режима блока управления, третийи четвертый выходы которого подключены30 соответственно к входам синхронизациикоммутатора и блока вычисления порогового оператора, выходы с первого по К-йгруппы (где К - число аргументов непрерывно-логической функции) блока вычисления35 порогового оператора подключены соответственно к информационным входам с первого по К-й коммутатора,2.Устройство по п.1,отл ича ю щеес я тем, что блок вычисления порогового.40 оператора содержит дешифратор, группу изК регистров, первую группу иэ К элементовК К - 1сравнения, вторую группу из2элементов сравнения, К коммутаторов и ре 45 гистр, причем первый информационныйвход блока подключен кинформационномуформационный вход блока подключен к информационным входам регистров с первого по К-й, выходы а-го и в-го коммутаторов (где а, Ь = 1,., К и а = Ь) подключены соответственно к первому и второму входам 1-го элемента сравнения второй группыК К - 1(где = 1,., ) и соответственно к а-му и Ь-му выходам группы блока, выходы элементов сравнения с первого по К-й первой группы подключены соответственно куправляющим входам коммутаторов с первого по К-й и соответственно к информационным входам первой группы регистра,5 выходы элементов сравнения с первого поК К - 1-й второй группы подключены соот 2ветственно к информационным входам второй группы регистра, выход которого10 подключен к выходу блока,Т Производственно-и акаэ 4162 ВНИИПИ Госуда венного113035,Подписноемитета по изобретениям и открытиям при ГКНТ СССсква, Ж, Раушская наб 4/5 ский комбинат "Патент", г, Ужгород, ул.Гагарина, 10

СмотретьЗаявка

4655006, 24.02.1989

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ АВТОМАТИЧЕСКИХ СИСТЕМ

ШИМБИРЕВ ПАВЕЛ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: вычисления, непрерывно-логических, функций

Опубликовано: 30.11.1991

Код ссылки

<a href="https://patents.su/8-1695289-ustrojjstvo-dlya-vychisleniya-nepreryvno-logicheskikh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления непрерывно-логических функций</a>

Предыдущий патент: Устройство для отображения и редактирования информации на экране электронно-лучевой трубки

Следующий патент: Устройство для сортировки данных

Случайный патент: Устройство для выделения и отрезания нервов